The Cortex-M architecture uses a vector table lookup mechanism. When an exception occurs, the core automatically looks up the entry address of the handler from the vector table. The vector table is essentially an array of WORDs (32-bit integers), where each index corresponds to a specific exception, and the value of that index is the entry address of the exception handler.

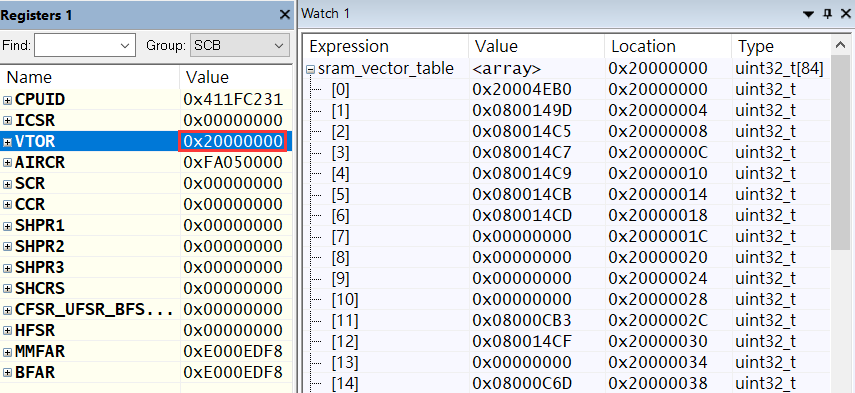

The position of the vector table in the address space can be set using the VTOR register in the SCB. After reset, the value of this register is 0. Therefore, a vector table must be present at address 0 for initial exception allocation. However, after the system is running, we can relocate the vector table to another address by modifying the VTOR register, which can be in the Flash area or the RAM area. It is important to note the requirements for the starting address of the vector table: first, determine the total number of vectors in the system, then round this number up to the next power of 2, and the starting address must be aligned to the boundary of this value. For example, if there are 68 interrupts, the total number of vectors is 68 + 16 (system exceptions) = 84, which rounds up to 128, so the address must be divisible by 128 * 4 = 512.

This article takes the IAR EWARM development environment as an example to relocate the vector table of STM32F107 to the starting address of SRAM. EWARM requires the default vector table to be named “__vector_table” so that its debugging system can correctly identify the vector table, which is placed at address zero in Flash.

Then, define a vector table in SRAM, which can be named arbitrarily; here it is named “sram_vector_table”. After system initialization, copy the contents of __vector_table to sram_vector_table to construct the new vector table. To control the storage location of the vector table, use the #pragma preprocessor directive to place the vector table in a custom section named “.vector”. The “__root” keyword forces the compiler to retain the vector table without any optimization.

#define VECTOR_LEN 84UL

#pragma location = “.vector”

__root uint32_t

sram_vector_table[VECTOR_LEN]; /* Vector table in SRAM */

Then, in the IAR linker script (icf file), control the storage location of .vector, placing it at the starting position of SRAM:

place at start of RAM_region { section .vector };

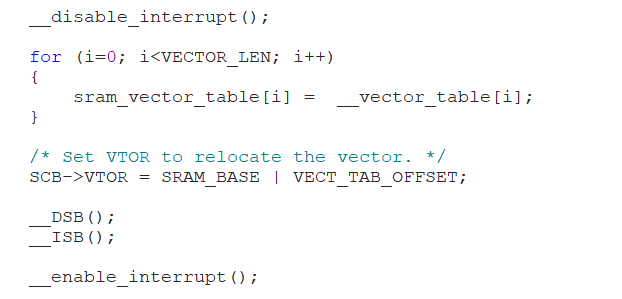

Construct sram_vector_table at an appropriate position in the code:

When relocating the vector table, global interrupts should be disabled first to avoid unexpected situations caused by interrupts during the process. SRAM_BASE is the starting address of RAM (0x20000000), and VECT_TAB_OFFSET is 0.

After resetting the VTOR, global interrupts are enabled again, and the interrupt vector table relocation is complete.

Product Consultation:

Beijing: 010-62975900

Shanghai: 021-62127690

Shenzhen: 0755-82977971

Share, Read, and Like, at least I want to have one