Source: EETOP

Original Author: electronicdesign

-

The pain points of the existing chip layout (floorplan) design process. -

How artificial intelligence can optimize this process, reducing the time required from weeks to hours. -

Potential applications of extending the same method to improve different hardware design processes.

Artificial intelligence (AI) has transformed many markets, including manufacturing, pharmaceuticals, and aerospace, but hardware systems are the areas that have yet to see significant investment or innovation in AI.

While there are many potential machine learning (ML) applications throughout the end-to-end lifecycle of system-on-chip (SoC) production, this article focuses on the layout planning phase of SoC design. Undoubtedly, this is one of the most time-consuming, costly, and resource-intensive processes. Specifically, we will explore the evaluation of using ML and optimization models to exponentially reduce investment during this SoC phase.

floorplan

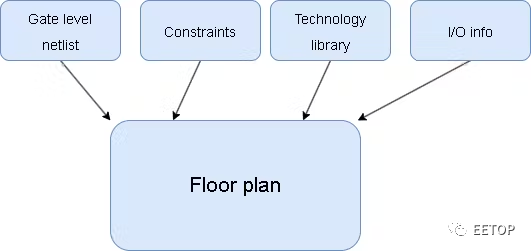

Semiconductor chips consist of billions of transistors. The floorplan involves placing these transistors along with other necessary components (such as clocks, power rails, etc.) on the chip. Their positions are optimized to achieve smaller chip sizes, better performance, avoidance of timing conflicts, and easier routing. This critical step in the design flow requires gate-level netlists, constraints, technology libraries, timing libraries, I/O information, etc., as shown in Figure 1.

1. The floorplan planning requires different inputs.

However, floorplan design typically takes several weeks to complete. Machine learning can perform the same task in a matter of hours. This helps bring semiconductor chips to market faster and allows engineers to focus on more complex tasks.

Machine Learning

Machine learning is a type of artificial intelligence that learns various patterns and insights from data and applies this learning to make accurate and insightful predictions. Various steps are required in the ML process to optimize the floorplan.

Data Collection

The inputs required for the floorplan, such as gate-level netlists, constraints, technology libraries, and I/O information, are collected from silicon-validated chips.

Data Preprocessing

Once the data is collected, the steps to train the ML model are initiated. The first step is to obtain the data in the correct format to train the model, known as data preprocessing. It includes several stages such as data filtering, data quality checks, data transformation, normalization, and standardization.

Model Training

Once the data is prepared, the next step is to train the ML model. The goal is to predict the placement of the next component on the chip while optimizing for minimal power consumption, performance, and area (PPA). Reinforcement learning can be used to achieve this. It employs an iterative approach and rewards placements that lead to the lowest PPA while penalizing suggestions that increase PPA.

Model Testing and Deployment

After training the model, the next step is to test the model’s performance on unseen chip blocks to validate the effectiveness of its predictions. If the results validated by the engineers are satisfactory, deployment can proceed. Predictions for chip block placements made through these steps will be more effective and faster than traditional methods.

Additional Optimization of Block Placement

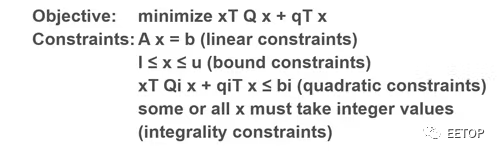

The process can stop at the previous stage. However, further optimization of the entire chip block placement can be achieved using mixed-integer programming (MIP) optimization techniques. This algorithm aims to further minimize PPA based on the optimized floorplan generated by the ML model, under specified design constraints defined in the data section.

The advantage of using MIP is the ability to generate optimized solutions for different scenarios. This is very helpful when scaling the process to accelerate design speed. The step-by-step approach of the entire process is illustrated in Figure 2.

2. The machine learning process involves steps to predict and optimize floorplan design.

Algorithms

Reinforcement Learning

Reinforcement learning is a type of ML that involves taking actions and learning through trial and error. This is achieved by rewarding behaviors that lead to the desired outcomes and penalizing unwanted behaviors.

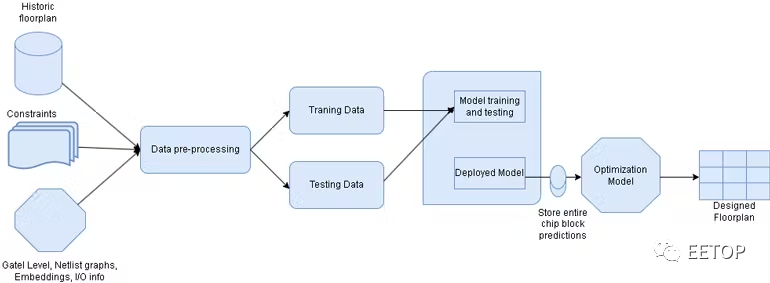

Although there are many types of reinforcement learning algorithms, a commonly used method is called Q-learning (defined by the equation in Figure 3). This occurs when the agent does not receive any policy (a reinforcement learning policy is a mapping of the probability distribution of actions to take based on observations of the current environment), leading to self-guided exploration of the environment.

3. This is the equation for Q-learning, which is a reinforcement learning algorithm.

MIP Optimization

Mixed-integer programming is an optimization technique used to solve large and complex problems. It can be used to minimize or maximize objectives within defined constraints.

Examples of MIP objectives and constraints definitions:

The Value of Optimization

Using optimization techniques to overcome process bottlenecks to create efficient systems is not a new concept. It has been successfully applied across various industries for decades, with its revolutionary impact particularly evident in supply chain management, which has a market size of hundreds of billions of dollars.

Using AI to optimize supply chain management ensures efficient manufacturing, distribution, and inventory placement systems in the supply chain at the lowest costs. This became very evident during the COVID-19 pandemic when supply chains were severely disrupted. Companies that adopted supply chain optimization not only avoided significant impacts from the pandemic but many even thrived during it. Meanwhile, companies that failed to do so suffered billions in losses and have yet to recover.

Stay Vigilant

Artificial intelligence is indeed powerful, but its predictions should not be accepted blindly and must be verified by human engineers. Feedback should be provided to ML models that output layouts that do not meet constraints or are suboptimal. However, with consistent feedback, the model will indeed self-improve. The hardware industry should also consider the initial overhead.

Conclusion

There are many other practical applications of utilizing artificial intelligence (machine learning, deep learning, etc.) to integrate, analyze, simulate, deploy, and launch effective solutions throughout the hardware lifecycle, with the potential for billions of impacts. This article merely scratches the surface by looking at one of these applications.

Similar to the software technology industry, leaders in the hardware technology industry should also work together to unleash the full potential of artificial intelligence in this field.

Does not represent the position of the Institute of Semiconductors, Chinese Academy of Sciences