This article is based on the Creative Commons text sharing agreement: https://creativecommons.org/licenses/by-sa/4.0/

In the automotive industry, reducing development costs is crucial. The development of electrical hardware is an expensive and time-consuming process involving many stages (e.g., prototyping, electrical testing, mechanical testing, lifecycle testing). There is an increasing demand for virtualization to improve the cost-effectiveness of embedded software development and testing stages. With this approach, fewer prototypes need to be manufactured, as simulation can more quickly and effectively identify most potential faults without constructing hardware prototypes. Renode is an open-source embedded system simulation framework that aids in software-based testing. The main goal of this article is to explore the usability of this framework in automotive applications.

(Translator’s Note: Renode uses the QEMU processor model, and we have reference content about QEMU on our video channel and public account; we also undertake virtualization custom development based on Renode and QEMU, welcome to contact us.)

Keywords: Embedded System Simulation; MCU Microcontroller Virtualization; Software-in-the-Loop SIL

1. Introduction

The electronic control units installed in new cars typically need to run some embedded software to ensure the controllers operate correctly. The development time for these controllers is long, and repetitive prototyping and testing increase costs.

In addition to embedded software development, developing the necessary hardware is also important. However, this task requires constant prototyping and redesign based on test results, necessitating multiple iterations. It is also time-consuming and costly. The goal of simulating hardware and software together is to verify whether the hardware and software can work properly. This task is traditionally performed after the prototype hardware is completed, but if this verification can be done in a virtual environment, it can reduce the costs of prototyping and any iterations, as well as the time required for development.

Electronic control units (ECUs) in automotive electronic systems may experience functional failures due to interference between the analog signals generated on the circuit and the binary signals used within the microprocessor of the control unit [1]. Currently, the industry tests the functionality of such failures through experiments, which is time-consuming and may occur late in the development stage (when a physical prototype is available), and correcting and retesting is very time-consuming. Due to hardware supply difficulties, development is often delayed, and debugging on real hardware is also challenging. For all these reasons, testing the functional robustness of automotive electronic systems is costly and time-consuming [2].

Therefore, the automotive industry is very eager for an industrially applicable virtual robustness testing method that can test the functional robustness of automotive electronic systems through computer simulation [3,4,5,6].

There is a need for a software toolbox that allows for virtual functional testing of automotive electronic system control units. The goal is to study a simulation method suitable for virtual functional testing of electronic components [7]. This can be important in all areas:

-

Early screening of design errors;

-

Shortening development time;

-

Improving test coverage and efficiency;

-

Significantly reducing testing costs;

-

Minimizing the use of hardware elements.

This solution can be used in any electronic system design process that requires functional testing of control units, joint simulation of analog and digital circuits, or robust design and operation. Unfortunately, there is a lack of information in scientific literature about applicable software solutions. Most available tools provided by teams like Synopsys and Cadence focus on semiconductor design and instruction set verification. Other simulators, such as LabCenter Proteus and DesignSoft TINA, are not open-source and are difficult to extend their microcontroller models [8,9]. Hence, the aim of this study is to explore whether it is possible to apply Renode to handle the virtualization of the electrical development toolchain.

(Translator’s Note: Simulators provided by Synopsys, MachineWare, etc., are chip-level, while simulators like Proteus and TINA focus on PCB-level. We undertake custom development services for chip-level and PCB-level virtualization, welcome to contact us for more information.)

2. What is Renode?

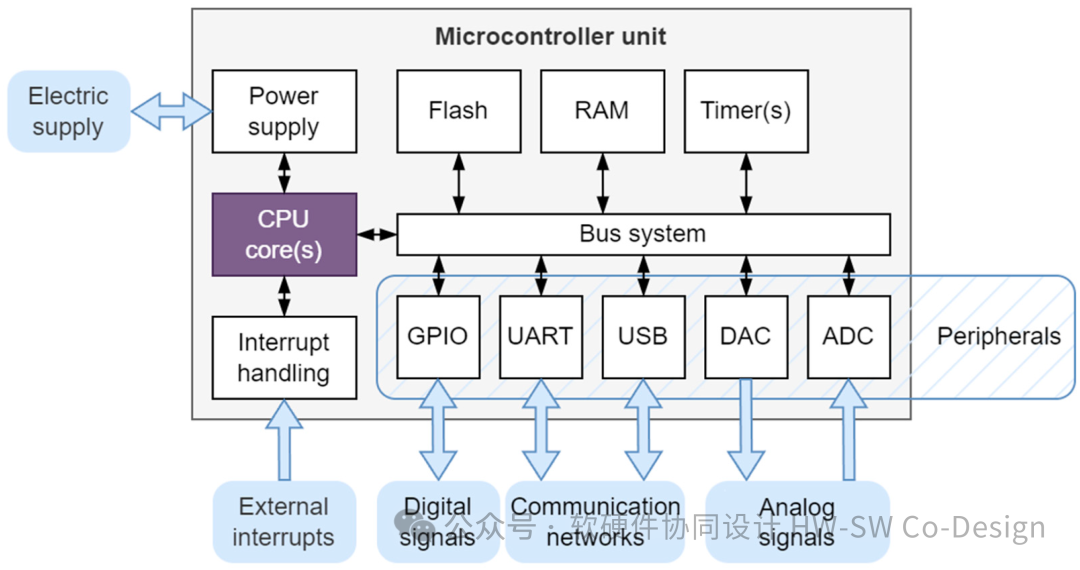

Renode is an open-source simulator software solution for embedded platforms. It is an instruction set simulator that supports various out-of-the-box architectures such as x86 (Intel Quark), ARM Cortex-A, Cortex-M, SPARC, and RISC-V, and due to its open-source nature, it can be further extended. It can be used to assemble virtual systems on chips from building blocks, such as various types of microcontrollers (e.g., Cortex-M, Cortex-A) and different peripheral models (Figure 1). Therefore, it can also simulate microcontrollers used for automotive control. Unmodified production firmware can run against the simulated cores, peripherals, and even configured sensors and actuators. The parameters of the simulated embedded systems (e.g., memory addresses, peripherals, etc.) are defined in text-based configuration files, while functionalities are modeled in C#.

Figure 1. Microcontroller and connected peripherals.

Figure 1. Microcontroller and connected peripherals.

Using Renode, rapid software development and debugging capabilities can be achieved without hardware evaluation, just like in standard IDE design processes. Most integrated development environments can be used, with the only requirement being the ability to connect to a GDB server for debugging.

(Translator’s Note: Achieving rapid software development and debugging capabilities without hardware evaluation is the overall goal of the global virtual prototyping industry.)

3. Renode System as a Virtual Platform

The platforms in Renode model the system bus of the machine (designated as sysbus) as the central building block connecting peripherals. All peripherals can be accessed from anywhere in the created platform.

Real hardware may use various intricate connection buses, but the same platform in Renode uses only a single bus. This simplification typically does not affect the simulated behavior in any way, as the interconnection structure in the SoC is hidden from a software perspective.

There are necessary configuration files to define the simulated MCU and development board. Using these text-based configuration files, the environment can be automatically initialized.

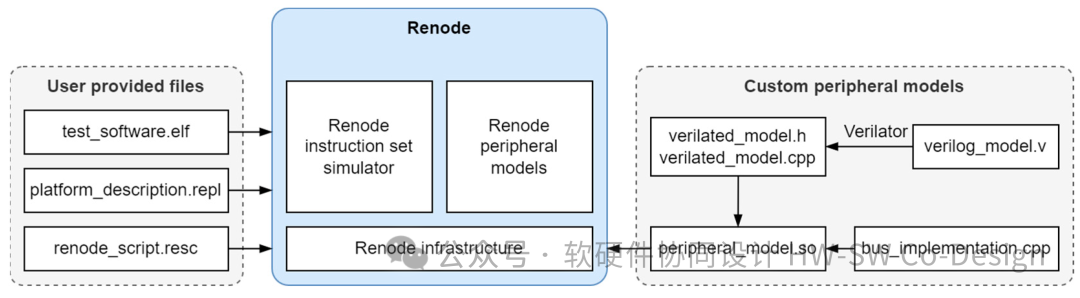

Renode simulation typically involves several key files that work together to define and execute the simulation environment in Renode. The files usually involved are shown in Figure 2.

Figure 2. Files typically involved in Renode simulation.

Figure 2. Files typically involved in Renode simulation.

The Renode script files (with the .resc extension) contain commands required to create the virtual machine, load the board files, and perform other logging. This allows automation of command line operations. The Renode platform definition files (with the .repl extension) include descriptions of the MCU (e.g., CPU and peripherals) and the board. This script loads the configurations for processor descriptions and the connections of system hardware (e.g., GPIO connected to LED). Renode is also capable of loading custom peripheral models developed in Verilog or C++ [10].

4. Implementation of STM32F4 Discovery Board

The STM32F4 series is a range of 32-bit microcontrollers developed by STMicroelectronics. These microcontrollers are based on high-performance ARM Cortex-M cores with rich peripherals. The STM32F4 Discovery board is a popular development board that leverages the capabilities of the STM32F407 microcontroller (embedded debugging tools, digital accelerometer, LEDs, buttons). The board is designed to help users easily develop and test applications, especially those involving audio processing.

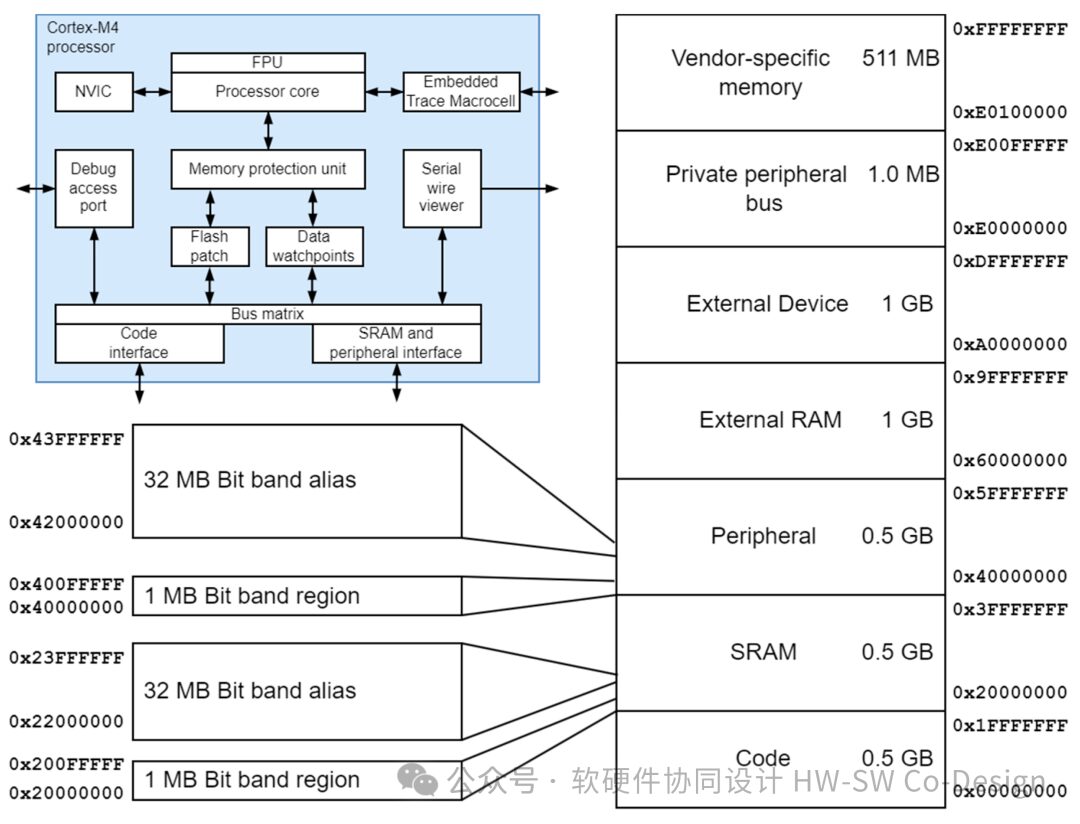

This article uses the STM32F4 Discovery board simulation to test the simulation setup using Renode. Figure 3 shows the memory address space of the Cortex-M4 CPU, and the parameters of the configuration file are the same as below [11].

Figure 3. Block diagram of the Cortex-M4 CPU (top left) and memory address space.

Figure 3. Block diagram of the Cortex-M4 CPU (top left) and memory address space.

In Renode, after creating the virtual machine, it only contains one peripheral, which is the system bus, referred to as sysbus. At this point, there is no CPU or memory, so the machine is not ready to execute any code. Renode uses a text-based format to describe the platform.

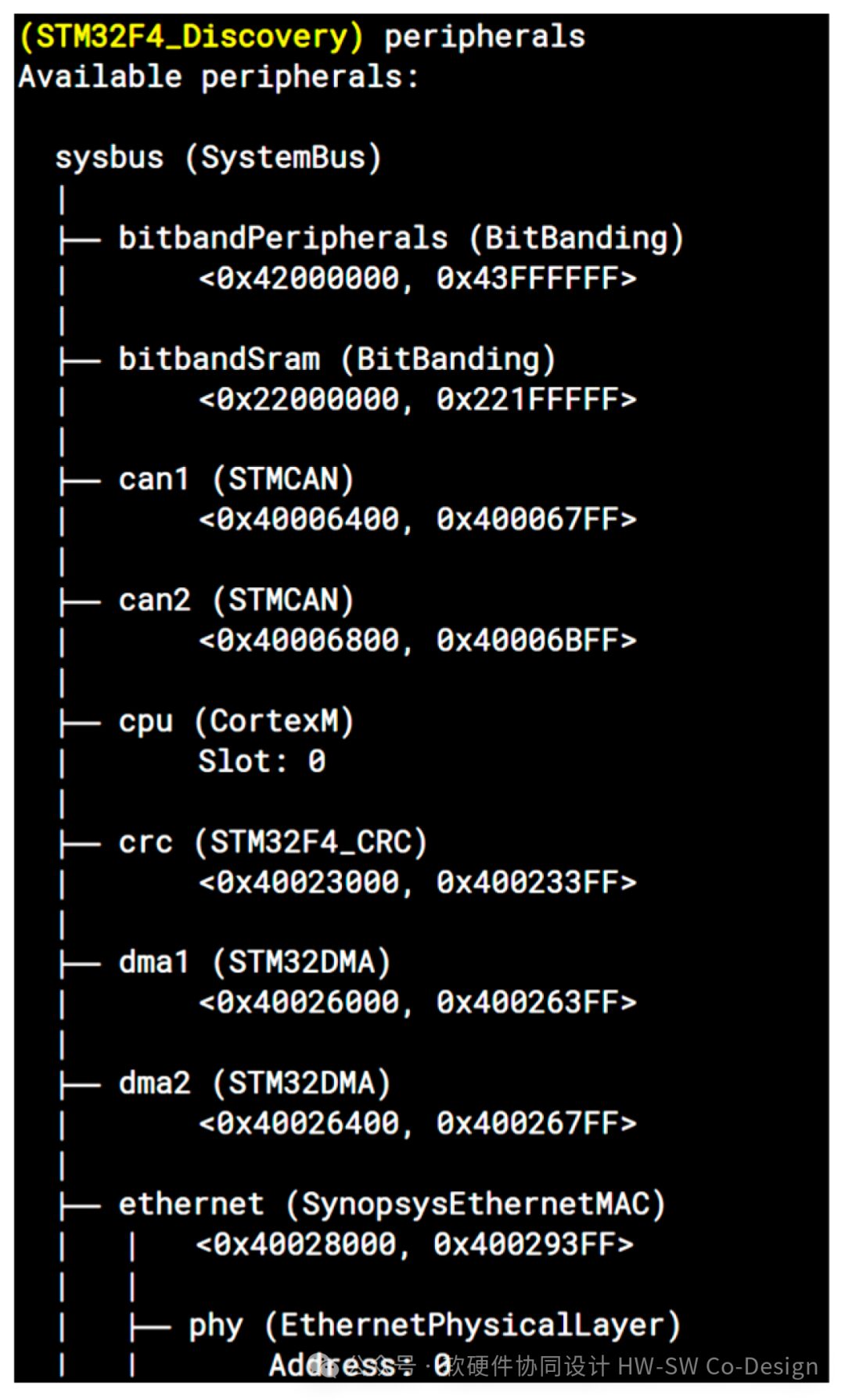

After loading the necessary board files using predefined platform definitions (platform description files) in the Renode terminal window, all peripherals are configured, and the virtual machine is ready for use. All configured peripherals can be listed, and binary files can be loaded for testing and debugging against the simulation (Figure 4).

Figure 4. Peripherals defined for STM32F4 in the Renode terminal window.

Figure 4. Peripherals defined for STM32F4 in the Renode terminal window.

5. Debugging

Virtual debugging is the most crucial function necessary for handling ECU development virtualization. The virtual machine can be used to debug binary code using the GDB remote protocol. General GDB functions (such as breakpoints, stepping, memory access) can be used to inspect the binary code against the virtual hardware while it is running. There is a significant time difference between debugging on real hardware and virtual debugging; the debugging process is transparent for the simulated machine because virtual time does not increase when the simulated CPU stops.

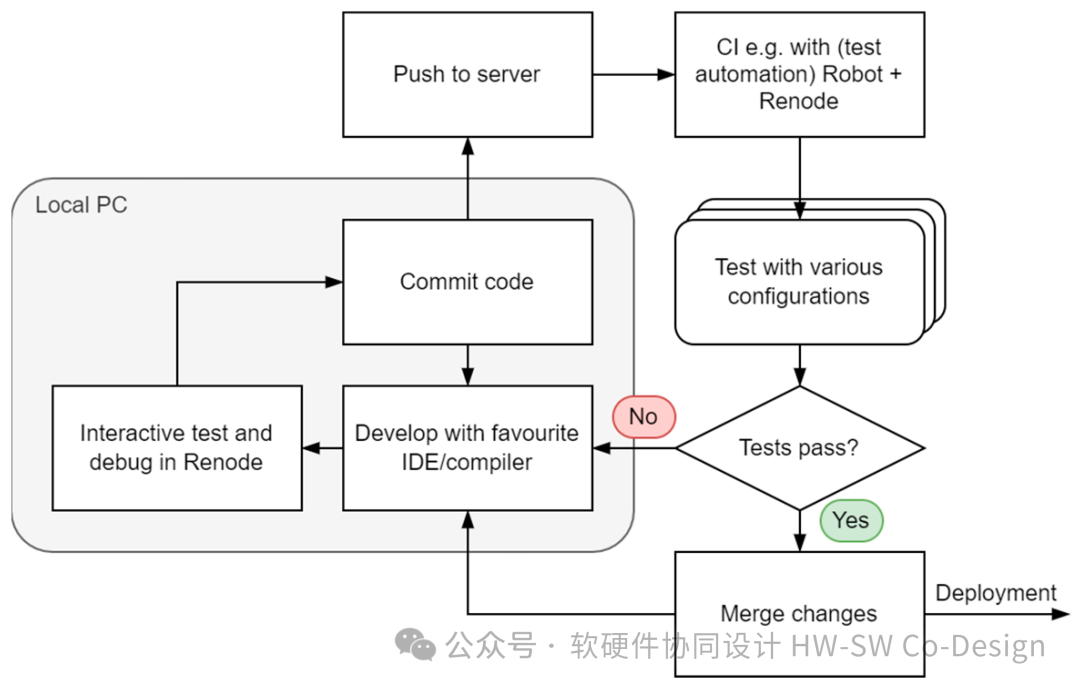

Due to the deterministic time flow, the process is simpler; the debugging process can stop the entire system simultaneously. It is very suitable to be part of automated testing scenarios, such as running in the background on CI servers. Renode integrates with the Robot Framework test suite, allowing it to be used with other test automation environments and providing user-friendly scripts for running tests (Figure 5).

Figure 5. The process of development and testing using Renode.

Figure 5. The process of development and testing using Renode.

Assuming the executed binary file (the compiled .elf file) contains a symbol mapping (which is usually the case during development), it can track its execution, obtain detailed logs (including function names executed, peripheral access, and opcode counts), generate code coverage reports, and utilize advanced GDB integration. Renode also comes with a built-in disassembler and metrics analyzer that can simulate device elements using labels, integrate with external analyzers like Wireshark, and allow the use of hooks to monitor or change the execution of the binary file, such as triggering software behavior by spoofing register/memory states or injecting messages (network, CAN, etc.).

6. Conclusion

Today, there are many control units in new cars that operate switches and actuators based on sensor data. The volume of data flowing between these units is increasing, and the manner is becoming more complex. Therefore, development and testing programs are also becoming more complex.

With Renode, virtual test cases can be created where corresponding tests can be assigned to virtual nodes connected through known communication channels (e.g., Ethernet, CAN, wifi, etc.). This makes prototype testing more flexible and accelerates the entire testing process. The benefits of simulation are apparent, as the complexity of automotive systems continues to increase, especially for new hardware components, which must determine whether new hardware components can fit into specific projects.

Renode is a framework that supports automotive development, as it possesses testing integration capabilities, an increasing hardware coverage (supporting different instruction set architectures), and the possibility of automation. Further research should relate to SPICE-based circuit simulation.

(Translator’s Note: This project is a research project of European universities, funded by the European Union. If your company needs to carry out similar explorations, please feel free to contact us for more information; we provide virtual prototyping engineering implementation services based on commercial and open-source tools.)

Author Contributions

Conceptualization, F.S., D.F., and I.S.; methodology, I.S. and F.S.; validation, F.S.; investigation, I.S.; resources, I.S. and F.S.; writing—original draft preparation, F.S. and I.S.; writing—review and editing, F.S., D.F., and I.S. All authors have read and agreed to the published version of the manuscript.

Funding

This research was funded by the European Union under the framework of the National Autonomous Systems Laboratory (RRF-2.3.1-21-2022-00002).

Institutional Review Board Statement

Not applicable.

Informed Consent Statement

Not applicable.

Data Availability Statement

Original data supporting the conclusions of this article will be made available by the authors upon request.

Conflicts of Interest

The authors declare no conflict of interest.

References

-

Urbina, M.; Ahmadian, H.; Obermaisser, R. Co-simulation framework for AUTOSAR multi-core processors with message-based Network-on-Chips. In Proceedings of the 2016 IEEE 14th International Conference on Industrial Informatics (INDIN), Poitiers, France, 19–21 July 2016; pp. 1140–1147. [Google Scholar] -

Hseih, H.; Lavagno, L.; Passerone, C.; Sansoe, C.; Sangiovanni-Vincentelli, A. Modeling micro-controller peripherals for high-level co-simulation and synthesis. In Proceedings of the 5th International Workshop on Hardware/Software Co Design. Codes/CASHE’97, Braunschweig, Germany, 24–26 March 1997; pp. 127–130. [Google Scholar] [CrossRef] -

Gauthier, L.; Jerraya, A. Cycle-true simulation of the ST10 microcontroller. In Proceedings of the Design, Automation and Test in Europe Conference and Exhibition 2000 (Cat. No. PR00537), Paris, France, 27–30 March 2000; p. 742. [Google Scholar] [CrossRef] -

Gauthier, L.; Jerraya, A. Cycle-true simulation of the ST10 microcontroller including the core and the peripherals. In Proceedings of the 11th International Workshop on Rapid System Prototyping. RSP 2000. Shortening the Path from Specification to Prototype (Cat. No.PR00668), Paris, France, 21–23 June 2000; pp. 60–65. [Google Scholar] [CrossRef] -

Stecklina, O.; Vater, F.; Basmer, T.; Bergmann, E.; Menzel, H. Hybrid Simulation Environment for rapid MSP430 system design test and validation using MSPsim and SystemC. In Proceedings of the 14th IEEE International Symposium on Design and Diagnostics of Electronic Circuits and Systems, Cottbus, Germany, 13–15 April 2011; pp. 167–170. [Google Scholar] [CrossRef] -

Köhler, C. Enhancing Embedded Systems Simulation: A Chip-Hardware-in-the-Loop Simulation Framework; Vieweg+ Teubner Verlag: Wiesbaden, Germany, 2011. [Google Scholar] [CrossRef] -

Amringer, N.; Asemann, P. Simulation of Virtual ECUs in the context of ECU Consolidation. In Proceedings of the 9th AutoTest Technical Conference, Test of Hardware and Software in Automotive Development, Stuttgart, Germany, 19–20 October 2022. [Google Scholar] [CrossRef] -

Janabi, A.; Agyeman, M. An Overview of Cycle-Accurate, Event-Driven and Full Systems Simulators for Chip-Multiprocessors. Int. J. Comput. Theory Eng. 2019, 11, 103–106. [Google Scholar] [CrossRef] -

Paknikar, R.; Bansode, S.; Nandihal, G.; Desai, M.; Moudgalya, K.; Jha, A. eSim: An Open Source EDA Tool for Mixed-Signal and Microcontroller Simulations. In Proceedings of the 2021 4th International Conference on Circuits, Systems and Simulation (ICCSS), Kuala Lumpur, Malaysia, 26–28 May 2021; pp. 212–217. [Google Scholar] [CrossRef] -

Deshpande, N.; Sadakale, R. AMBA AHB to APB Bridge Protocol Verification Using System Verilog. In Proceedings of the 2023 First International Conference on Advances in Electrical, Electronics and Computational Intelligence (ICAEECI), Tiruchengode, India, 19–20 October 2023; pp. 1–3. [Google Scholar] [CrossRef] -

STM32 Cortex®-M4 MCUs and MPUs Programming Manual. Available online: https://www.st.com/resource/en/programming_manual/pm0214-stm32-cortexm4-mcus-and-mpus-programming-manual-stmicroelectronics.pdf (accessed on 15 August 2024.).