This article is brought to you by the Semiconductor Industry Review (ID: ICViews).

This article is brought to you by the Semiconductor Industry Review (ID: ICViews).

It may take until 2039 for a truly 10 nanometer chip to appear.

In recent years, many industry insiders, including NVIDIA CEO Jensen Huang, have expressed pessimism about the future of Moore’s Law. However, a new roadmap released by the chip production research and engineering organization IMEC provides a starkly different conclusion—Moore’s Law is still valid. If this roadmap is accurately implemented, it could foresee the trajectory of chip manufacturing all the way to 2039 , with processes entering a new era of 0.2 nanometer nodes.

Before delving into IMEC’s predictions, it is necessary to re-evaluate the essence of Moore’s Law. It is not an immutable law of nature but rather an induction and speculation based on historical experience regarding industry development trends. Intel summarizes it as “the number of transistors on a single chip doubles every two years while keeping costs low,” meaning that every two years, consumers can obtain chips with double the performance at a similar price. However, the “doubling every two years” is not an absolute standard; it is essentially more of a trend in the semiconductor industry.

However, the condition of “low cost” in Moore’s Law is facing severe challenges in reality. In recent years, the cost of advanced chip manufacturing has skyrocketed, with high-end GPUs often priced at tens of thousands of yuan, which starkly contrasts with the expectations of Moore’s Law. Meanwhile, the naming conventions for chip manufacturing have also come under criticism, as today’s process names have deviated from physical reality. For example, chips manufactured using a 3 nanometer process have internal component sizes that are far from 3 nanometers.

IMEC is an authoritative institution focused on fundamental research in chip production, covering new materials, novel lithography technologies, and next-generation transistor designs. Its research results profoundly influence the entire chip manufacturing industry and endow it with a strong capability to predict the direction of chip technology. In IMEC’s roadmap, the future development of chip manufacturing is clearly visible.

In terms of process nodes, the industry will gradually evolve from TSMC’s current most advanced 3 nanometer technology to 14 angstroms (1.4 nanometers) by 2027 , reaching 10 angstroms (1 nanometer) by 2029 , and continuing to advance to nodes below 2 angstroms (less than 0.2 nanometers) by 2039.

In terms of lithography technology, more advanced extreme ultraviolet (EUV) lithography will help achieve manufacturing goals below 0.2 nanometers; in terms of transistor technology, FinFET transistors will be replaced by nanosheet transistors around 2027, and forked transistors will debut in 2031, followed by complementary FETs that will double transistor density instantly. Starting from 2037, some materials for chips will develop towards two-dimensionality, achieving atomic-level thickness of material sheets through deposition technology. Additionally, the interconnect technology for data and power at the bottom of the chip will continue to upgrade, evolving from basic backside interconnects to more complex global interconnects and local signal line backside interconnects.

It is worth noting that there is a significant difference between the naming of process nodes and the actual component sizes.

Before 1990, the reduction of gate lengths was almost entirely linear, and the name “Xnm” intuitively reflected the performance of the chip. The length and width of each generation of transistors are 0.7 times that of the previous generation (length 0.7*width 0.7=0.49), meaning that the area of a single transistor shrinks to half of its original size, confirming the description of Moore’s Law that transistor density doubles. For example, 180nm>130nm>90nm>65nm>45nm>32nm>22nm, where “X” refers to the length of the chip gate, which is the distance from the source to the drain of a MOS transistor. As the number of advanced processes decreases, the corresponding transistor density increases, leading to lower chip power consumption and higher performance.

In the subsequent technological evolution, the speed of process node reduction accelerated to about 0.72 times, and it is no longer completely linear. Field-effect transistors have also gradually deviated from their originally fixed structure, such as the emergence of spatially structured transistors like FinFET, where the channel becomes three-dimensional, and the channel length gradually can no longer represent the highest precision of the process. 7nm, 5nm, 3nm are no longer representative of channel lengths; they serve as equivalent lengths, merely numbers.

The length of the gate is an important indicator of chip manufacturing processes; the smaller the gate length, the faster the current flowing between the source and drain. Fin Pitch (Fin Pitch) is also an important parameter for measuring process advancement. During the FinFET transistor era, increasing the height of the fins and reducing the spacing between fins can effectively increase drive current, thereby improving efficiency. Other metrics include metal spacing and logic unit dimensions; the smaller the metal spacing, the less capacitive effect needs to be overcome; the lower the minimum height of logic units, the more advantageous it is for 3D stacking.

In TSMC’s 3 nanometer process, the actual distance between transistor gates is 23 nanometers. By 2027, at the 14 angstrom node, this distance will shrink to 21 nanometers, and by 2039, it is expected to be between 14 nanometers and 10 nanometers. This means that a truly 10 nanometer chip may not appear until 2039, but continuous technological progress is far more important than naming.

According to IMEC’s predicted development pace, by 2039, the complexity of chips will exceed imagination. Comparing with Intel’s 32 nanometer process manufactured Sandy Bridge CPU in 2011, which had only 1.1 billion transistors; today’s Intel Core Ultra 9 285K chip has nearly 18 billion transistors. By analogy, the number of transistors in CPUs in 2039 is expected to reach about 300 billion, while the number of transistors in GPUs may even approach 1.5 trillion.

Although these figures still contain speculative elements, it is undeniable that the core logic of doubling transistor counts and increasing chip complexity in Moore’s Law remains valid. However, the industry still faces significant challenges in cost control. How to continue Moore’s Law while addressing cost issues will become a key topic for the development of the semiconductor industry.

* Disclaimer: This article is the original author’s creation. The content reflects their personal views, and our reposting is solely for sharing and discussion purposes, not representing our endorsement or agreement. If there are any objections, please contact us.

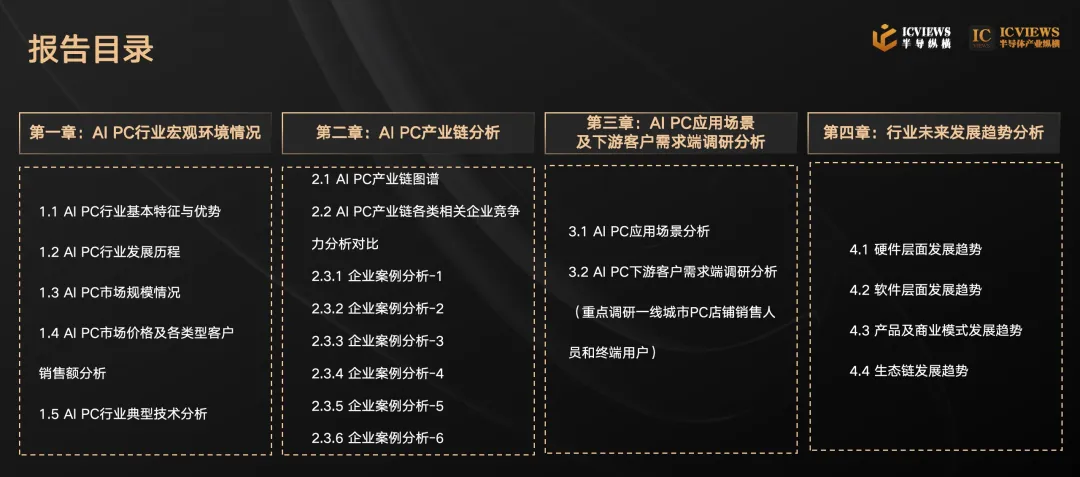

AI PC Industry Research Report

To help players at various levels of the AI PC industry, including hardware, software, model, and terminal layers, better understand the current state and future trends of the AI PC industry, the Semiconductor Industry Review is preparing to write the “AI PC Industry Research Report.” We are currently collecting case studies from various manufacturers in the AI PC industry chain. This report will be published through the Semiconductor Industry Review’s multimedia matrix, and participating cases will receive rich promotional support and exposure opportunities. The case collection starts now, and the report is expected to be released in July. We welcome relevant companies to actively participate in discussions! Interested parties can contact us:

* WeChat ID 1: icviews2

* WeChat ID 2: Joy8432211