Definition

First, let’s look at the definitions of both in the authoritative guide for Cortex-M.

- 1 Exception Definition According to the authoritative guide for Cortex-M, an exception refers to an event that can alter the normal program flow. When an exception occurs, the processor pauses the currently executing task and executes a dedicated program to handle the exception. After handling the exception, it resumes the previously interrupted task.

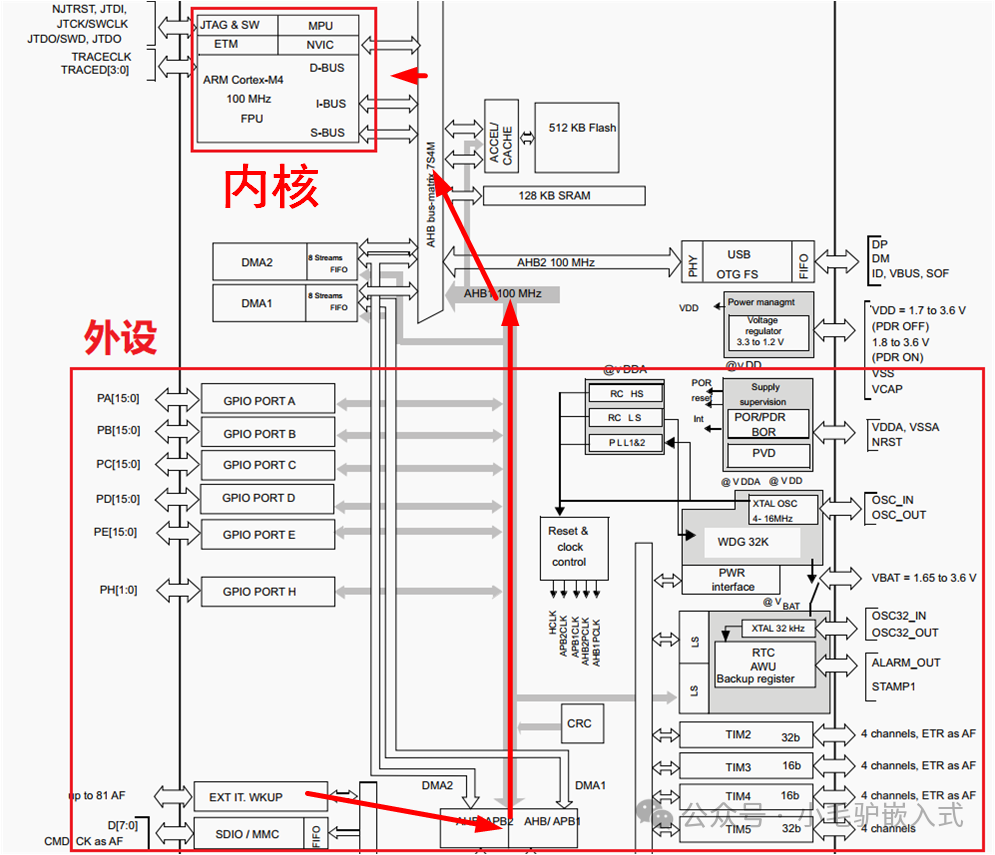

- 2 Interrupt In the ARM architecture, an interrupt is a type of exception. Interrupts are generally generated by peripherals outside the core, but can also be triggered by software. The exception handling function for interrupts is commonly known as the ISR (Interrupt Service Routine).

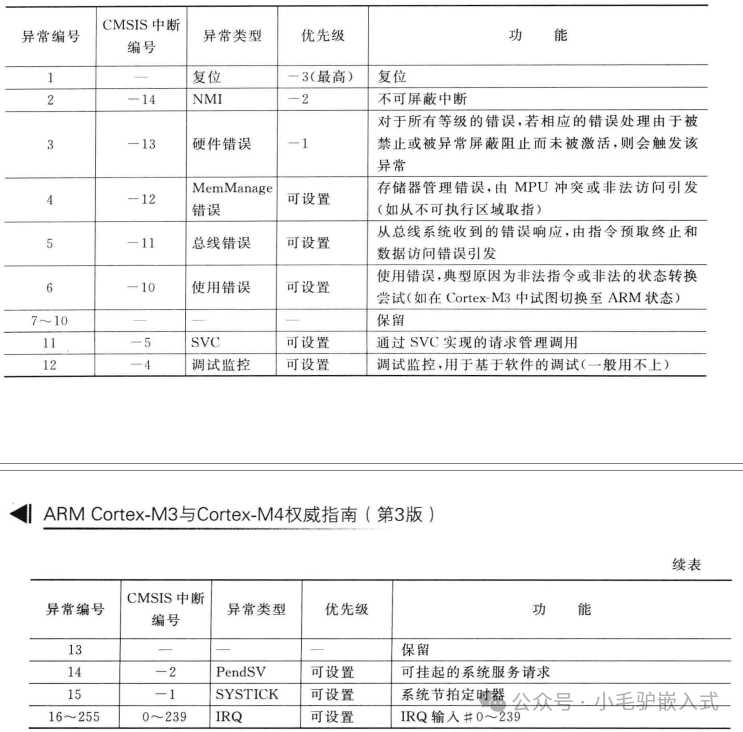

- 3 Types of Exceptions The types of exceptions in Cortex-M are shown in the table, where exception numbers 1 to 15 are system exceptions, referred to as exceptions, and the rest are interrupts.

Supplement: Among exception events, hardware errors are the most common. Other types, such as memory management errors and debugging monitor errors, can also play a significant role in software debugging. For example, memory management exceptions can set specific memory protection areas and define the types of operations to monitor. When the program unexpectedly reads, writes, or executes in this area, it can trigger a memory management exception event. Debugging monitor exceptions can be paired with debugging facilities in the core, such as DWT and FPB, to set offline breakpoints and achieve non-intrusive program monitoring.

Supplement: Among exception events, hardware errors are the most common. Other types, such as memory management errors and debugging monitor errors, can also play a significant role in software debugging. For example, memory management exceptions can set specific memory protection areas and define the types of operations to monitor. When the program unexpectedly reads, writes, or executes in this area, it can trigger a memory management exception event. Debugging monitor exceptions can be paired with debugging facilities in the core, such as DWT and FPB, to set offline breakpoints and achieve non-intrusive program monitoring.

Differences

Source

- Exceptions originate from the core, such as division by zero, bus errors, hardware errors, etc.

- Interrupts come from peripherals: for example, serial interrupts, external interrupts, etc.; they can also be triggered by software: the NVIC-STR register allows users to read and write, which can be used to generate software interrupts, perform unit testing of interrupt service functions, and test how long interrupts run, making it a very useful debugging tool.Core: The processor core (IP core) designed by ARM, responsible for basic functions such as instruction execution, interrupts, and exceptions. The same core (e.g., M4) behaves consistently across different vendor chips.Peripherals: Function modules added outside the core by STMicroelectronics (e.g., GPIO, ADC, TIM, etc.), with significant design differences among vendors (e.g., USART registers in STM32 and GD32 may differ).

Speed

Due to the different origins of the two, the CPU processes them at different speeds.

- Exceptions are synchronous with the CPU.

- As shown in the figure below, MPU, NVIC, etc., are core-level peripherals located within the core. When an exception occurs, the CPU will handle it immediately.

- Interrupts are asynchronous with the CPU. Interrupts originate from peripherals hanging on the AHB-APB, and the entire process takes about 12 clock cycles. The process is as follows:

- The peripheral generates an interrupt, and the register is set.

- An interrupt request is generated, which must pass through:

- APB

- AHB

- AHB bus matrix

- NVIC

- NVIC responds to the interrupt request, the interrupt pending register is set, and the CPU is requested to handle it.

- CPU– The CPU enters Handler mode, while the hardware clears the pending flag.

- Enters ISR