This article is approximately 8,000 words long, recommended for saving and reading.

This article is approximately 8,000 words long, recommended for saving and reading.

Author | Beiwai NannxiangProduced by | Chip Technology and Process

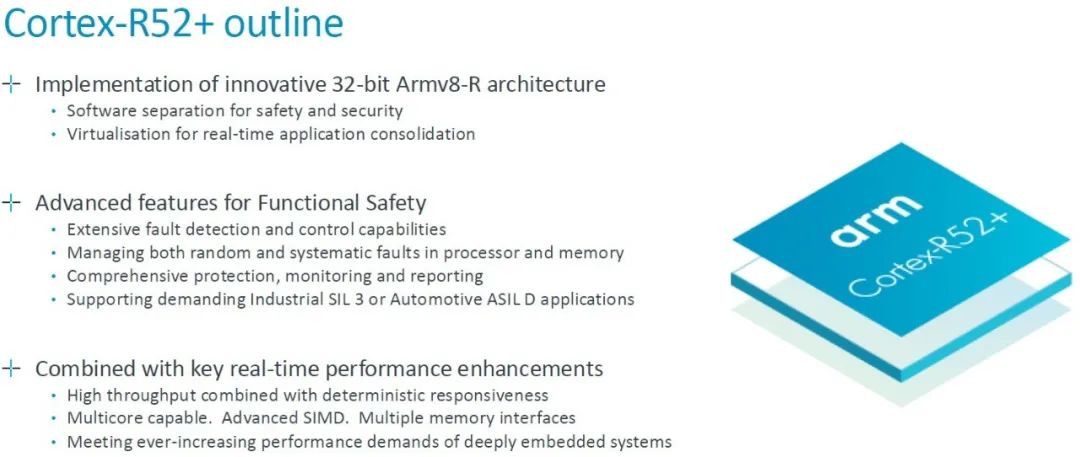

Cortex-R52+ is an enhanced version of Cortex-R52, designed to meet the integration and virtualization needs of functional safety applications while maintaining software compatibility. It is based on the Armv8-R architecture, providing hardware-level task isolation and virtualization support, allowing multiple operating systems and applications to run securely on a single processor. Cortex-R52+ is particularly suitable for time-critical applications in automotive electronics, such as Advanced Driver Assistance Systems (ADAS) and cockpit controllers, offering enhanced safety, flexibility, and real-time performance.

#01Background Introduction

The launch of Cortex-R52+ further strengthens Arm’s position in the high-reliability embedded systems market, providing robust support for applications requiring high safety and real-time performance.

The Arm Cortex-R52+ processor features several core characteristics that meet the demands of high-performance and high-reliability embedded systems.

1.1 Architectural Features

- Based on Armv8-R architecture:The Cortex-R52+ adopts the Armv8-R architecture, integrating high performance and high reliability, suitable for real-time control and safety-critical applications.

- Real-time optimization:This processor is optimized for real-time operations, ensuring deterministic behavior and low-latency responses to meet stringent real-time application requirements.

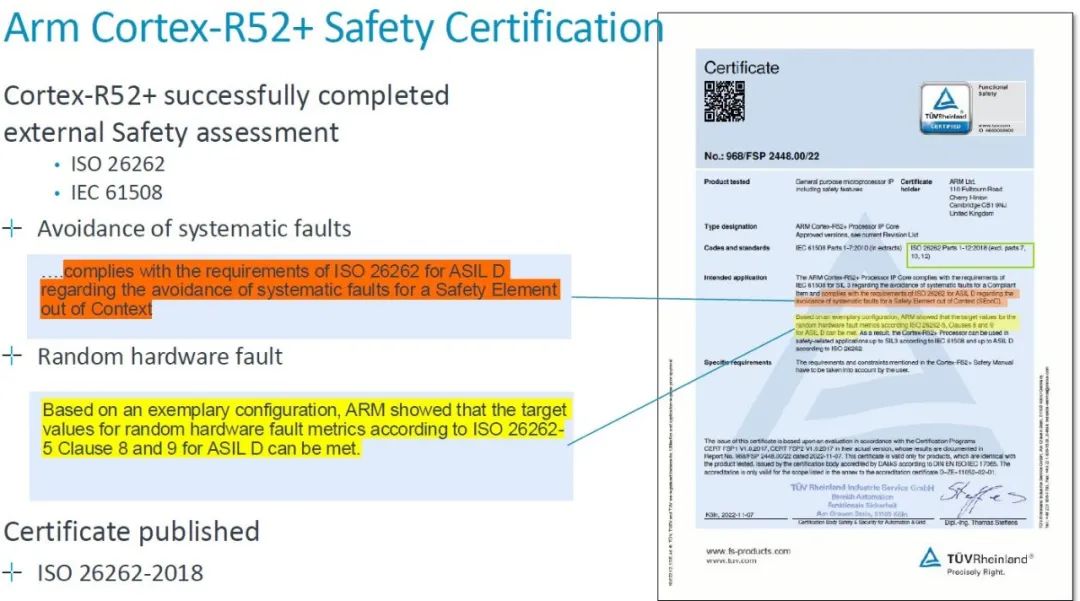

1.2 Safety Design

- Compliance with functional safety standards:The design of Cortex-R52+ complies with functional safety standards such as ISO 26262 ASIL D and IEC 61508 SIL 3, making it suitable for safety-critical applications in automotive and industrial sectors.

- Hardware isolation domain support:The processor provides hardware-enforced software separation, allowing multiple operating systems and applications to run securely on a single processor, ensuring isolation between safety and non-safety tasks.

1.3 Multi-core Support and Resource Isolation

- Multi-core design:The Cortex-R52+ supports multi-core configurations, enabling symmetric multiprocessing (SMP) or asymmetric multiprocessing (AMP), enhancing the system’s parallel processing capabilities.

- Memory Protection Unit (MPU):The processor integrates an MPU, providing task-level memory isolation to prevent interference between different tasks, enhancing system safety and reliability.

1.4 Power Optimization

- Low power design:The Cortex-R52+ employs advanced power management techniques to reduce system power consumption, suitable for embedded systems with strict energy efficiency requirements.

- Dynamic power management:The processor supports dynamic voltage and frequency scaling, allowing real-time adjustment of power consumption based on workload, achieving efficient energy management.

Through these technical advantages, the Cortex-R52+ demonstrates exceptional functional safety and real-time performance in competition, making it an ideal choice for high-reliability embedded systems.In terms of application areas, the Cortex-R52+ shows wide adaptability:

- Automotive electronics:Meets the functional safety and real-time requirements of Advanced Driver Assistance Systems (ADAS), battery management, and sensor fusion.

- Industrial automation:Supports robotic control, real-time communication protocols, and PLC systems, aiding the development of Industry 4.0.

- Medical devices:Provides high reliability and low power solutions, ensuring patient data security and device functional independence.

- Aerospace and defense:Suitable for high-reliability tasks such as flight control and navigation.

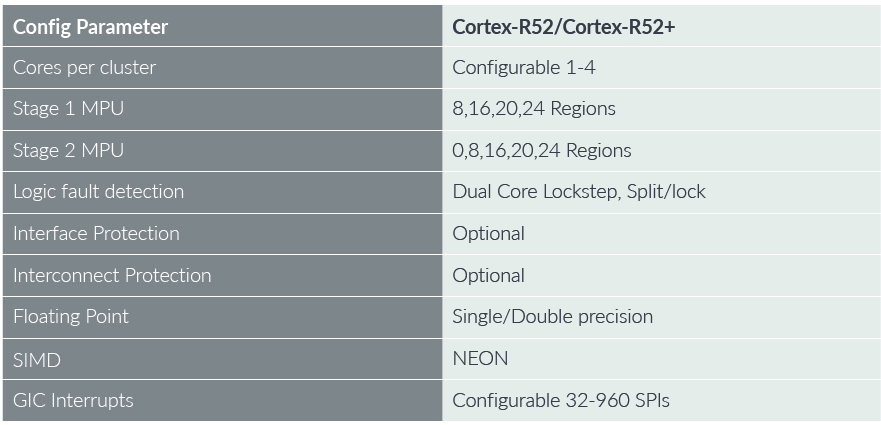

1.5 Configuration Introduction

The configuration parameters for Cortex-R52/Cortex-R52+ are as follows:

| Parameter | Description | Significance |

| Cores per cluster | The Cortex-R52/Cortex-R52+ processor supports configurations of 1 to 4 cores. | Multi-core configurations enhance the processor’s parallel processing capabilities, adapting to complex embedded applications. |

| Users can choose the number of cores based on application requirements, for example: ADAS (Advanced Driver Assistance Systems) may require multi-core support, while simple embedded systems may only need a single core. | ||

| Stage 1 MPU | Provides memory protection for 8, 16, 20, or 24 regions. | The MPU (Memory Protection Unit) is responsible for memory partitioning and preventing illegal access, ensuring system security. |

| Configurable region numbers flexibly adapt to different task complexity requirements. | ||

| Stage 2 MPU | Optional support for 0, 8, 16, 20, or 24 memory protection regions. | Used for finer memory partition management in multi-task systems. |

| Provides an additional layer of security, aiding in achieving higher isolation when running multiple tasks, especially suitable for functional safety-critical scenarios such as automotive and industrial applications. | ||

|

Logic fault detection |

Supports dual-core lockstep and core splitting/locking. | Dual-core lockstep: Two cores run the same instruction stream in sync to detect logic errors. When one core fails, the other core can continue to operate normally. |

| Core splitting/locking: Depending on the needs, multi-core can be set to run as independent tasks (split mode) or work collaboratively (locked mode). | ||

| Enhances the capability of high-reliability systems, suitable for high-demand scenarios such as automotive and aerospace. | ||

| Interface Protection | Optional interface protection features. | Prevents external devices from initiating illegal operations or data tampering through interfaces. |

| Enhances the overall system’s resistance to attacks, ensuring the security of interface data communication. | ||

| Interconnect Protection | Optional interconnect protection features. | Ensures data integrity and security on the processor’s internal interconnect bus. |

| Protects critical data transmission, preventing malicious data tampering or unauthorized access. | ||

| Floating Point | Supports single precision and double precision floating-point operations. | Floating-point operations support complex mathematical calculations (such as sensor data processing, image processing). |

| Single precision is suitable for applications with lower performance requirements,double precision is used for high-precision requirement scenarios (such as medical imaging and flight control systems). | ||

| SIMD | Supports NEON technology. | NEON is Arm’s SIMD technology used to accelerate vector computation tasks. |

| Commonly used in signal processing, audio/video encoding and decoding, significantly improving performance and power efficiency. | ||

| GIC Interrupts | Supports 32 to 960 configurable shared interrupts (SPIs). | GIC (Generic Interrupt Controller) manages system interrupt requests. |

| Meets interrupt requirements from simple to complex embedded applications, supporting 32 to 960 interrupts. | ||

| Provides flexible interrupt priority configuration, ensuring real-time tasks respond quickly. |

This configuration parameter table demonstrates the technical advantages of Cortex-R52/Cortex-R52+ in performance, safety, real-time capability, and scalability. These features make it an ideal choice for high-reliability embedded systems.

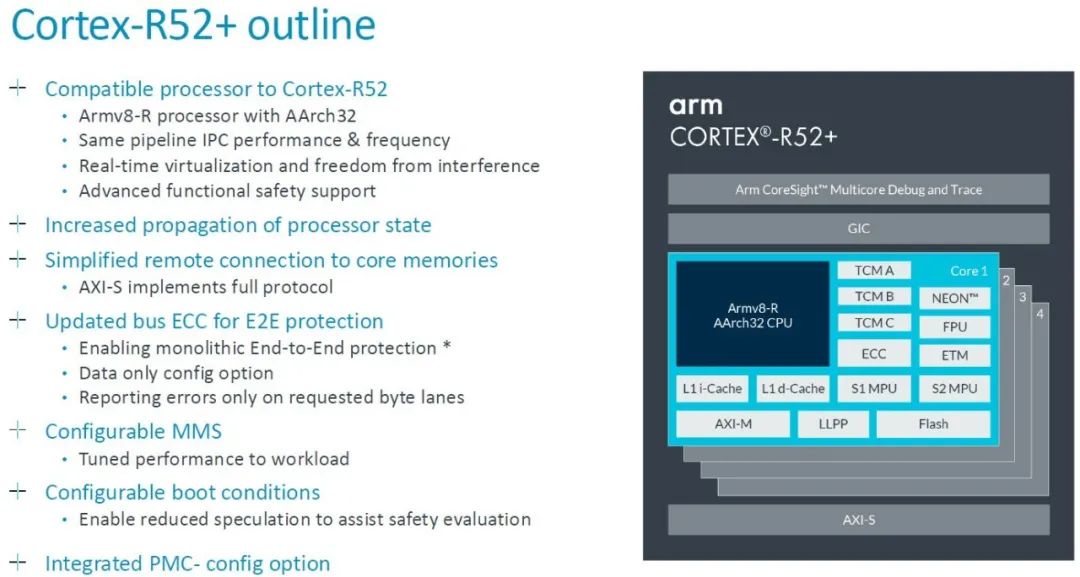

1.6 Enhanced Features of Cortex-R52+

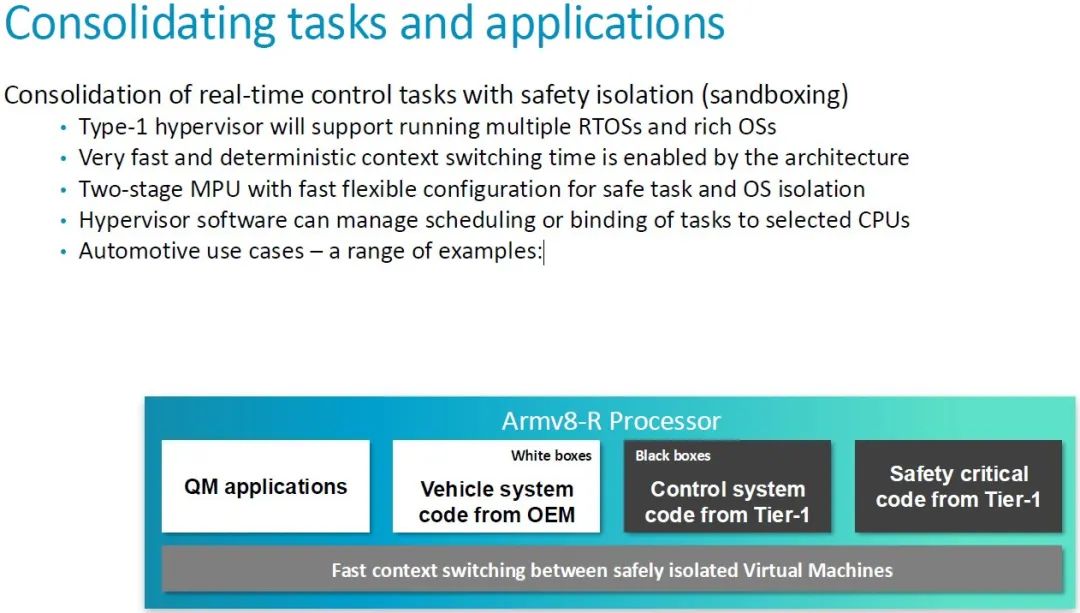

The Cortex-R52+ further enhances real-time performance, safety, and configurability while maintaining the high performance and reliability of Cortex-R52, particularly excelling in real-time virtualization, fault diagnosis, data integrity protection, and memory management optimization.

| FeatureDescription | Main Advantages | |

| 1.Cortex-R52Compatible Processor | The Cortex-R52+ is an enhanced and compatible version of Cortex-R52, optimized for real-time computing and functional safety scenarios. | – SupportsArmv8-Rarchitecture and AArch32instruction set, providing ideal support for embedded systems while meeting high-performance requirements and ensuring real-time capabilities. |

| – Maintains the same pipeline IPC performance and frequency as Cortex-R52, ensuring a smooth software migration process. | ||

| – Hardware-level support forreal-time virtualization and interference isolation, meeting the needs of high safety and high real-time applications. | ||

| – Enhanced functional safety support, compliant withISO 26262 and other industry standards, suitable for automotive control systems and industrial automation in demanding scenarios. | ||

| 2.Improved processor state propagation capability | Provides a faster processor state propagation mechanism. | – Improves context switching efficiency, reducing latency in real-time multi-task environments and enhancing system real-time response capability. |

| – Supports fault diagnosis and recovery for complex embedded systems, accelerating fault handling mode switching and enhancing system reliability. | ||

|

3.Simplified connection between core memory and remote devices |

Simplifies the connection mechanism between core memory and remote devices. | – UsesAXI-Sprotocol as a standardized memory access protocol, reducing communication complexity in multi-core or distributed systems. |

| – Enhances data access efficiency, suitable for multi-core parallel computing and frequent access to remote memory scenarios. | ||

| 4.Enhanced busECCsupportE2Eprotection | Provides enhanced bus error correction code (ECC) functionality, achieving end-to-end (E2E) data integrity protection. | – End-to-endECCprotection, covering the entire link of data generation, transmission, and reception, suitable for high-security scenarios with strict data integrity requirements. |

| – Flexible ECC configuration allows enabling ECC only for critical data, reducing performance overhead. | ||

| – Provides a fine-grained error reporting mechanism for quick problem localization and resolution, improving system diagnostic efficiency. | ||

|

5.Configurable Memory Management System(MMS) |

Dynamic configurable memory management system to meet different task requirements. | – Dynamic optimization of performance, adjusting memory allocation based on actual task load, enhancing storage resource utilization efficiency. |

| – Adapts to real-time multi-task scenarios, optimizing memory access performance and improving task parallel processing capabilities. | ||

| 6.Configurable Boot Conditions | Supports flexible configuration of boot conditions, enhancing system boot safety and reliability. | – Limits speculative execution behavior, reducing the risk of speculative execution vulnerabilities during the boot phase. |

| – Meets functional safety assessment requirements, especially suitable for safety-critical medical devices and automotive control units. | ||

| 7.Integrated Performance Monitoring Counter(PMC)Configuration Options | Provides integrated performance monitoring counter configuration, offering strong tool support for performance debugging and optimization. | – Real-time performance monitoring, quickly identifying performance bottlenecks, helping developers optimize system performance. |

| – Provides flexible PMC configuration capabilities, adjusting monitoring strategies based on application needs, improving debugging efficiency and performance tuning capabilities. |

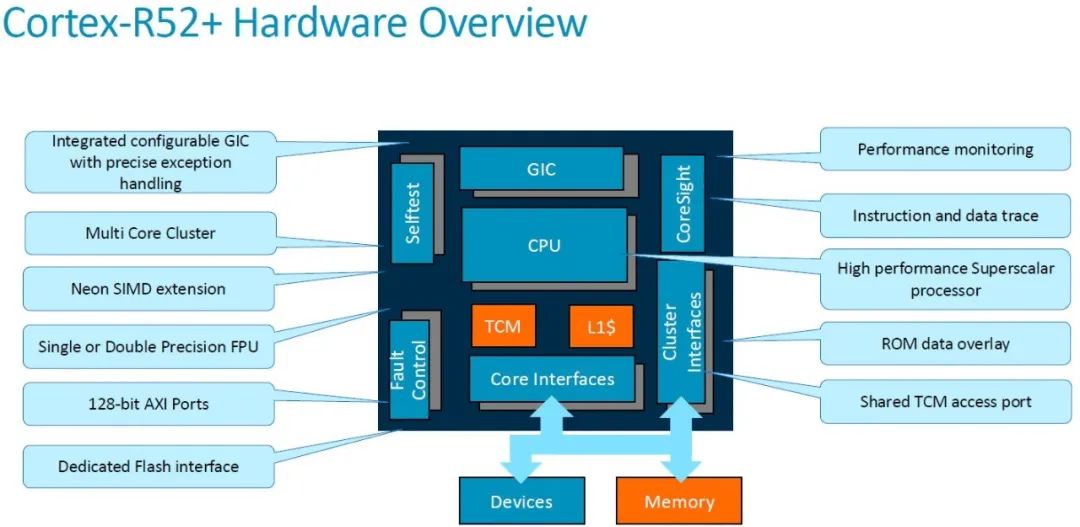

1.7 Hardware Overview of Cortex-R52+

ARM Cortex-R52+ is a processor designed for high reliability and real-time requirements, featuring powerful computing capabilities and highly flexible external interfaces. The following is a detailed analysis of its main hardware modules and features:

| ModuleFeatures | Details | |

| CPU(Processor Core) | High-performance superscalar processor | Supports multiple instruction pipelines, capable of processing multiple instructions in parallel, improving execution efficiency and adapting to high-performance demands. |

| Supports precise exception handling | Designed for real-time systems, quickly and accurately responding to exceptions, ensuring real-time performance in high-reliability systems. | |

| GIC(Interrupt Controller) | Configurable interrupt controller | Supports interrupt priority management and precise interrupt handling, ensuring real-time operating systems effectively control interrupts and handle urgent tasks. |

| Performance Monitoring | Integrated performance monitoring functionality, tracking system operating efficiency in real-time, helping optimize system performance. | |

| CoreSight | Instruction and data tracing | Provides debugging functionality, capturing instruction and data flow in real-time, assisting embedded system development and debugging. |

| ROMData Overlay | Supports dynamic modification of data in ROM, facilitating functional testing and verification. | |

| L1Cache (L1 Cache) | Low-latency access | Accelerates data access, improving processor response speed, especially suitable for frequently accessed data. |

|

TCM(Tightly Coupled Memory) |

Low-latency storage | Provides fast storage access, optimizing system performance. |

| Shared Access Port | Supports multi-core shared storage, enhancing multi-core parallel task collaboration capabilities. | |

| Fault Control(Fault Control) | High-reliability design | Supports fault detection and fault tolerance mechanisms, ensuring high stability and safety in critical task applications. |

| Self-Test(Self-Test Module) | Hardware self-test | Provides hardware self-test functionality, ensuring reliability during the processor’s startup and operation. |

| 128bitAXIInterface | High bandwidth, low latency | Supports high-speed data transmission, meeting real-time systems’ high-performance requirements, optimizing connections with external devices or memory. |

| Dedicated Flash Memory Interface | Optimizes startup performance | Designed specifically for flash memory devices, supporting efficient program code storage and fast startup. |

| Neon SIMDExtension | Parallel computing capability | Supports single instruction multiple data parallel processing, accelerating computation-intensive tasks such as multimedia, signal processing, and machine learning, improving computational efficiency. |

| Single precision/Double precision floating-point unit (FPU) | Floating-point operation support | Provides single precision (32-bit) and double precision (64-bit) floating-point operations, suitable for complex mathematical operations (such as filtering in control systems, PID algorithms). |

| Multi-core Cluster | Multi-core structure | Supports multiple cores forming a cluster, capable of processing tasks in parallel, with each core operating independently or collaboratively, optimizing multi-task processing performance. |

|

Device Interface |

Connection with external devices | Supports connections with sensors, actuators, and other external devices, ensuring rapid data transmission and real-time processing, adapting to embedded system requirements. |

| Memory Interface | Connection with external memory | Supports connections with external memory such as DRAM or SRAM, providing efficient data access and large-capacity storage support. |

| Cluster Interface | Communication coordination between multi-cores | Supports efficient communication between multiple cores or processors, ensuring task allocation and load balancing, maximizing system resource utilization efficiency. |

#02Introduction to Exception Levels and Two-Stage Memory Protection Unit (MPU)

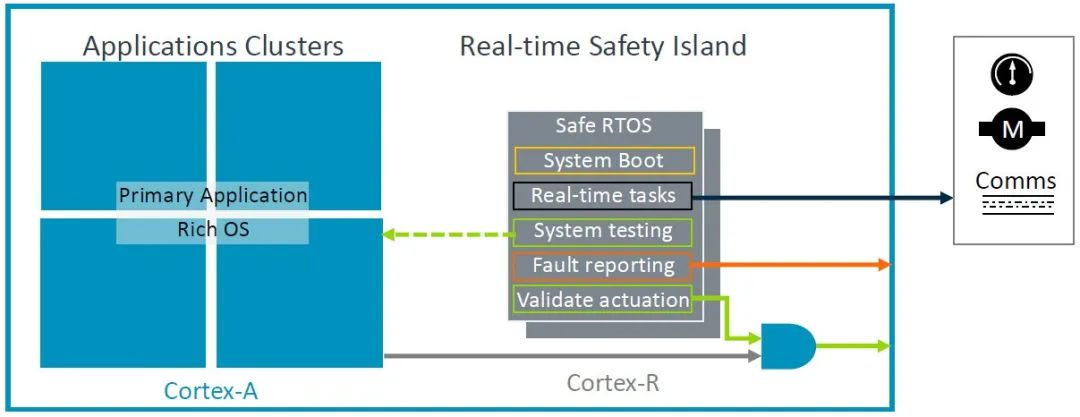

As the number of software applications in vehicles continues to increase, more applications are integrated into a single microcontroller, especially in domain/area controllers, which provide a more streamlined bridge between the central vehicle computer and the electromechanical edge ECUs (Electronic Control Units). This integration mechanism is particularly prominent in modern vehicles, especially in the interaction between domain controllers and central computers, involving different hardware architectures and operating systems.

- Central vehicle computer:Typically uses processors based on Arm Cortex-A cores, running POSIX-based operating systems andAdaptive AUTOSAR, handling complex computing tasks and advanced applications.

- Electromechanical edge ECUs:Typically adopt Arm Cortex-R or Cortex-M cores, primarily responsible for real-time tasks with relatively low computational requirements, such as sensor control, actuator control, etc.

In systems requiring separation of different applications,using microcontrollers like Cortex-R52+ can support allocating applications to run in different virtual machines (VMs). Each virtual machine provides an independent runtime environment, typically consisting of the following components:

1. Physical or virtual processor cores:Each virtual machine can run on independent processor cores, or multiple virtual cores can share physical cores.

2. Memory:Virtual machines allocate independent memory space for each application.

3. Peripherals:Virtual machines can have their own virtual peripherals or share physical peripherals with other virtual machines.

4. Configuration registers:Each virtual machine has independent configuration registers, ensuring system isolation.

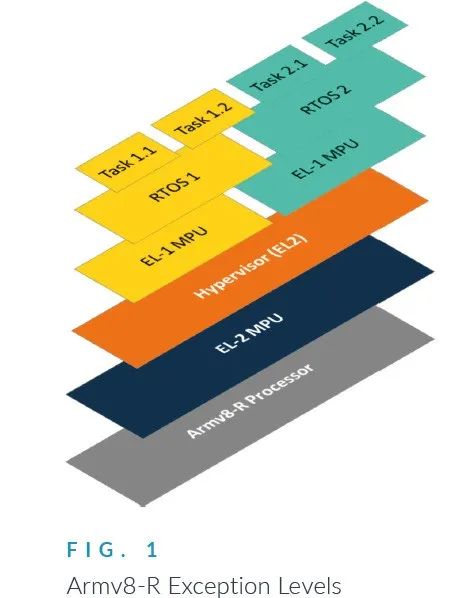

These virtual machines are managed by a hypervisor, typically running at the EL2 (Exception Level 2) privilege level of Cortex-R processors. The hypervisor functions similarly to an operating system, creating an illusion for the software in the virtual machines that it is running on an independent microcontroller, rather than sharing the same physical hardware resources with other virtual machines.

These improvements enhance the resource management and security capabilities of Cortex-R processors. By introducing EL2 exception levels and two-stage MPU, the processor can not only support isolation of multi-tasking and multi-operating systems but also maintain real-time performance in high-security scenarios.

2.1 General Introduction

As part of the Armv8-R architecture, these processors introduce exception levels and a two-stage memory protection unit (MPU), providing strong support for resource management and task isolation in embedded systems, as detailed below:

| CategoryContent | Details | |

| Exception Level Extension | New Exception Level2 (EL2) | Function: |

| EL2 is dedicated to running hypervisors or separation kernels, responsible for managing software access and interaction with shared resources in the system. | ||

| Simplifies resource management, ensuring isolation between software. | ||

| Functions and Applications of EL2 | Function: | |

| Achieves isolation between tasks when running the same operating system on a single processor. | ||

| Provides isolation capabilities between different operating systems in multi-operating system scenarios. | ||

| User Space and Operating System Space Collaboration | EL0(User Space): | |

| Executes application tasks. | ||

| Focuses on efficient task execution. | ||

| EL1(Operating System Space): | ||

| Controls task resources, managing system resource access permissions. | ||

| Provides higher resource security assurance through collaboration with EL2. | ||

|

Two-Stage Memory Protection Unit (MPU) |

Stage 1MPU(Controlled byEL1Operating System) | The operating system manages its resource access permissions through the Stage 1 MPU, providing basic memory protection functionality, ensuring the security and stability of operating system resource access. |

| Stage 2MPU(Configured byEL2) | New Features: | |

| Configured and controlled by the hypervisor running at EL2. | ||

| Further refines resource management and access control. | ||

| Enforces isolation between tasks and resources, suitable for multi-tasking or multi-operating system environments. | ||

| Resource Access Management Mechanism | Centralized Management Based onEL2 | Software running on EL2 (such as hypervisors) is responsible for handling task resource access requests. |

| Through the cooperation of Stage 1 and Stage 2 MPU, resource access permissions are enforced, ensuring secure allocation and management of resources. | ||

| Supports Multi-Level Contexts | Supports multiple task contexts, each context can apply different security protection strategies, flexibly responding to security needs in multi-task concurrent scenarios. |

*Armv8-R Cortex-R processors do not provide a Memory Management Unit (MMU). Hypervisors running on Cortex-A devices can use their MMU to provide each virtual machine with a completely independent virtual address space. For example, customer software running within each virtual machine can link to the same address and use the same memory address range for data storage.Cortex-R52+ provides a Memory Protection Unit (MPU) that allows hypervisors to protect one virtual machine’s memory from interference by another virtual machine, but does not allow each virtual machine to have an independent virtual address space.。

2.2 Introduction to Exception Levels and Two-Stage MPU

New exception levels and two-stage MPU introduce multi-layer security protection for the system, meeting high-security needs. At the same time, the system provides configurable task isolation capabilities, adapting to embedded scenarios from single-task to complex multi-tasking and multi-operating systems. By avoiding the latency issues brought by MMU, this architecture ensures efficient operation of real-time systems, enhancing overall system performance. The following diagram illustrates the exception levels (Exception Levels) of Armv8-R architecture and its related modules, mainly reflecting the layered structure and resource management mechanism between different tasks, operating systems, and hardware. The detailed analysis is as follows:

Feature Analysis of the Diagram

- Layered Architecture:The hierarchy shown in the diagram, from bottom to top, is as follows:

- Hardware Layer (Processor)

- EL2 (Hypervisor and EL2 MPU):Responsible for centralized management and isolation.

- EL1 (RTOS and EL1 MPU):Provides resource allocation and task scheduling for the operating system.

- Task Layer:Execution of specific tasks.

- Dual Memory Protection:

- EL1 MPU provides the first stage of protection.

- EL2 MPU provides a higher priority second stage of protection, achieving finer-grained memory management.

- Multi-Operating System Support:Allows multiple real-time operating systems to coexist (RTOS 1 and RTOS 2), managing their tasks separately.

- Task Isolation:Tasks within the same RTOS, as well as tasks between different RTOS, are isolated through EL2 and MPU, enhancing system security.

This diagram illustrates how the Armv8-R architecture provides secure and efficient solutions for multi-operating systems and multi-task environments through multi-layer exception levels, memory protection units, and task management mechanisms.

2.2 Design and Function of System-Level Memory Protection Unit (SMPU) and Peripheral Protection Mechanism

2.2.1 Advantages of SMPU Compared to Core MPU

- Global Protection:The core MPU’s role is limited to local memory, while SMPU provides cross-component protection capabilities, covering the entire system.

- Supports Multi-Component Virtualization:SMPU can create virtual machines containing multiple Cortex-R52+ cores and other DMA components (such as Cortex-M cores). By connecting through the memory bus, different components can efficiently share resources while maintaining strict access control.

- Enhanced Isolation:Divides memory, peripherals, and interrupts, providing stronger virtual machine isolation, especially suitable for scenarios with high real-time and security requirements.

2.2.2 Functions and Roles of SMPU (System-Level Memory Protection Unit)

- Main Function:SMPU controls whether hardware components in the system, such as DMA controllers, processor cores (like Cortex-R, Cortex-M), and other peripherals, can access specific memory areas. It ensures that only authorized hardware can access designated memory spaces, preventing unauthorized access and enhancing system security. It provides a global memory protection mechanism that surpasses the protection range of a single core MPU.

- Region Configuration:

- SMPU is typically divided into multiple regions, each with the following attributes:

- Starting Address and Size

- Access Permissions, specifying which bus managers (or virtual machines, VMs) can access that region.

- In more advanced designs, SMPU can combine with the Cortex-R52+ VSCTLR.VMID register to allocate memory regions through VM identifiers (VMID), enhancing virtual machine isolation capabilities.

Advantages:

- Cross-Component Protection:Allows multiple bus managers to share a memory protection mechanism, not limited to a single core.

- Virtualization Support:Enables microcontrollers to create virtual machines (VMs) containing multiple cores (such as Cortex-R and Cortex-M) and DMA controllers.

- Enhanced Security:Prevents unauthorized components from accessing sensitive memory areas, thereby improving system security.

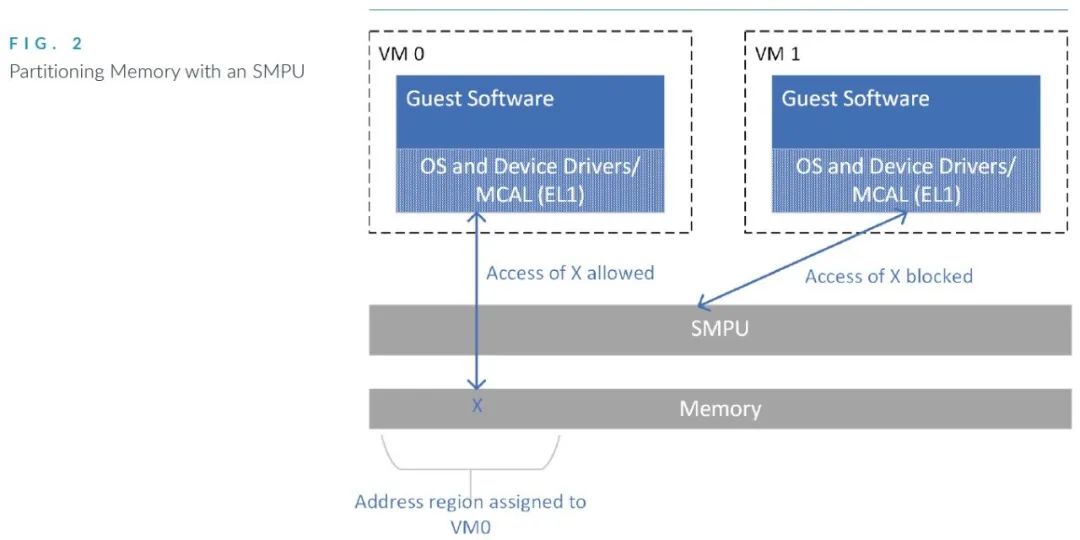

The following diagram illustrates the concept of memory partitioning achieved through the System-Level Memory Protection Unit (SMPU) for isolating memory access between multiple virtual machines (VMs), with detailed analysis as follows:

Structure and Meaning of Each Part in the Diagram

| ComponentFunction and Description | Function and Description |

| Virtual Machines (VM0 and VM1) | VM0 and VM1 represent two virtual machines in the system, each running independent operating systems, device drivers, and application software. |

| Guest Software: Applications running in the virtual machine (user-mode programs). | |

| OS and Device Drivers/MCAL (EL1): The operating system and device drivers of the virtual machine are located in the privileged mode of the virtual machine (EL1, Exception Level 1), responsible for managing hardware resources. | |

| Isolation Mechanism: Clear isolation mechanisms are needed between virtual machines to prevent one virtual machine from accessing another’s memory or hardware resources. | |

| System-Level Memory Protection Unit (SMPU) | SMPU is a hardware module responsible for controlling memory access permissions. |

| Memory Access Control: SMPU decides whether specific virtual machines can access certain memory areas based on configured rules. | |

| Memory Address Range Setting: SMPU can set access permissions based on memory address ranges (e.g., address area X). For example, VM0 can be granted access to address area X, while VM1 cannot access that area. | |

| Enhanced Isolation: The mechanism of SMPU enhances the isolation between virtual machines and system security. | |

|

Memory (Memory) |

Some address areas in memory (e.g., address area X in the diagram) are allocated to specific virtual machines (e.g., VM0). |

| Memory Allocation: Address area X is allocated to a virtual machine (e.g., VM0), meaning VM0 has the right to access that area. Only VM0 is authorized to access that area, while VM1 is not. | |

| SMPU’s Task: Ensures that only authorized virtual machines (e.g., VM0) can access designated memory areas. When an unauthorized virtual machine (e.g., VM1) attempts to access address area X, SMPU will block that access request, ensuring system security. |

Specific Logic of Access Permissions in the Diagram

1.VM0 Accessing Address Area X: Allowed Access

- In the diagram, VM0 initiates an access request to memory address area X.

- SMPU checks and finds that VM0 has permission to access X, thus the request is allowed.

- VM0 can read and write to address area X normally.

2.VM1 Accessing Address Area X: Access Blocked

- When VM1 initiates an access request to memory address area X, SMPU performs a permission check.

- Since address area X is not allocated to VM1, SMPU blocks that access request.

- This ensures that VM1 cannot read or modify the contents of address area X.

Key Design Points of Memory Partitioning Mechanism

1. Address Range Division:Each address range (e.g., X) can be allocated to a specific virtual machine. The division of address ranges is configured based on the system design requirements, typically including:

- Code Segment:Stores program instructions.

- Data Segment:Stores data during program execution.

- Device Registers:Used to control hardware peripherals.

2. Access Permission Control::SMPU can precisely configure access permissions for each memory area, including:

- Which virtual machines can read, write, or execute the contents of that area.

- Handling methods when unauthorized access occurs (e.g., generating exceptions).

3. Enhanced Isolation::Through the memory partitioning mechanism of SMPU, it can ensure that each virtual machine can only access its authorized memory areas, achieving memory isolation. This isolation can prevent:

- Malicious attacks or unintentional interference between virtual machines.

- Sensitive data being read by unauthorized virtual machines.

Through SMPU’s memory address range partitioning, memory isolation between virtual machines can be achieved, enhancing system security and stability. This mechanism is particularly important in embedded systems requiring multi-task parallelism.

2.2.3 Functions and Roles of Peripheral Protection Mechanism

- Main Function:Peripheral protection mechanisms limit the access range of peripheral registers by allocating permissions, ensuring that peripherals are only allowed to be operated by designated bus managers (or VMs).

- Mechanism Features:Each peripheral can be allocated to one or more bus managers (or VMs). Unauthorized bus managers or VMs are prohibited from accessing the registers of protected peripherals.

- Achieved Separation:The peripheral protection mechanism, combined with SMPU, can achieve cluster-level isolation:

- Both memory and peripherals can be allocated to different virtual machines.

- Each virtual machine can include all cores in the Cortex-R core cluster, ensuring resource isolation and independent operation.

#03Conclusion

The launch of Cortex-R52+ represents Arm’s technological innovation in the embedded processor field, further consolidating its leading position in the high safety and real-time market. By supporting multi-task isolation and complex system partitioning, it provides embedded system developers with more flexible and secure solutions.

At the same time, the successful application of Cortex-R52+ accelerates the technological development in cutting-edge fields such as autonomous driving and industrial automation, setting new benchmarks for functional safety and real-time standards in these industries.

With its excellent performance and functional safety features, Cortex-R52+ becomes the ideal choice for high-safety and real-time embedded systems. In the context of the evolving Internet of Things and smart manufacturing, it will provide solid technical support for future high-reliability embedded applications, injecting new momentum into the intelligent transformation of various industries.

References:

1. For Autonomous Driving, ARM Launches the Most Advanced Safety Processor Cortex-R52 – Chip Intelligence2. Cortex-R52+ | Enhanced Safety and Virtualization Support – Arm®3. https://developer.arm.com/documentation/-END-This article is for communication and learning purposes only and does not constitute any investment advice. Some images are sourced from the internet and copyright ownership has not been verified. It is not for commercial use. If there is any infringement, please contact us at [email protected].