This morning, we held a brainstorming session with graduate students to discuss the general concepts of SoC design. I found that many students did not grasp the core of SoC design. Now, while the discussion is still fresh, I will record it here.

First of all, what is SoC design centered around?

SoC design is conducted around the bus. The core knowledge that SoC designers need to master is not the concept of SoC itself, but the concepts of buses and interfaces discussed in the microcomputer principles course. For example, what is a three-bus system, what is a master (Master), and what is a slave (Slave), etc.

By mastering these concepts, one can understand how the processor reads and writes data via the bus, thus understanding how to control and manage the entire system chip through the processor.

When understanding the bus, the most crucial point is to grasp the communication mechanism of the master-slave mode. The processor acts as the host, initiating communication. The peripherals and on-chip memory act as slaves, responding to the communication initiated by the host. Furthermore, it is essential to understand the bus timing and the entire process from initiating communication on the bus to its conclusion. This understanding allows for software access to specific address spaces.

Secondly, how does SoC achieve the integration of IP cores?

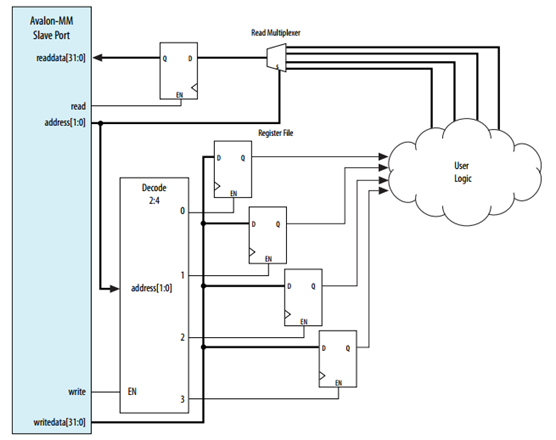

To achieve the integration of IP cores, it is fundamentally about ensuring that data can be written in and results can be read out. This means that the data that needs to be processed by the IP must be input into the IP core in some way, and the results after processing must be readable in some manner. If the IP has multiple functionalities, it is also necessary to convey the type of functionality to be completed to the IP core in a specific way. Once the computation is complete, there must be a way to notify the CPU that the computation has ended. All of this must be implemented through the means of writing in and reading out.

So how can data be written in and results read out? Ultimately, it is about making the IP core ‘visible’ at the software level. To make it visible at the software level, it must be accessible through executing instructions. How to access it? Of course, through the bus. The following diagram makes it clear:

Finally, how is software-hardware co-design addressed in SoC design?

This requires a clear division of tasks and planning between software and hardware IP cores. Generally speaking, the software part executed by the processor is suitable for management tasks such as scheduling, decision-making, and judgment, while hardware IP cores are suitable for more structured computational tasks. At the boundary of software and hardware division, reasonable register groups must be set up to transmit signals and data.

For example, to implement a circuit for rapidly calculating trigonometric functions, we need to realize a hardware computing unit for the Cordic algorithm. However, just implementing this hardware unit is not enough; we also need to write a piece of software code to input the operation data read externally, set the required calculations (Cos/Sin, etc.), and read out the results after the computation is complete. Throughout this process, necessary handshakes and communication must occur, which can be achieved through polling or interrupts.

In fact, all of the above content is not learned from boring courses like ‘SoC Design’; the core issues are clearly explained in ‘Microcomputer Principles.’ However, many educational departments and some university teachers are hastily pushing ‘Microcomputer Principles’ out of the curriculum, replacing it with fast-food courses like microcontrollers, embedded system design, or SoC design. This shortsighted and foolish behavior ultimately forces innocent students to bear the consequences. If you see this blog and your school/college is doing something similar, you must be vigilant!