In modern chips, billions of transistors are interconnected by metal lines to form complex circuits. As the manufacturing process enters the nanoscale, a seemingly “invisible” problem gradually comes to light:Capacitive coupling between metal lines. This coupling not only slows down signal transmission speeds but can also lead to data transmission errors. The key to solving this problem lies inlow dielectric constant (Low-k) materials.

Interconnect Delay

At the 22nm process node, scientists discovered a disruptive phenomenon:interconnect delay (the delay of signal transmission in metal lines) reached 20 times that of transistor gate delay. This means that even if the transistor switching speed is fast, the “traffic jam” of signals in the metal lines can severely hinder overall performance.

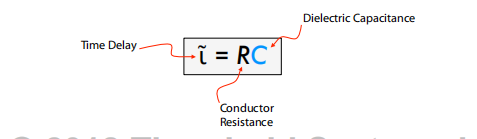

Why is there such a large delay?

The battle between resistance (R) and capacitance (C): The speed of signal transmission is determined by the RC time constant. Although copper (Cu) has low resistivity, if the dielectric medium between metal lines has a high dielectric constant (k value), it significantly increases capacitance (C), leading to a spike in RC values. Capacitive coupling effect: Adjacent metal lines form “invisible capacitance” through the dielectric medium, which interferes with each other when the signal changes, further exacerbating delays.

Capacitive Coupling: A Chain Reaction from “Crosstalk” to Data Errors

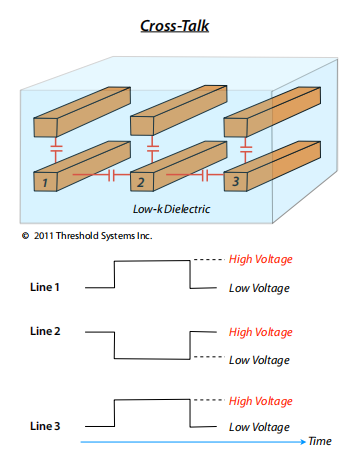

When two metal lines are arranged in parallel, the dielectric medium between them forms capacitance. This capacitance leads to two problems: signal delay: capacitance requires charging and discharging time, slowing down the signal transition speed. Crosstalk: a voltage change in one line can interfere with adjacent lines through capacitive coupling.

The most dangerous scenario: Suppose one line attempts to switch from a high voltage (e.g., 1 V) to a low voltage (0 V), while the lines on both sides simultaneously switch from low voltage to high voltage. At this point, the high voltage on both sides will “pull” the voltage of the middle line through capacitive coupling, preventing it from dropping to a low level, ultimately leading to data transmission errors.

The Salvation of Low-k Materials: How to Break the Capacitive Dilemma?

Low dielectric constant materials (Low-k Dielectric) directly reduce the capacitive coupling between metal lines by lowering the dielectric constant of the insulating medium. The core principle is: reducing the dielectric constant: traditional SiO₂ has a k=3.9, while Low-k materials (such as carbon-doped oxide CDO) can reduce k to 2.5-2.8, decreasing capacitance by 30%-40%. Suppressing electric field propagation: Low-k materials are less likely to support electric field establishment, weakening the charge interaction between adjacent metal lines, thereby reducing the probability of crosstalk.

The Combination of Copper and Low-k

Although copper has extremely low resistivity, using it alone cannot solve the capacitance problem.Copper interconnect + Low-k dielectric combination has become the industry standard: copper reduces resistance (R): the resistivity of copper (1.68 μΩ·cm) is only 60% that of aluminum, reducing signal transmission loss. Low-k reduces capacitance (C): by reducing the k value, the RC time constant is optimized simultaneously, increasing chip speed by 20%-30%.

Future Outlook

As the manufacturing process enters below 3nm, the industry is beginning to explore k<2.0ultra-low dielectric constants

Air Gap Technology: Introducing vacuum pores (k=1.0) between metal lines to further reduce capacitance.