I. The “Unsung Hero” in Embedded Development – HAL

In the vast realm of embedded development, there is a crucial role that often remains “behind the scenes” – the Hardware Abstraction Layer (HAL). It serves as a bridge connecting upper-level software applications with a diverse range of underlying hardware devices. For C++ embedded developers, a deep understanding and clever design of the HAL is the key to unlocking efficient and stable development. Today, we will unveil the mysteries of HAL and explore its “superpowers” in C++ embedded development.

II. What Exactly is the “Magical Tool” of HAL?

Simply put, HAL is a “magical shield” situated between the hardware and upper-level software. It connects closely with the hardware below, familiar with the “temperament” of various hardware types, whether it’s the configuration of processor registers, control registers for peripherals, or complex interrupt handling mechanisms – HAL knows it all. Upwards, it provides a set of concise and unified interfaces for operating systems and applications, akin to crafting a “point-and-shoot camera” for upper-level software, allowing them to utilize various functionalities without delving into the complexities of hardware details.

For instance, different manufacturers may produce similar types of chips that can achieve comparable functionalities, such as GPIO (General Purpose Input/Output) pin control and serial communication. However, their register addresses and configuration methods can vary significantly. Without HAL, every time upper-level software switches to a new chip, it has to undergo substantial code modifications to adapt to the hardware specifics of the new chip, which is undoubtedly a “nightmare”. With HAL, things change dramatically! HAL abstracts common functionalities into unified interfaces, such as gpioWrite(pinNumber, value) for controlling GPIO pin output levels and uartSendData(buffer, length) for serial data transmission. Upper-level software always calls these unified interfaces, while the specifics of the underlying chip and register configurations are managed by HAL, greatly enhancing software portability and allowing the code to “freely traverse” across different hardware platforms.

III. Key Points Not to Overlook When Designing HAL

(1) Hardware Independence: Letting Software “Roam Free”

Ensuring hardware independence is the primary mission of HAL. This means that regardless of the hardware’s manufacturer or architecture, HAL must provide consistent interfaces, allowing upper-level software to feel as though it is always operating in a familiar environment. To achieve this goal, deep abstraction of hardware is necessary during HAL design. For instance, although the internal register configurations for GPIO modules across different chips may vary greatly, HAL can define a unified function prototype gpioConfigure(pin, mode, speed) to configure pin modes and speeds, with differentiated implementations based on different hardware platforms internally. This way, when upper-level software calls this function, it does not need to concern itself with the underlying hardware details, enabling seamless cross-platform operation. Moreover, during code development, it is crucial to adhere strictly to the principle of separating interfaces from implementations, encapsulating hardware-related code within specific modules to avoid leaking hardware characteristics and paving the way for the “free migration” of software.

(2) Performance Optimization: Unleashing Hardware Potential

While HAL’s main responsibility is to abstract hardware, performance must not be overlooked. In some embedded scenarios where real-time requirements are extremely high, such as industrial control and autonomous driving, even subtle delays can lead to severe consequences. When designing HAL, it is essential to reduce unnecessary function call layers to avoid performance losses caused by excessive nesting. For instance, directly manipulating registers is often more efficient than multiple function forwarding. If the balance between direct register access and function encapsulation can be managed well while ensuring hardware independence, a balance between convenience and performance can be achieved. Additionally, optimizing based on hardware characteristics, such as utilizing special instruction sets (like ARM’s NEON instruction set for accelerating multimedia processing) can fully unleash hardware potential and allow the entire embedded system to “fire on all cylinders”.

(3) Scalability: Embracing New Hardware Trends

With rapid advancements in hardware technology, new peripherals and functionalities continue to emerge. HAL must possess good scalability to keep pace with these developments. During the initial design phase, a forward-looking perspective should be adopted, reserving interfaces for potential future hardware functionalities. For example, with the rise of the Internet of Things, low-power Bluetooth (BLE) modules are becoming increasingly popular. If the early-designed HAL reserves function prototypes like bleInitialize() and bleSendData(), even if the current hardware does not include this module, it can easily fill in the function bodies during future upgrades, allowing upper-level software to seamlessly connect to new functionalities without starting from scratch. Furthermore, adopting a modular design approach, encapsulating different hardware functionalities into independent modules, facilitates the addition of new modules and upgrades of old ones, enabling HAL to evolve alongside hardware advancements.

IV. Common “Techniques” for HAL Design and Implementation

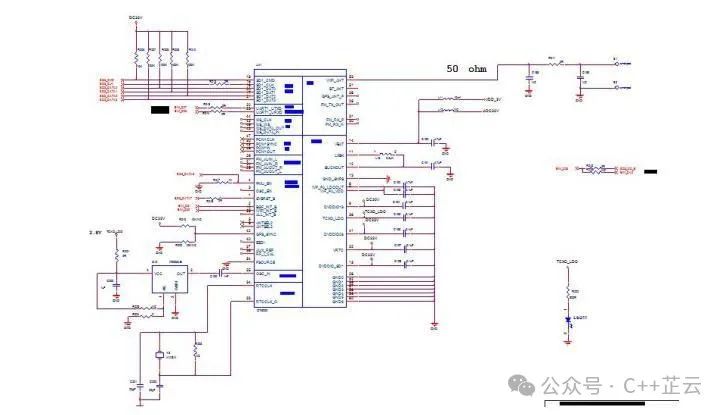

(1) Register Mapping: Directly Hitting the Bullseye

Register mapping is arguably the most “hardcore” HAL design method. It directly maps hardware registers to the memory address space, allowing upper-level software to operate registers as if reading and writing ordinary memory. For controlling GPIO, for example, in C++ code, you only need to define a pointer to the register address:

volatile uint32_t* GPIO_REG = (volatile uint32_t*)0x40020000;(assuming this is the base address of a certain chip’s GPIO register), and then you can directly set the register value with a statement like

*GPIO_REG = 0x0001;, quickly controlling pin states. The advantages of this method are evident: it is highly efficient, with no additional function call overhead, and performs excellently in scenarios with stringent response speed requirements. However, it also has downsides; excessive reliance on hardware registers increases code dependency on hardware, and once the hardware platform changes, register addresses, bit definitions, and other details may vary, requiring extensive code adjustments and compromising hardware independence. Therefore, this method is often used in embedded projects where performance is critically sensitive and hardware is relatively fixed, or in conjunction with other methods in critical performance paths of HAL to leverage its efficiency.

(2) Driver Interface: The Art of Encapsulation

The driver interface is a commonly used and balanced method for HAL implementation. It encapsulates hardware operations within individual driver modules, with each driver targeting specific hardware functionalities and providing a set of concise, unified interface functions to upper-level software. For example, for SPI bus communication, there would be

SpiDriver::init();to initialize the SPI interface, setting clock frequency, mode, and other parameters;

SpiDriver::transferData(buffer, length);is responsible for data transmission and reception. When upper-level software calls these interfaces, it does not need to concern itself with the complex details of the underlying SPI controller’s register configurations and interrupt handling, as the driver manages all hardware interactions internally. This encapsulation greatly enhances hardware independence; when replacing an SPI chip, as long as the new driver adheres to the same interface specifications, upper-level software requires minimal changes. Additionally, it encapsulates complex hardware operations, reducing the likelihood of software errors and improving maintainability, making it the preferred solution for projects prioritizing stability and portability, widely used in various embedded system developments.