Little Science Gas Station

In embedded learning, the STM32 series chips are particularly favored due to their many excellent features, such as the STM32 MCU integrating a wealth of peripherals, including communication interfaces (like UART, SPI, I2C, CAN, etc.), analog and digital interfaces, timers, and interrupt controllers. Today, Little Science introduces the interrupt system of STM32.

Basic Concepts

An interrupt is a mechanism in the processor used to respond to and handle burst or urgent events. When an interrupt occurs, the currently executing program is temporarily halted, and the processor jumps to the interrupt handler (also known as the interrupt service routine) to process the interrupt event. After handling the interrupt, the processor returns to the interrupted program to continue execution. Interrupts can be classified into internal and external interrupts:

1) Internal interrupts: Triggered by modules or events within the processor, such as timer overflow or non-empty serial port receive buffer. Internal interrupts can be used for regularly executing specific tasks or detecting state changes.

2) External interrupts: Triggered by external devices or signals, such as a button press or changes in external sensor signals. External interrupts are used to respond to external events and handle related tasks in a timely manner.

The interrupt mechanism in the processor allows it to respond promptly to important events while executing the main program, enhancing the system’s real-time performance and flexibility. By appropriately configuring interrupt priorities and enabling interrupts, different interrupts can be managed and controlled to ensure that high-priority interrupts are processed in a timely manner.

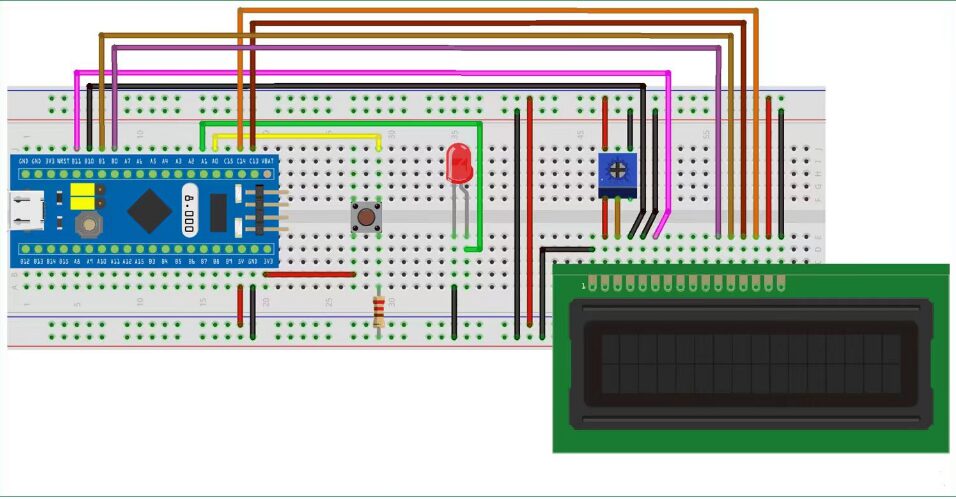

Figure 1 STM32 Circuit Connection Diagram

In STM32 microcontrollers, the interrupt system is an important mechanism for handling external events and priorities. It allows the microcontroller to respond promptly to specific events while executing the main program. The following are the basic concepts of the STM32 interrupt system:

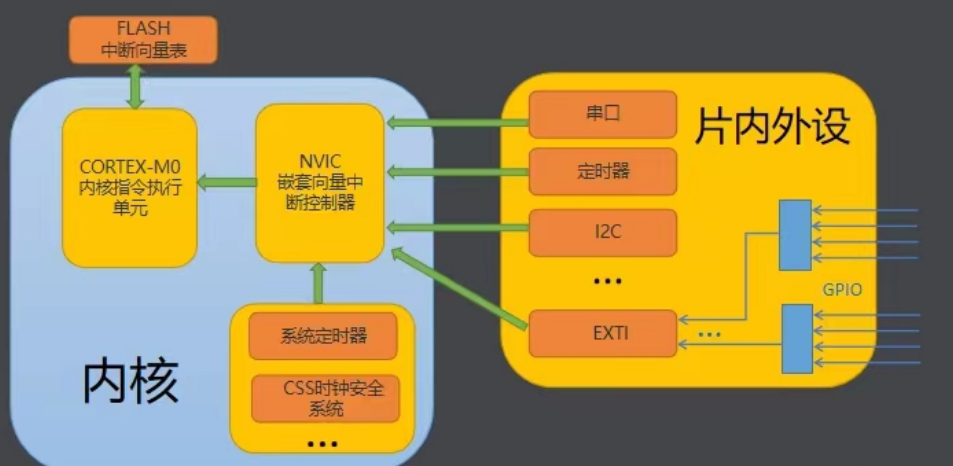

Interrupt vector table: The interrupt vector table is a table that stores the addresses of interrupt handlers. Each interrupt has a specific vector, and when an interrupt occurs, the microcontroller jumps to the corresponding interrupt handler address based on the interrupt vector table.

Interrupt request: Also known as interrupt source or interrupt event, refers to the signal sent by external devices or internal modules to notify the microcontroller that a specific event has occurred, such as a button press or timer overflow.

Interrupt controller: The interrupt controller is responsible for managing interrupt requests and allocating priorities. STM32 microcontrollers typically have multiple interrupt controller modules, such as the NVIC.

Interrupt priority: Each interrupt has a priority used to determine the execution order of interrupt handlers. Higher-priority interrupts can interrupt lower-priority interrupts or the main program being executed.

Interrupt handler: Also known as interrupt service function, is a piece of code used to handle specific interrupts. When an interrupt occurs, the microcontroller jumps to the corresponding interrupt handler to execute related operations, and after completion, returns to the main program.

Interrupt enable: By setting the corresponding interrupt enable bits, specific interrupts can be enabled or disabled. Once an interrupt is disabled, even if an interrupt request occurs, the microcontroller will not respond.

Interrupt flag: The interrupt flag is used to indicate whether a specific interrupt has occurred. After handling the interrupt, the corresponding interrupt flag needs to be cleared to allow the same interrupt to be triggered again.

When using STM32, you can manage and handle various interrupt requests by configuring the interrupt vector table, interrupt priorities, and enabling interrupts. The interrupt system allows the microcontroller to respond promptly to external events, enhancing the system’s real-time performance and concurrent processing capability.

Significance of Interrupts

Interrupts can process burst events in a timely manner, achieving program parallelization and thereby improving CPU efficiency. Interrupts are significant in computer systems, and here are some important meanings of interrupts:

1. Real-time response: Interrupts enable the processor to respond promptly to external or urgent events. Through the interrupt mechanism, the processor can immediately halt the current task and process the interrupt request, ensuring real-time response to important events.

2. Asynchronous processing: The interrupt mechanism allows the processor to handle interrupt events asynchronously without relying on the execution of the main program. This enables the processor to handle multiple concurrent interrupt events while executing the main program, improving the system’s concurrent processing capability.

3. Resource sharing: The interrupt mechanism allows multiple devices or modules to share the processor’s resources. Different devices or modules can issue interrupt requests through the interrupt mechanism, and the processor processes these interrupts based on priority and configuration, achieving reasonable sharing and utilization of resources.

4. Reduced power consumption: In some cases, the processor can enter a low-power mode. By configuring interrupt wake-ups, the processor can wake up only when specific interrupt events occur while in standby or sleep mode, thereby reducing system power consumption. Priority management: The interrupt mechanism allows for priority management of different interrupt requests. By setting interrupt priorities, the processor can ensure that high-priority interrupts are processed in a timely manner, thereby enhancing the system’s real-time performance and responsiveness.

5. System reliability: The interrupt mechanism helps improve the reliability and fault tolerance of the system. Through reasonable design of interrupt handlers and error handling mechanisms, timely responses and appropriate measures can be taken in the event of exceptions or errors, ensuring system stability and reliability.

In summary, the interrupt mechanism plays a crucial role in computer systems, enhancing the system’s real-time performance, concurrent processing capability, resource sharing ability, and providing support for system reliability and maintainability.

Interrupt Handling Process

[Processing Steps]

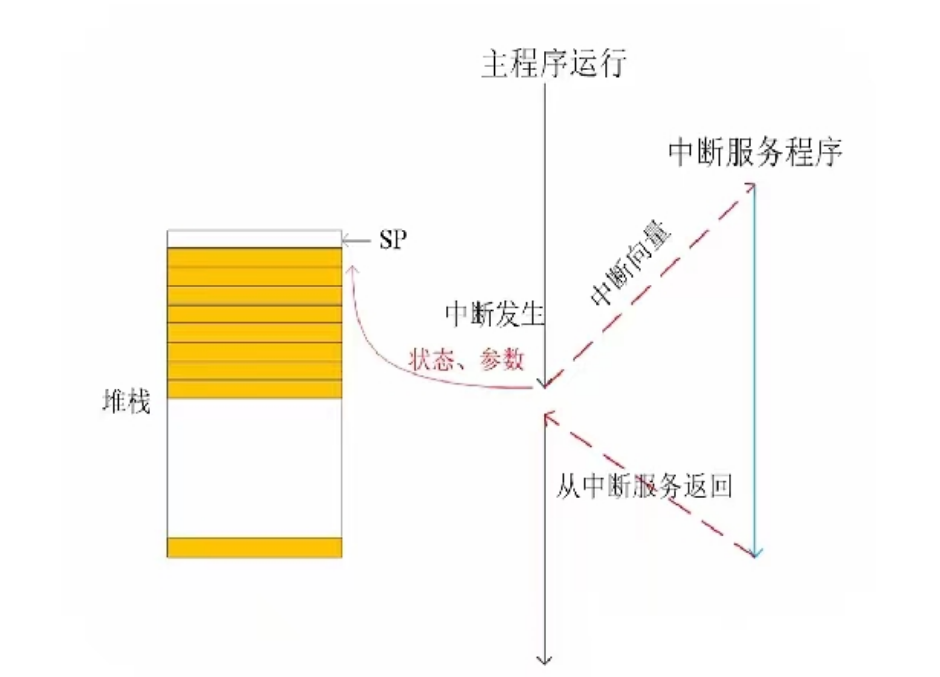

Figure 2 Interrupt Flowchart

[Entering Interrupt]

The processor automatically saves the context to the stack {PC, xPSR, R0-R3, R12, LR}. Once the stack operation is complete, the ISR can begin execution.

[Exiting Interrupt]

The context before the interrupt is automatically restored from the stack; once the stack operation is complete, execution of the interrupted instruction continues; the stack operation can also be interrupted, allowing for a new interrupt to be responded to without saving the context.

R0 – R12

R13 Stack Pointer SP: points to the top address of the stack

R14 Link Register LR: stores the return address

R15 Program Counter PC: saves the address of the instruction to be executed

[Detailed Process]

1. Interrupt request triggers: An external device or internal module issues an interrupt request, notifying the processor that a specific event has occurred. Interrupt detection and response: The processor detects the interrupt request at the appropriate time and determines whether to respond to the interrupt based on the interrupt controller’s settings. If the interrupt is allowed and has a higher priority, the processor will halt the current task and handle the interrupt event.

2. Save context: Before handling the interrupt, the processor needs to save the context information of the current task to correctly restore the interrupted task after the interrupt handling is completed. Context information includes the program counter (PC), register contents, etc.

3. Interrupt vector lookup: The processor uses the interrupt vector table (or interrupt vector address table) to determine the address of the interrupt handler. The interrupt vector table is a data structure that stores the addresses of interrupt handlers, finding the corresponding interrupt handler address based on the interrupt number or interrupt source identifier.

4. Execute interrupt handler: The processor jumps to the address of the interrupt handler to start executing the interrupt handling code. The interrupt handler is responsible for performing operations specific to the interrupt, such as reading data from external devices, updating status, triggering other tasks, etc. After handling the interrupt: When the interrupt handler completes related operations, the processor performs corresponding cleanup tasks, including clearing the interrupt flag and restoring the saved context information.

5. Restore context: The processor uses the previously saved context information to restore the state of the interrupted task. This includes restoring the program counter, register values, etc., to ensure that the task can continue execution from where it was interrupted.

6. Resume execution: After restoring the context of the interrupted task, the processor resumes executing the interrupted task, continuing the code flow that was interrupted.

It is important to note that the specific interrupt handling process may vary depending on the processor architecture, operating system, and application. The above steps provide a general outline of the basic process of interrupt handling.

Figure 3 Interrupt Architecture Diagram

This concludes our Little Science Gas Station today!

Now let’s focus on the technology hotspots~~

Global Technology Hotspots

Facts themselves can and should provide us with scientific knowledge.

——Einstein

Elon Musk claims his brain-computer interface company has completed its first human brain device implantation surgery

Source: The Paper | January 30, 2024, 09:57

1

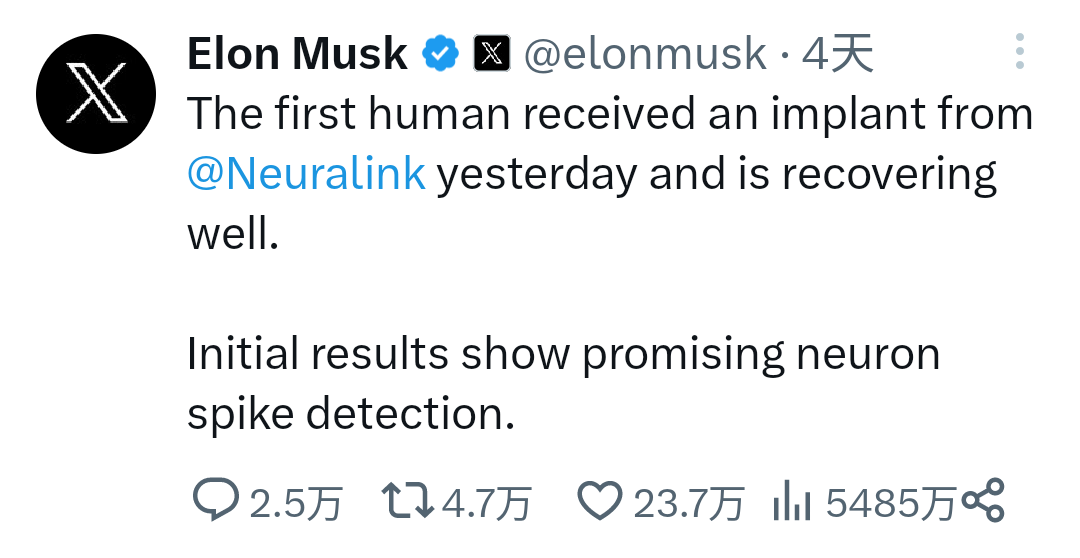

According to Global Times citing Bloomberg, Elon Musk, co-founder of OpenAI, stated that his brain-computer interface company, Neuralink, has completed its first human brain device implantation surgery on January 29. Musk recently posted on social media platform X that, “Yesterday, the first human patient received an implantation surgery from Neuralink, and is currently recovering well. Preliminary results show promising neuron spike detection.”

Figure 2.1 Musk’s post on social media platform X

Neuralink applied for human trials in 2022 but did not receive approval from the U.S. Food and Drug Administration due to concerns about the safety of brain-implant trials.

In May 2023, Neuralink received FDA approval to begin its first clinical trial of brain implant devices. The company also announced on its official blog that it had been approved to start recruiting volunteers, stating that those with quadriplegia due to neck spinal cord injury or amyotrophic lateral sclerosis (commonly known as ALS) might qualify for recruitment.

Neuralink announced in September 2023 that it had begun implantation trials. The company stated that during the study, its developed robot would implant “ultra-thin” wires to help transmit signals in the brains of trial participants.

Neuralink hopes that by implanting electrodes, chips, and other devices into the human brain, it can establish communication and control channels between the human brain and external devices, i.e., brain-computer interfaces, allowing for direct control of external devices using bioelectric signals from the brain or regulating brain activity through external stimuli. If successful, this technology could benefit patients with visual or motor disabilities.

One arrow, eleven stars! Long March 2C rocket sets record for multiple satellite launches

Source: Science and Technology Daily | February 3, 2024, 10:23:50

2

At 7:37 AM on February 3, the Long March 2C carrier rocket, developed by the China Aerospace Science and Technology Corporation, successfully launched from the Xichang Satellite Launch Center, successfully sending the Geely Constellation 02 group of satellites into their designated orbit.

This launch of eleven satellites with one arrow is the largest number of satellites launched in a single mission by the Long March 2C rocket.

To meet the requirements of launching eleven satellites with one arrow, the design team optimized satellite layout to efficiently use the rocket fairing space, ensuring safe and reliable satellite separation, thus enhancing the rocket’s mission adaptability.

The Geely Constellation 02 group of satellites can provide satellite application services to global users, empowering automotive autonomous driving and intelligent networking in the automotive field through integrated communication, navigation, and remote sensing technologies.

Global Technology Weekly

Written by | Xin Bingjie, Tao Jingong

Typeset by | Tao Jingong

Reviewed by | Lai Hengyi, Liu Mohan

Guided by | Sun Pengbo