Follow+Star PublicNumber, don’t miss out on exciting content

Author | strongerHuang

WeChat Public Account | Embedded Column

If the CPU has no interrupts, can you imagine what it would be like?

It would just be a while loop, unable to handle tasks in a timely manner, let alone have the current RTOS (RTOS also requires interrupts to be realized).

Next, let’s talk about the interrupts of Cortex-M and the principles of FreeRTOS interrupt priority configuration.

1About Cortex-M3 Processor

Before writing this article, let’s write some relevant extended content, this article combines the core of Cortex-M3 with STM32 for discussion.

Cortex-M3 is just a core of STM32F1. Conversely, STM32F1 is a chip that adds some peripherals (such as: USART, AD, etc.) based on Cortex-M3.

2Cortex-M Interrupt Control

NVIC: Nested Vectored Interrupt Controller, that is, the nested vector interrupt controller.

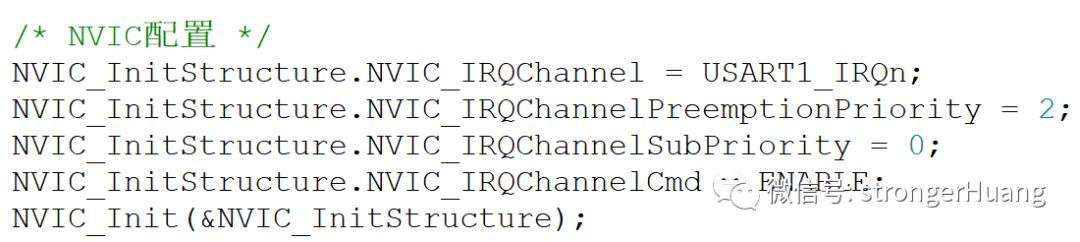

We are quite familiar with NVIC in STM32, when programming we always configure NVIC when using interrupts.

And the NVIC in STM32F1 is part of Cortex-M3, not a peripheral added by STM32.

NVIC vector interrupt controller is an inseparable part of Cortex‐M3, it is tightly coupled with the CM3 core logic, with some parts even intertwined.

Therefore, the NVIC related registers are located in the Cortex-M manual. To discuss STM32’s interrupt control, we must start with the NVIC of Cortex-M3.

2. Difference Between Interrupts and Exceptions

So:

1. From the perspective of Cortex‐M3 core, interrupts like USART in STM32 are considered external interrupts.

2. From the perspective of STM32, EXTI external pin interrupts are considered interrupts.

3. Priority

Tip:

1.In STM32, the smaller the interrupt priority value, the higher the priority.

2.Priority grouping: Cortex-M3 and M4 have grouping functions, meaning there are preemptive priorities and response priorities, as shown below:

Some cores do not have this function, such as Cortex-M0.

3. Reference Material

You can refer to “Cortex-M3 Authority Guide”

STM32’s core programming manual:

http://www.st.com/stonline/products/literature/pm/15491.pdf

3FreeRTOS Interrupt Priority Configuration

This section discusses the maximum interrupt priority configuration problem of FreeRTOS, that is, in the FreeRTOSConfig.h configuration file:

configMAX_SYSCALL_INTERRUPT_PRIORITY

Do you know the meaning of the configured value? Here, it is necessary to understand in conjunction with NVIC related content.

For more information about FreeRTOS maximum priority configuration, you can refer to:

https://www.freertos.org/RTOS-Cortex-M3-M4.html

Reply in the background “Cortex-M” “STM32” “FreeRTOS” to read more related articles.

Click “Read the Original” to see more shares, welcome to share, collect, like, and look.