Introduction

During the project development process, it was found that the actual baud rate configured for the MCAL SPI did not match the clock frequency captured by the logic analyzer. The actual frequency was only half of the configured value. This article documents the troubleshooting process for this issue.

MCAL Configuration Check

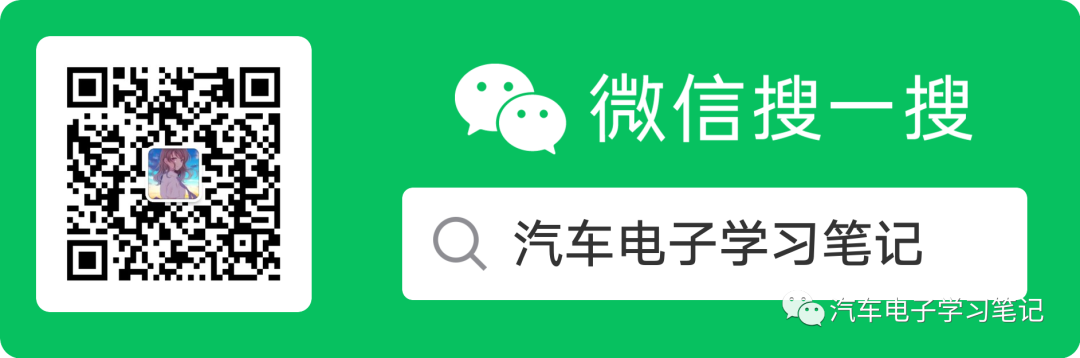

The baud rate for the MCAL SPI is configured in the ExternalDevice, as shown below  . To calculate the baud rate, it is necessary to associate it with the SPI clock, which is configured in the SpiyPhyUnit

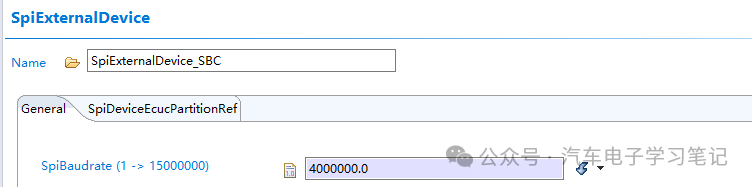

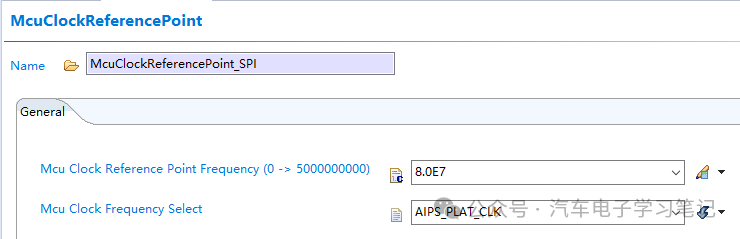

. To calculate the baud rate, it is necessary to associate it with the SPI clock, which is configured in the SpiyPhyUnit  . This reference clock is configured in the MCU, as shown below, with the clock being AIPS_PLAT_CLK, and the clock frequency configured to 80M

. This reference clock is configured in the MCU, as shown below, with the clock being AIPS_PLAT_CLK, and the clock frequency configured to 80M . The clock is derived from PLL_PHI0_CLK. Currently, the configuration seems fine, and there were no errors during code generation. Therefore, it is necessary to check the chip manual for the SPI Clock Source.

. The clock is derived from PLL_PHI0_CLK. Currently, the configuration seems fine, and there were no errors during code generation. Therefore, it is necessary to check the chip manual for the SPI Clock Source.

SPI Clock Source

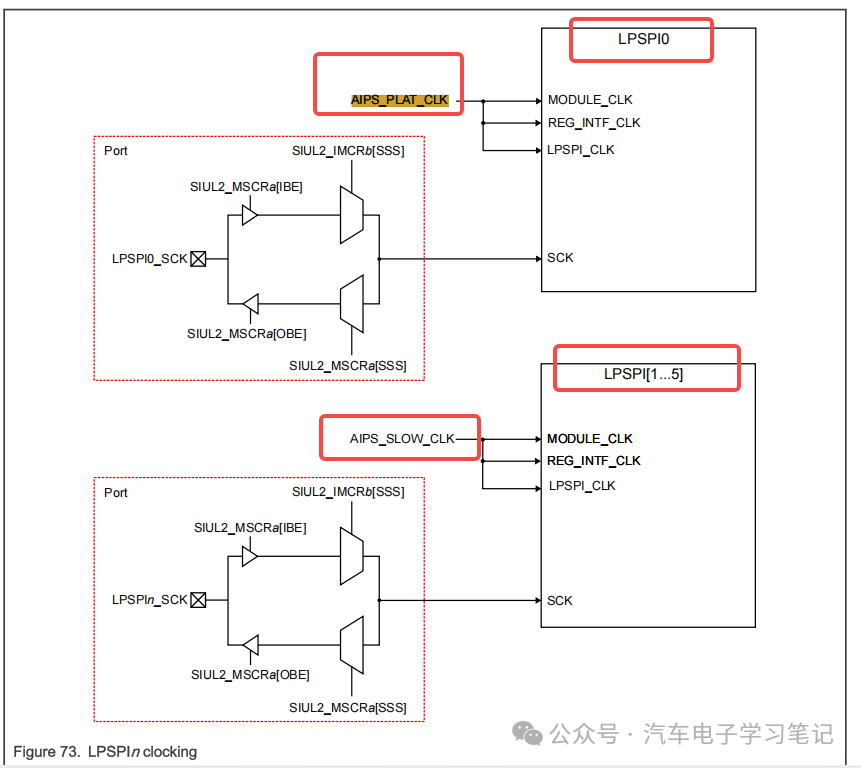

The SPI clock source is shown in the manual as follows:

Only the SPI0 clock comes from AIPS_PLAT_CLK, while the clocks for other SPI modules come from AIPS_SLOW_CLK, which is only half of the AIPS_PLAT_CLK. Therefore, the issue is easily explained: we are using SPI1. Although the clock associated in MCAL is AIPS_PLAT_CLK, the actual clock used is AIPS_SLOW_CLK, resulting in the final SPI clock being only half of the configured value

Issue Resolution

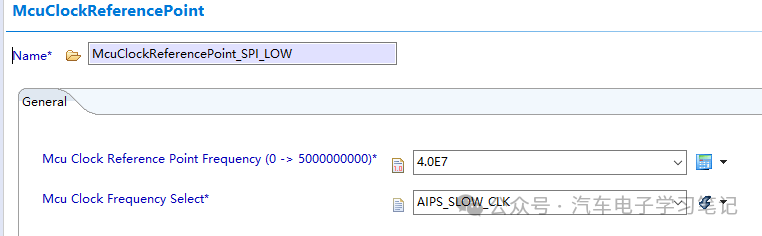

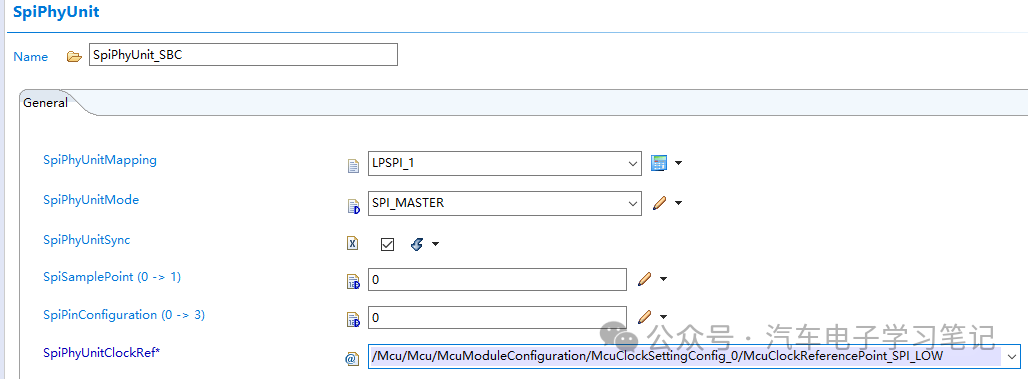

If you do not want to change the clock configuration, you can temporarily increase the baud rate configuration to twice the desired value. However, it is best to modify the clock configuration to associate the PhyUnit clocks of SPI1-SPI5 with AIPS_SLOW_CLK, which will also make it easier for others to understand and avoid ambiguity

Conclusion

Many peripherals in the S32K3 have similar characteristics, where the first peripheral has the strongest performance. For example, the previously encountered CAN0 supports more Mailboxes than other CAN channels. This time, the SPI clock source is also the case, where only SPI0 has the highest clock frequency. Therefore, when selecting chips in the future, the differences in peripherals must be fully considered!