SiFive’s Best Processor Portfolio

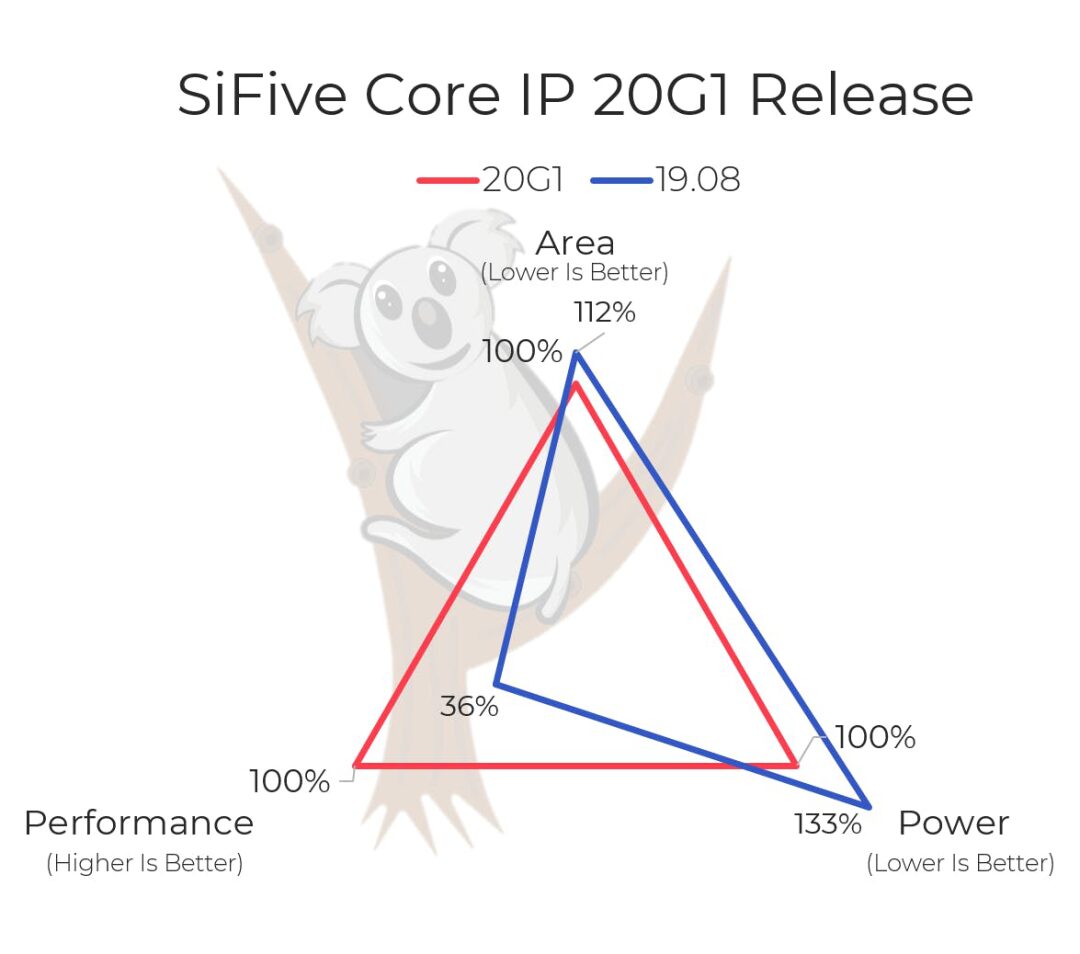

We are excited to announce that the SiFive 20G1 version has undergone a comprehensive update and upgrade to its RISC-V IP portfolio. The release of version 20G1 brings enhancements and new features to the SiFive Core IP, which is the most widely used RISC-V IP portfolio in the industry. This portfolio ranges from the ultra-high-performance U7 series to the popular E2 series processors, providing up to 2.8 times performance improvement (1); power consumption reduced by up to 25% (2); and area reduced by up to 11% (3).

Setting Standards for RISC-V Cores

SiFive was founded by the inventors of RISC-V, offering processor cores based on the open-source RISC-V architecture, with the mission of enabling the development of domain-specific chips. SiFive combines market feedback gained from customer experiences to identify all the components that processor cores must include and develops the necessary software for CPUs with integration and security in mind — this is also the reason for the previous releases of SiFive Shield and SiFive Insight.

Accelerating Product Development

SiFive Insight is the industry’s first pre-integrated debug and trace IP for RISC-V processor cores, enabling faster chip design, hardware-software integration, and application development.

Notably, SiFive Insight is compatible with Arm® CoreSight™. By seamlessly integrating with Arm® CoreSight™, developers can integrate SiFive RISC-V based cores into mixed ISA designs while maintaining their existing development environments. SiFive Insight has received broad industry support from leading software companies such as Green Hills Software, IAR Systems, Lauterbach, SEGGER, and the free tools from SiFive Freedom Studio.

High Performance, High Efficiency Processor Cores

In the SiFive 20G1 version, the SiFive Core IP has been enhanced to improve power, performance, and area (PPA). The enhanced features of the high-performance U7 series application processors have reduced power consumption by over 25% (2), while increasing load bandwidth in streaming data applications (such as AI acceleration applications) by 2.8 times (1).

SiFive E3 and E7 series now support the RISC-V “embedded” extension RV32E, which reduces area by up to 11% (3) compared to RV32I, further improving the core’s PPA. According to customer feedback, RV32E will be a very popular choice for product designers of high-performance embedded CPUs with area constraints. The SiFive 3 series, 5 series, and 7 series cores have been updated with entirely new enhanced real-time capabilities, bringing deterministic performance for high-reliability designs.

SiFive’s advanced platform engineering expertise enables our roadmap development to quickly integrate and validate on FPGAs, allowing rapid testing of improvements and new features across the product line. To achieve a high-performance software development platform, the SiFive customer software package includes FPGA bitstream, currently featuring the Xilinx UltraScale+ FPGA series VCU118, providing a software development platform for the entire SiFive Core IP product portfolio, including large-scale multicore configurations.

The award-winning cloud-based application SiFive Core Designer is closely integrated with the SiFive 20G1 version, allowing you to configure your own processor core, making SiFive Core IP simple to use. In the SiFive 20G1 version, we adopted a new versioning scheme, changing the naming from “year/month” to “year/release.” The SiFive 20G1 version is the first general release of 2020, representing nine months of hard work from SiFive, and we have established a new release schedule that aligns with our customers’ development cycles. SiFive Core Designer allows chip designers to fine-tune SiFive processors to select the desired features and functions to meet their workload requirements.

SiFive Shield is an open, extensible platform architecture designed to enhance the security of the entire SoC for RISC-V, and it has been pre-integrated into SiFive Core IP and configured through SiFive Core Designer. The SiFive 20G1 version adds support for the SiFive Shield hardware cryptography accelerator (HCA) IP add-on option.

SiFive HCA IP offers a configurable combination of AES, SHA, and TRNG functions to achieve secure “foundational security” and hardware-accelerated encryption capabilities. SiFive Shield HCA is configured using the SiFive Core Designer platform and is delivered alongside SiFive Core IP (including accompanying documentation, software, and drivers) with pre-integration and validation.

Developing Excellent Applications

In discussions with customers about software, we are often first asked about support for the FreeRTOS™ real-time operating system. Support for FreeRTOS on RISC-V has been integrated since the official FreeRTOS release in early 2019, and now the source code and build scripts for FreeRTOS v.10 have been integrated into the SiFive Freedom E SDK. In addition to the FreeRTOS kernel, the SiFive Freedom E SDK includes several FreeRTOS-based examples, including enabling secure runtime operation using Physical Memory Protection (PMP).

The SiFive Freedom E SDK board support package (BSP) has been upgraded to include system view description (SVD) files for better integration into debugging environments.

SiFive Freedom Studio accelerates debugging speed by enhancing support for SiFive Insight’s advanced tracing and debugging (including new views for trace streams), thereby speeding up new product development.

SiFive’s Best Product Portfolio is Here

The SiFive 20G1 version combines new pre-integrated SiFive Insight trace and debug features, with impressive improvements in PPA, saving customers significant time and effort. By leveraging SiFive’s unique support for Arm® CoreSight™, we minimize disruptions in the workflow and provide extensive tool ecosystem support, enabling the definition and adoption of high-performance, high-efficiency, secure RISC-V processors and SiFive Shield security features and add-on options for your next-generation applications and real-time SoCs. With SiFive, everything is compelling.

We are eager to work with customers to help them leverage the current SiFive Core IP product portfolio, which boasts faster, more efficient, and more powerful new capabilities to create amazing products.

If you want to learn more about the SiFive 20G1 version directly, please contact us.

(1) Based on internal engineering measurements from SiFive, memory-intensive workloads running on SiFive U7 series processor cores achieved a performance increase of 2.8 times. Under normalized conditions, the performance of SiFive U7 series processor (20G1) is 2.8 times that of SiFive U7 series processor (19.08).

(2) Based on internal engineering measurements from SiFive, the core power consumption of SiFive U74 processor (20G1) is 25% lower than that of SiFive U74 processor (19.08) when running the Dhrystone benchmark.

(3) Based on internal engineering measurements from SiFive, under a 28nm process, compared to RV32I, the area of the SiFive E3 series using the RISC-V embedded extension RV32E is reduced by 11%.

Arm and CoreSight are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the United States and/or other countries.

This article is sourced from the SiFive website and is reproduced here after translation, intended to convey more information; copyright belongs to the original author.