Access, Inspect, and Control

The term “debug” has a legendary history. According to various sources, the word debug was coined in 1945 by computer pioneer and U.S. Navy Rear Admiral Grace Hopper when she removed a moth from the Harvard Mark II computer. The use of the word bug can also be traced back to a letter from the great inventor Thomas Edison in 1878. Regardless of where the word originated, we do not want bugs in our systems, hardware, and code.

As the size of computer systems has long surpassed the limits of physical inspection, programming with wires or punch cards has become obsolete, necessitating new methods. We need to gain insights into the machines, the code, and the millions of calculations happening every second in front of us to accurately and quickly create high-quality products.

Industry-Leading RISC-V Trace and Debug Toolkit

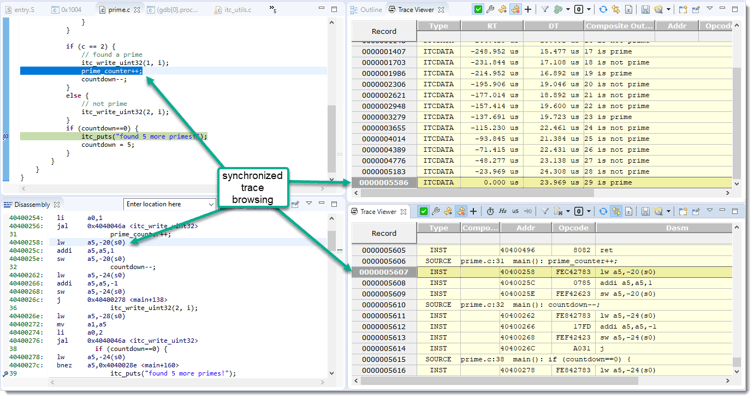

Let’s talk about SiFive Insight, a combination of trace, debug IP, software, and tools that makes the development of new SiFive RISC-V products efficient and straightforward. Inspecting product operations is crucial for developing safe and efficient systems. These trace and debug features allow access to system state information and even modifications to better understand the system’s operational flow.

It features the ability to trace processor instruction execution step-by-step and check debug log contents, providing us with the capability to inspect, access, and control system operations during development.

SiFive Insight is the first solution to integrate debug and trace within RISC-V cores. It is a single-vendor solution aimed at reducing the complexity of the entire process and is very lightweight, helping our customers integrate SiFive RISC-V processor core IP into SoC designs. Notably, SiFive Insight also supports Arm® Coresight™, making it equally easy to use in heterogeneous SoC development environments.

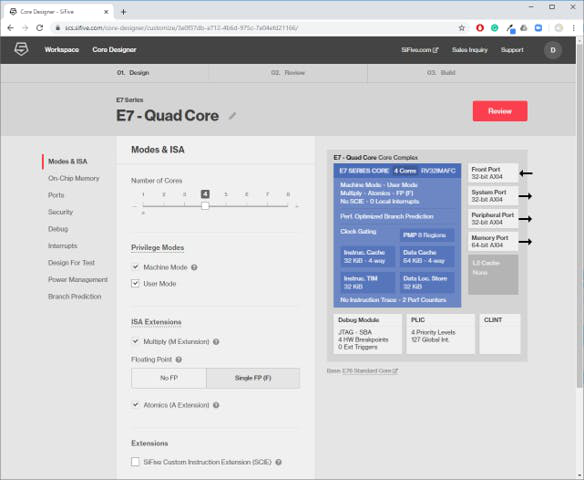

SiFive Insight is pre-integrated and validated with the CPU to provide a range of standard debug and trace functionalities. From run control to advanced multicore trace in heterogeneous core complexes, SiFive Insight can be easily configured on the award-winning SiFive Core Designer platform to meet your needs.

All SiFive cores have the capability to configure up to 16 hardware triggers. Hardware triggers can pause the processor when executing instructions or reading/writing memory locations. Additionally, hardware triggers can be used to control trace collection. These triggers can be combined to support any range. Besides core triggers, SiFive Insight also supports a configurable number of external triggers, allowing external events to trigger a debug halt command.

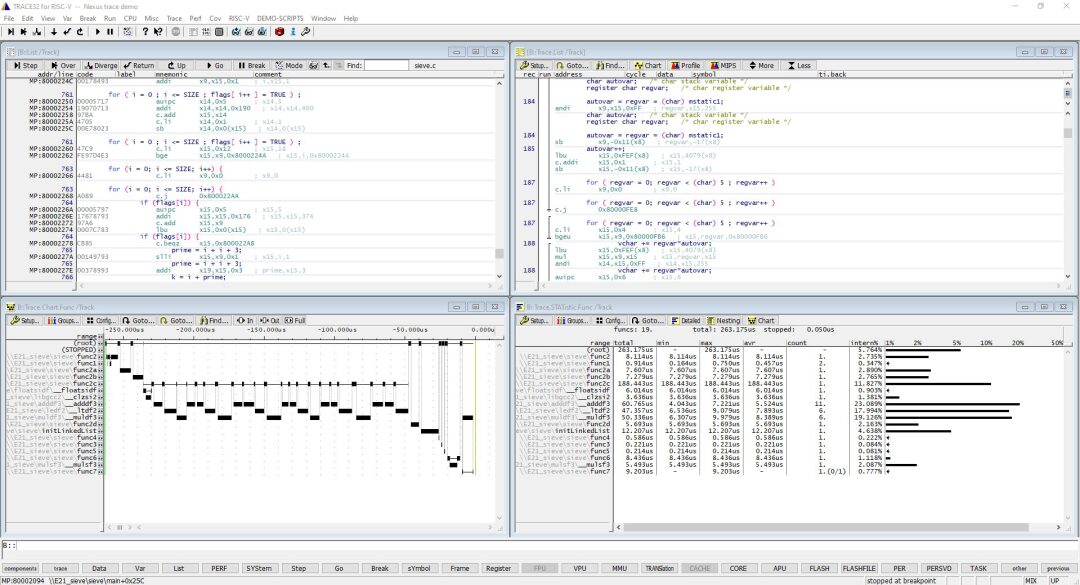

SiFive Insight is compatible with the Nexus 5001™ trace specification and has full support from the SiFive Freedom Studio Integrated Development Environment (IDE). Compatibility with Nexus 5001™ trace also ensures compatibility with leading development tools. SiFive cores support the released RISC-V Processor Trace standard. The RISC-V Foundation’s trace and debug working group is evaluating the approval of Nexus 5001™ trace as an additional standard. SiFive works closely with our ecosystem partners to enable them to utilize the latest SiFive Insight technology, ensuring they can well support application developers and chip designers.

IAR Systems

Lauterbach

SEGGER

SEGGER Microcontroller GmbH indicates that SEGGER J-Link provides comprehensive support for the new SiFive Insight’s debug and trace IP, including implementations based on Nexus trace features. Using SEGGER J-Link, trace data can be read from on-chip memory, generating backtrace, execution counts, code analysis, and code coverage information.

Market Dynamics

According to industry analysts’ forecasts, 62.4 billion RISC-V cores will be deployed over the next five years. SiFive’s product portfolio, tools, and expertise will ensure that customers develop market-centric products safely, efficiently, and without bugs.

Start using SiFive cores IP with SiFive Insight features that can be configured on SiFive Core Designer to help you develop the next safe, efficient, high-performance SoC. We have an industry-leading standard core series that can quickly configure customized cores based on your needs, ranging from small 32-bit cores for embedded applications to 64-bit application processor cores with high-performance architectures.

This article is sourced from the SiFive Blog, author: James Prior, translated and reprinted to convey more information, copyright belongs to the original author.