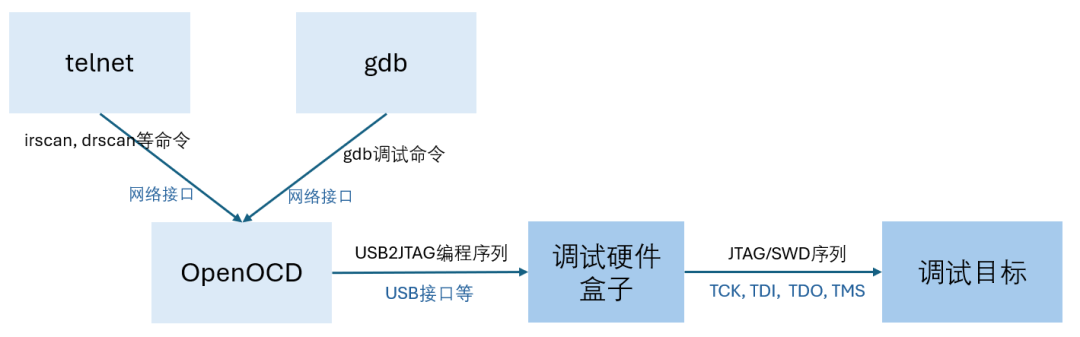

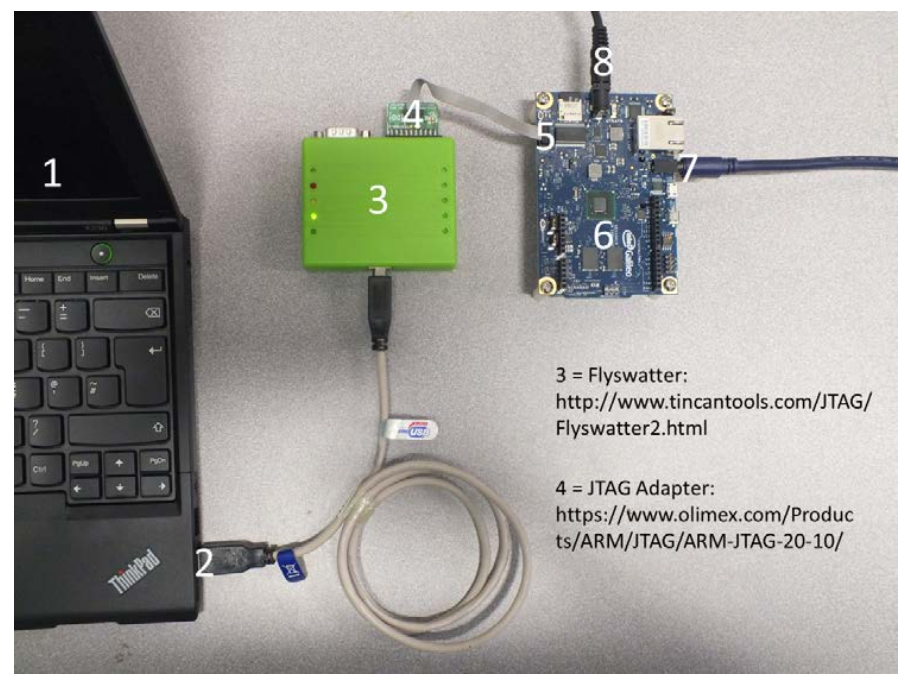

OCD stands forOn-Chip Debugger, which is on-chip debugging. OpenOCD is an open-source JTAG debugging tool that operates as follows: The following diagram shows a physical connection, where the debugging target is theIntel Galileo Board, and the hardware box is the Flyswatter. The small board labeled 4 is theARM-JTAG-20-10 Adapter:

The following diagram shows a physical connection, where the debugging target is theIntel Galileo Board, and the hardware box is the Flyswatter. The small board labeled 4 is theARM-JTAG-20-10 Adapter: When starting OpenOCD, a configuration file is passed in:

When starting OpenOCD, a configuration file is passed in:

openocd -f flyswatter2.cfg -f quark_x10xx_board.cfgTo successfully run OpenOCD on the debugging target, it is crucial to select the appropriate configuration. The content of the above flyswatters.cfg is as follows, and its meaning is not difficult to understand:

adapter driver ftdiftdi device_desc "Flyswatter2"ftdi vid_pid 0x0403 0x6010

ftdi layout_init 0x0538 0x057bftdi layout_signal LED -ndata 0x0400ftdi layout_signal nTRST -data 0x0010ftdi layout_signal nSRST -data 0x0020 -noe 0x0100The quark_x10xx_board.cfg references another file through source:

source [find target/quark_x10xx.cfg]

#default frequency but this can be adjusted at runtimeadapter speed 4000

reset_config trst_only

The content of thisquark_x10xx.cfg file is as follows:

# SPDX-License-Identifier: GPL-2.0-or-later

if { [info exists CHIPNAME] } { set _CHIPNAME $CHIPNAME} else { set _CHIPNAME quark_x10xx}

if { [info exists ENDIAN] } { set _ENDIAN $ENDIAN} else { set _ENDIAN little}

if { [info exists CPUTAPID] } { set _CPUTAPID $CPUTAPID} else { set _CPUTAPID 0x18289013}

jtag newtap quark_x10xx cpu -irlen 8 -irmask 0xff -expected-id $_CPUTAPID -disablejtag newtap quark_x10xx cltap -irlen 8 -irmask 0xff -expected-id 0x0e681013 -enable

#openocd puts tap at front of chain not end of chainproc quark_x10xx_tapenable {} { echo "enabling core tap" irscan quark_x10xx.cltap 0x11 drscan quark_x10xx.cltap 64 1 runtest 10}

proc quark_x10xx_tapdisable {} { echo "disabling core tap" irscan quark_x10xx.cltap 0x11 drscan quark_x10xx.cltap 64 0 runtest 10}

proc quark_x10xx_setup {} { jtag tapenable quark_x10xx.cpu}

jtag configure $_CHIPNAME.cpu -event tap-enable \ "quark_x10xx_tapenable"

jtag configure $_CHIPNAME.cpu -event tap-disable \ "quark_x10xx_tapdisable"

set _TARGETNAME $_CHIPNAME.cputarget create quark_x10xx.cpu quark_x10xx -endian $_ENDIAN -chain-position quark_x10xx.cpu

jtag configure $_CHIPNAME.cpu -event setup \ "quark_x10xx_setup"

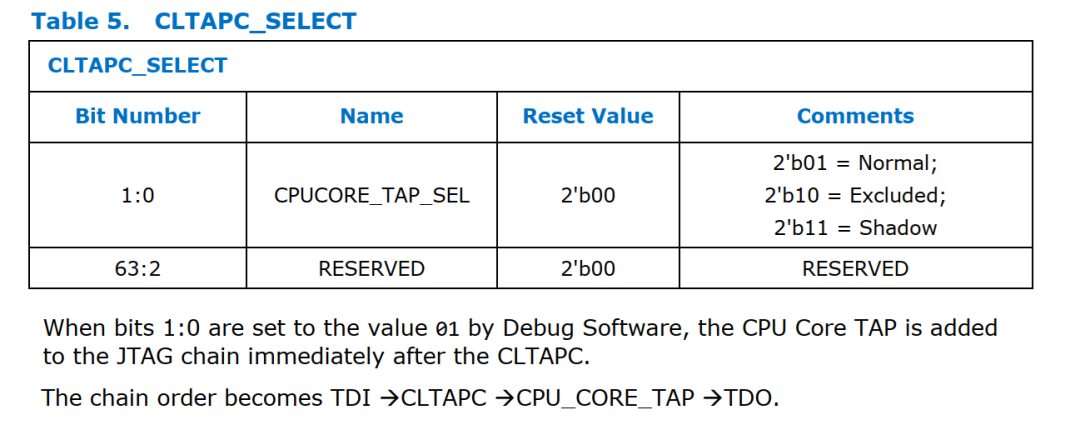

Among them, newtap defines two TAPs:

- quark_x10xx.cltap

- quark_x10xx.cpu

jtag newtap quark_x10xx cpu -irlen 8 -irmask 0xff -expected-id $_CPUTAPID -disablejtag newtap quark_x10xx cltap -irlen 8 -irmask 0xff -expected-id 0x0e681013 -enableThe following few lines define the procs executed when enabling, disabling, and setting up the TAP quark_x10xx.cpu:

jtag configure $_CHIPNAME.cpu -event tap-enable \ "quark_x10xx_tapenable"

jtag configure $_CHIPNAME.cpu -event tap-disable \ "quark_x10xx_tapdisable" jtag configure $_CHIPNAME.cpu -event setup \ "quark_x10xx_setup"The following defines the debugging target:

target create quark_x10xx.cpu quark_x10xx -endian $_ENDIAN -chain-position quark_x10xx.cpuThis debugging target, after creation, will call its setup when used, and the setup proc is to call the TAP quark_x10xx.cpu’s tapenable proc:

proc quark_x10xx_setup {} { jtag tapenable quark_x10xx.cpu}

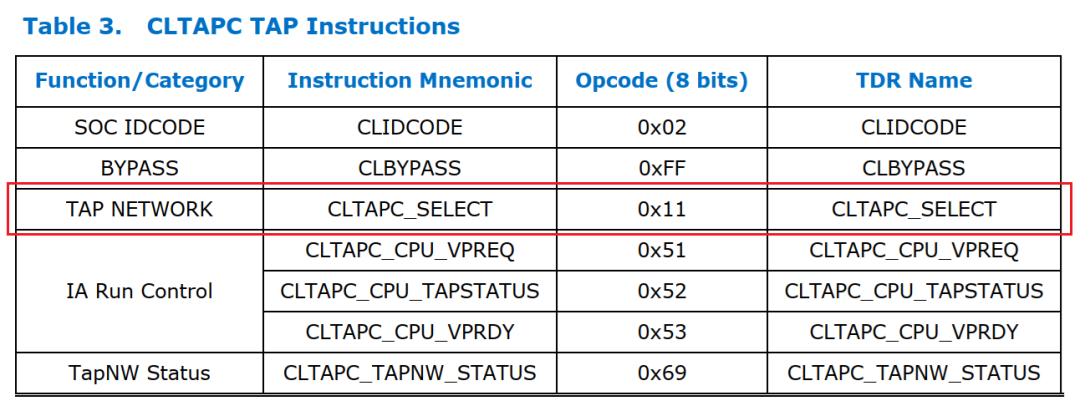

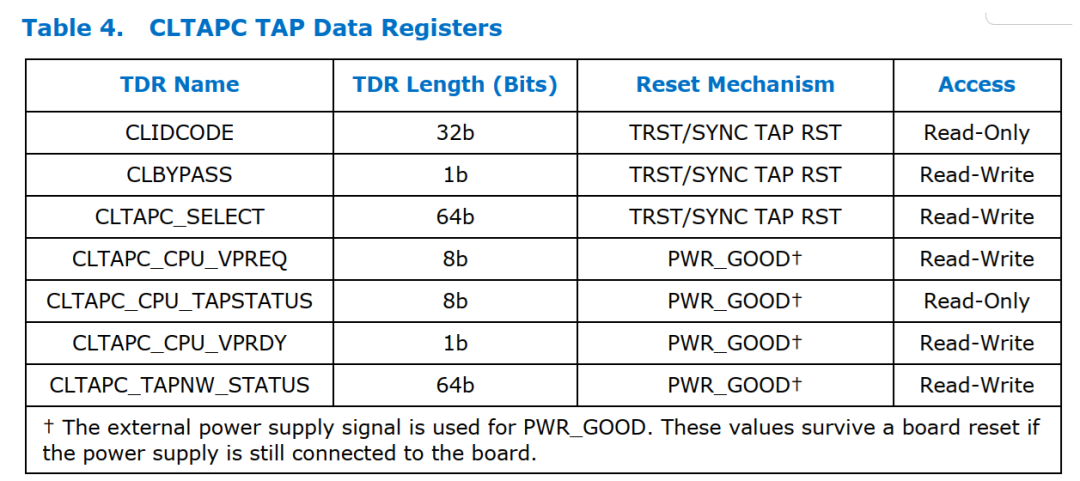

proc quark_x10xx_tapenable {} { echo "enabling core tap" irscan quark_x10xx.cltap 0x11 drscan quark_x10xx.cltap 64 1 runtest 10}The tapenable of quark_x10xx.cpu first setsquark_x10xx.cltap IR to 0x11, and then sets DR to 1. So 0x11 represents: It appears that CLTAP is a Center Level TAP, and through 0x11 CLTAPC_SELECT, the next level TAP can be selected.

It appears that CLTAP is a Center Level TAP, and through 0x11 CLTAPC_SELECT, the next level TAP can be selected. When DR CLTAPC_SELECT=1, it selects the CPU Core TAP, which is the TAP quark_x10xx.cpu, effectively establishing a debugging link to the CPU:

When DR CLTAPC_SELECT=1, it selects the CPU Core TAP, which is the TAP quark_x10xx.cpu, effectively establishing a debugging link to the CPU: