1. Development of the ARM Architecture

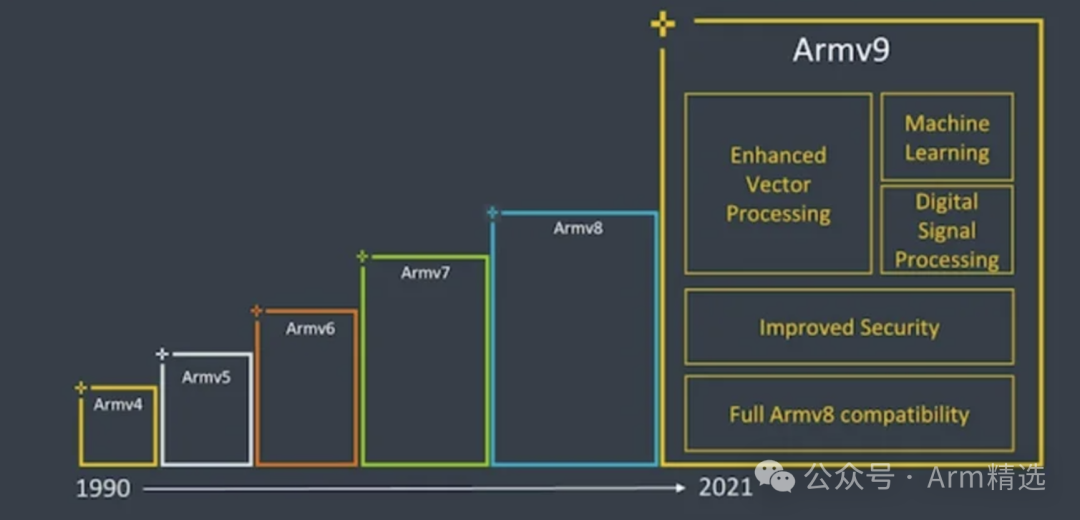

The ARM architecture (Advanced RISC Machine) is a microprocessor architecture based on the principles of Reduced Instruction Set Computing (RISC), originally designed and launched by the British Acorn Computer Company in the late 1980s. The evolution of the ARM architecture is as follows:

1.1. Early Development (1980s-1990s)

-

1985: Acorn began developing RISC-based processors to improve computer performance, launching the first ARM processor—ARM1. This processor was primarily used in the Acorn Archimedes computer.

-

1987: The ARM2 processor was released, offering improved performance over ARM1 and used in Acorn’s Archimedes series computers.

-

1990: Acorn established ARM Ltd., beginning to license the ARM architecture to other companies, paving the way for its commercialization.

1.2. Rapid Expansion (1990s-2000s)

-

1991: ARM launched the ARM6 series processors (such as ARM610, ARM620), which began to be applied in mobile phones and embedded devices.

-

1994: The ARM7 architecture was released, marking the successful application of ARM architecture in the low-power, high-performance embedded market. ARM7 series processors were widely used in mobile phones, game consoles, and home appliances.

-

1999: The ARM9 series was introduced, further enhancing performance and multi-core support, becoming a crucial foundation in the smartphone and consumer electronics sectors.

1.3. Expansion into Mobile Fields (2000s-2010s)

-

2000: ARM introduced the ARM10 architecture, with processors supporting higher clock frequencies and enhanced floating-point capabilities.

-

2005: Apple announced that its iPod used processors based on the ARM architecture, marking a significant milestone for ARM in consumer electronics.

-

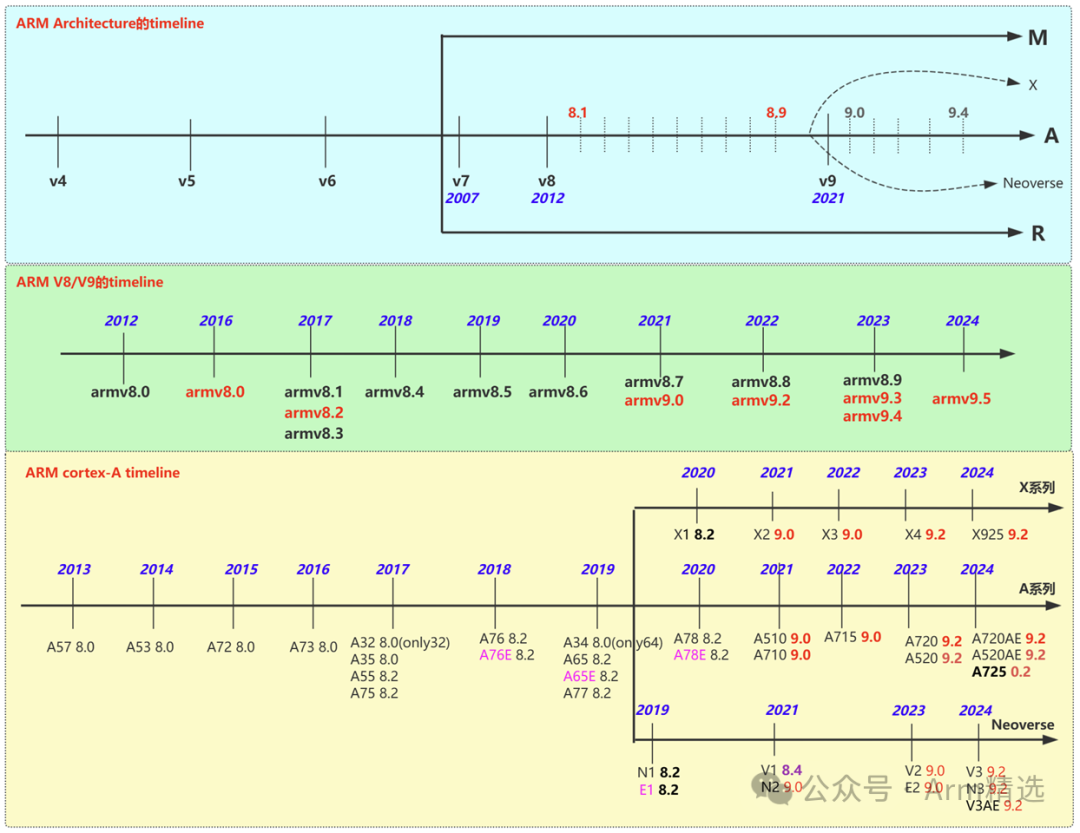

2007: ARM launched the Cortex-M and Cortex-A series processors, with the Cortex-A series primarily used in smartphones and high-performance computing devices, while the Cortex-M series was aimed at microcontrollers and low-power applications.

1.4. Dominance in Smartphones and Mobile Devices (2010s-Present)

-

2011: The ARM Cortex-A9 processor was widely used in smartphones, especially with Apple’s A-series chips adopting the ARM architecture. The high performance and low power characteristics of the ARM architecture made it the preferred processor architecture for mobile devices (such as smartphones and tablets).

-

2017: ARM introduced the Cortex-A75 and A55 architectures, further enhancing performance and energy efficiency, leading to widespread adoption in high-end smartphones and servers.

-

2020: ARM launched the Cortex-X series, designed for high-performance computing, further expanding into the data center and high-end computing markets.

1.5. Future Development and Ecosystem Expansion

2020s: ARM is increasingly applied in fields such as the Internet of Things, smart vehicles, cloud computing, and artificial intelligence. With NVIDIA’s planned acquisition of ARM (though not yet completed), ARM’s position in the global semiconductor supply chain is becoming increasingly important.

2. A64/A32/T32

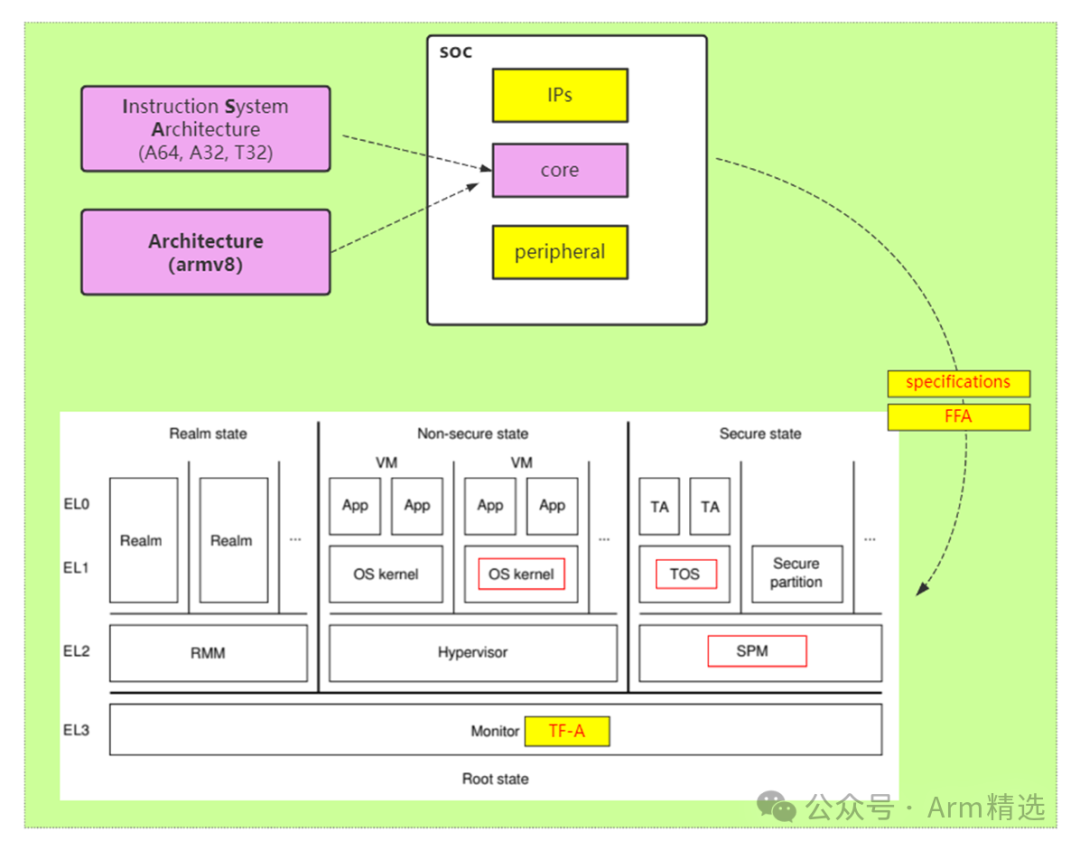

AArch64: Refers to the architecture

A64: Refers to the instruction set

arm64: Refers to the aarch64 system in the Linux Kernel

2.1. A64 Instruction Set (64-bit Instruction Set in ARMv8-A)

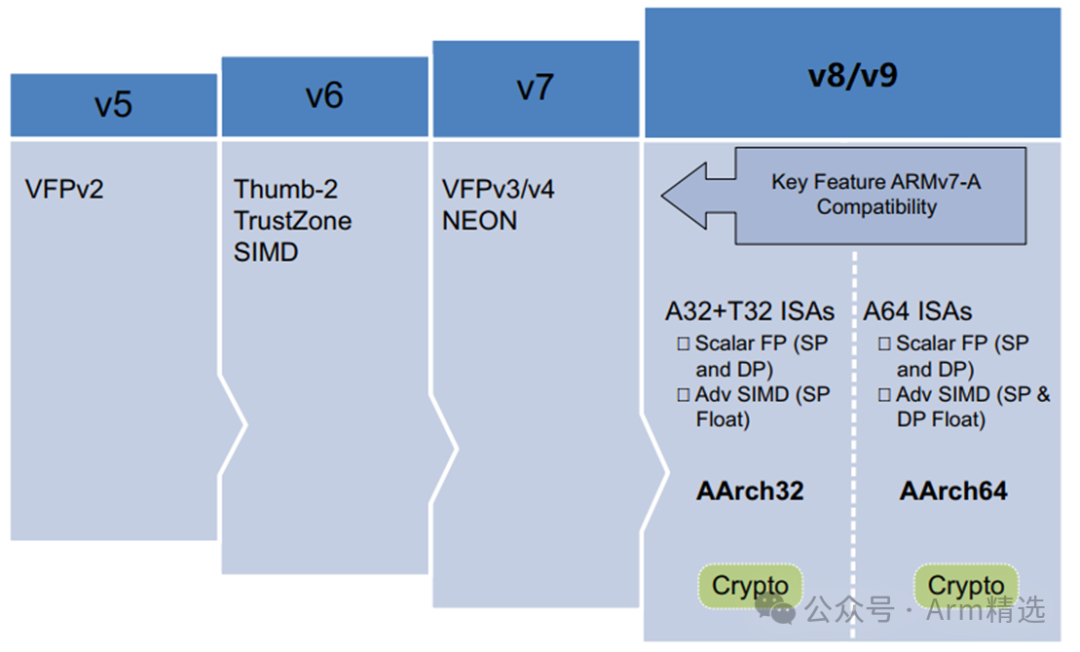

A64 is the 64-bit instruction set in the ARM architecture, first appearing in the ARMv8-A architecture. It is designed to provide higher performance and scalability.

-

64-bit Support: A64 supports 64-bit data processing, addressing, and register operations, capable of handling larger memory address spaces (up to 16 EB).

-

Compatibility: It is not compatible with ARMv7 and earlier 32-bit instruction sets, thus requiring specific support for backward compatibility (via A32 mode or providing a translation layer).

-

Performance Improvement: The A64 instruction set is optimized for performance, suitable for high-performance computing tasks such as servers, desktop computing, and high-end mobile devices.

-

Application Scenarios: The A64 instruction set is widely used in modern ARM64 processors, such as Apple’s A-series chips, Qualcomm’s Snapdragon 8 series, and many ARM-based servers and embedded devices.

2.2. A32 Instruction Set (32-bit Instruction Set in ARMv7 and Earlier)

A32 is the 32-bit instruction set in the ARM architecture, commonly referred to as the ARM (classic ARM instruction set). It primarily appears in ARMv7 and earlier versions of ARM processors.

-

32-bit Support: The A32 instruction set is designed for 32-bit, capable of handling memory address spaces within 4 GB.

-

Compatibility: The A32 instruction set is backward compatible, supporting 32-bit applications to run on ARMv7 and earlier ARM processors.

-

Wide Application: The A32 instruction set has lower power consumption and can execute relatively simple instructions, making it very popular in early embedded systems and smartphones.

-

Application Scenarios: The A32 instruction set is widely used in low-power, embedded, and smartphone devices. Many ARMv7-based processors (such as early Snapdragon and Exynos processors) utilize the A32 instruction set.

2.3. T32 Instruction Set (Thumb-2 Instruction Set)

The T32 instruction set is a hybrid 32-bit instruction set in the ARM architecture, also known as Thumb-2. It extends the A32 instruction set, providing a better balance between performance and code density.

3. Comparison Summary of AArch64 and AArch32

AArch64, 64-bit Execution State:

-

Provides 31 general-purpose 64-bit registers, with X30 used as the procedure link register.

-

Provides a 64-bit program counter (PC), stack pointer (SPs), and exception link register (ELRs).

-

Provides 32 128-bit registers for SIMD vector and scalar floating-point support.

-

Provides a single instruction set A64.

-

Defines the ARMv8 exception model with four exception levels, EL0 – EL3, providing an execution privilege hierarchy.

-

Supports 64-bit virtual addressing.

-

Defines many process state (PSTATE) elements containing PE state. The A64 instruction set includes instructions for directly manipulating various PSTATE elements.

-

Names each system register using a suffix that indicates the lowest exception level at which the register can be accessed.

AArch32, 32-bit Execution State:

-

Provides 13 general-purpose 32-bit registers, along with a 32-bit PC, SP, and link register (LR). LR also serves as the ELR and procedure link register. Some of these registers have multiple storage instances for different PE modes.

-

Provides an ELR for exceptions returning from Hyp mode.

-

Provides 32 64-bit registers for advanced SIMD vector and scalar floating-point support.

-

Provides two instruction sets, A32 and T32.

-

Supports the ARMv7-A exception model based on PE modes and maps it to the ARMv8 exception model based on exception levels.

-

Supports 32-bit virtual addressing.

-

Defines many process state (PSTATE) elements containing PE state. The A32 and T32 instruction sets include instructions for directly manipulating various PSTATE elements, as well as instructions for accessing PSTATE using the application state register (APSR) or current program status register (CPSR).

4. A Global Perspective: Should You Learn Assembly or Architecture First?

-

Those who learn assembly are just playing around.

-

When you look at a piece of assembly code, is it the assembly instructions you don’t understand? You should be confused by the architecture principles, hardware principles, and registers.

-

Who doesn’t know mov, str, ldr, add?

-

Considering the variant instructions, there are thousands of instructions; learn one or memorize one, and let me see.

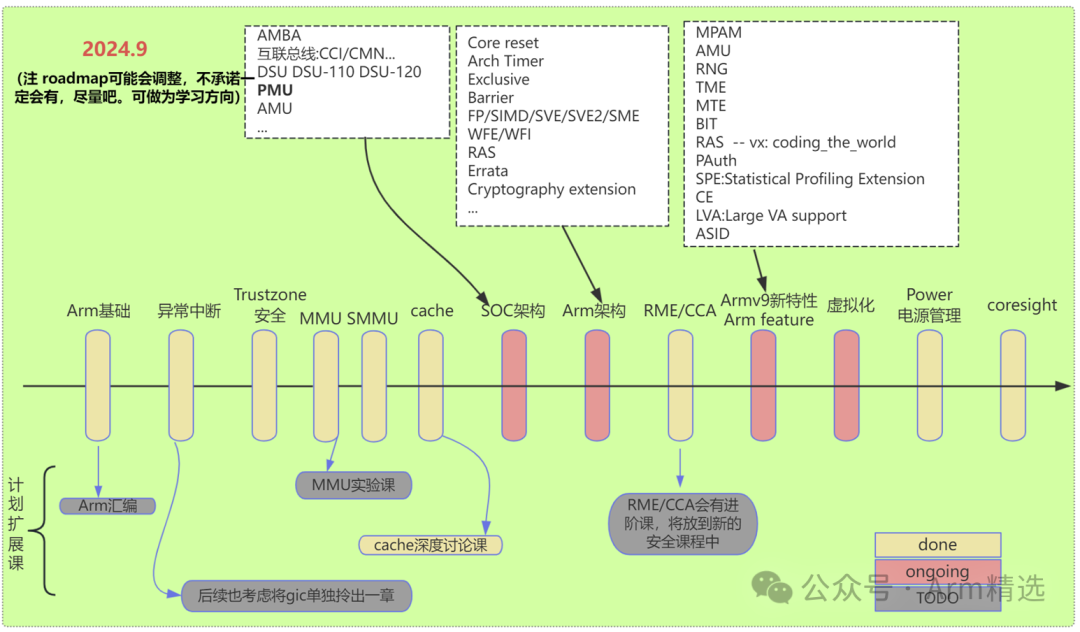

Learning Direction

| Recommended Courses | “From Beginner to Mastering Armv8/Armv9 Architecture” (Three Sessions) |

| “Trustzone/TEE/Security from Beginner to Master” Standard Edition | |

| Arm Selected – Platinum VIP Courses💋 All Courses | |

| 🌍Consult vx: sami01_2023 |