Skip to content

UART communication is an asynchronous communication method, where both the sender and receiver must communicate at an agreed baud rate. When there is an error in the baud rate, it can lead to communication errors. So, what factors can lead to errors in the baud rate?

1. Frequency Division Error

Firstly, the baud rate is generated based on the system clock division, and the relationship between the system clock and the baud rate may not be an integer multiple, so errors can occur during division. However, most MCUs currently have a relatively high system clock, generally in the tens of MHz, which is much greater than the baud rate for UART communication, so this error has a minimal impact.Assuming the MCU clock is 48MHz and the baud rate is 115200, 48MHz/115200=416.67. By dividing by 417, the actual baud rate becomes 48M/417=115108, resulting in an error of (115200-115108)/115200, approximately 0.08%. This error is very small and does not significantly affect UART communication.

However, when the system clock is relatively low, or the baud rate is relatively high, meaning the difference is not a large multiple, this error cannot be ignored.

For some older 51-core MCUs, due to low operating frequencies, using non-integer crystal oscillators (such as 11.0592M) is to minimize the division error when using common baud rates (such as 9600, 115200).

Secondly, the main error in baud rate still depends on the error of the system clock. So, how high are the requirements for clock error in UART communication?

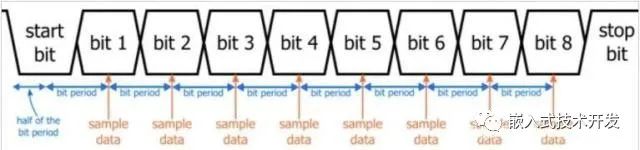

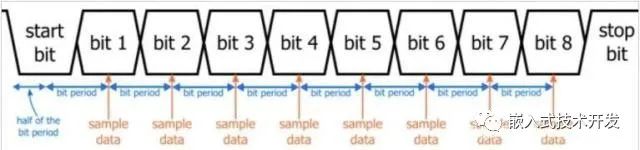

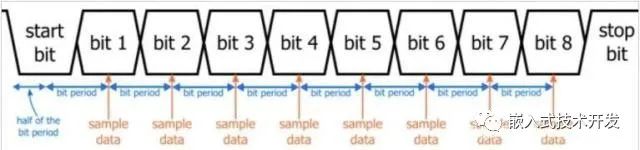

First, let’s look at the timing diagram for UART communication:

UART communication consists of a start bit, data bits, parity bit, and stop bit. Taking the common 8N1 as an example, it has 1 start bit, 8 data bits, no parity, and 1 stop bit. This means that transmitting one byte requires 10 bits. Each byte has a start bit for synchronization, so the error will only accumulate within one byte.

It is not difficult to see that the maximum error occurs during the sampling of the last bit, with an allowable extreme error of 0.5 bits. Calculating based on 10 bits per byte, the maximum allowable error is ±0.5/10=±0.05, or ±5%. Considering that UART communication involves both sending and receiving ends, it is best to control the error on each end to within ±2.5%.

When there are more data bits, parity bits, etc., the required clock accuracy becomes even higher. Considering the frequency division error mentioned above, generally speaking, when the clock error is less than ±2%, UART communication is relatively reliable.

Source: Embedded Technology Development

Copyright belongs to the original author. If there is any infringement, please contact for removal.

Be Cautious When Transitioning from Embedded Hardware to Software!

If a Programmer Goes to Jail, Will They Be Assigned to Write Code?

Why Are There More “Top Programmers” in Russia Than in China?

→ Follow to Stay Updated ←