Introduction: In the previous article (Architecture of LoRa IoT), we discussed the network structure of LoRaWAN. This article will focus on the end devices in the LoRaWAN network structure.

There are generally four ways to develop end devices.

1. Module

Pure RF module: Generally has an SPI interface and requires an external MCU, which eliminates the need for RF debugging.

AT command module: Uses serial AT commands, making it the simplest and most convenient to use.

2. Semtech LoRa Chips

Mainly the Semtech SX127x and SX126x series, differing in supported frequency bands, maximum transmission power, spreading factors, etc. An external MCU is required for RF debugging and software. The table below summarizes the main characteristics of these chips.

| Chip | Frequency | Spreading Factor | Bandwidth | Bit Rate | Max Sensitivity | Max Transmission Power | Receive Current |

|---|---|---|---|---|---|---|---|

| SX1276 | 137-1020MHZ | 6-12 | 7.8-500 kHz | 0.018-37.5 kbps | -148 dBm | +20 dBm | 9.9 mA |

| SX1277 | 137-1020MHZ | 6-9 | 7.8-500 kHz | 0.018-37.5 kbps | -139 dBm | +20 dBm | 9.9 mA |

| SX1278 | 137-525MHZ | 6-12 | 7.8-500 kHz | 0.018-37.5 kbps | -148 dBm | +20 dBm | 9.9 mA |

| SX1279 | 137-960MHZ | 6-12 | 7.8-500 kHz | 0.018-37.5 kbps | -148 dBm | +20 dBm | 9.9 mA |

| SX1261 | 150-960MHZ | 5-12 | 7.8-500 kHz | 0.018-62.5 kbps | -148 dBm | +15 dBm | 4.2 mA |

| SX1262 | 150-960MHZ | 5-12 | 7.8-500 kHz | 0.018-62.5 kbps | -148 dBm | +22 dBm | 4.2 mA |

| SX1268 | 410-810MHZ | 5-12 | 7.8-500 kHz | 0.018-62.5 kbps | -148 dBm | +22 dBm | 4.2 mA |

Official Semtech documentation: https://www.semtech.com/products/wireless-rf/lora-transceivers, and the open-source project on GitHub: https://github.com/Lora-net/LoRaMac-node, which includes schematics, software, etc.

3. LoRa SOC Chip STM32WL

The STM32WL system-on-chip integrates a general-purpose microcontroller and a sub-GHz wireless control unit on the same chip. The STM32WL microcontroller is built on the Arm® Cortex®-M4 core architecture and supports multiple modulation modes (LoRa®, (G)FSK, (G)MSK, and BPSK), ensuring flexibility for wireless applications using LoRaWAN® or any other suitable protocol in a completely open manner. The STM32WLE5 microcontroller meets the physical layer requirements of the LoRaWAN® specification published by the LoRa Alliance®. Its supported modulations, LoRa®, (G)FSK, (G)MSK, and BPSK, can also be used for traditional or proprietary protocols. The STM32WLE5 series features rich communication peripherals and characteristics, including up to 43 GPIOs, an integrated SMPS for optimized power consumption, and various low-power modes to maximize battery life. Dual power outputs and a wide linear frequency range ensure global compatibility. In addition to wireless and ultra-low power features, the STM32WL microcontroller also includes embedded security hardware features such as 128-bit/256-bit AES hardware encryption, PCROP read/write protection, and public key encryption using an elliptic curve encryption engine.

This chip has only been seen in a few trial boards in the ST community, with details not well known.4. Domestic ASR6505

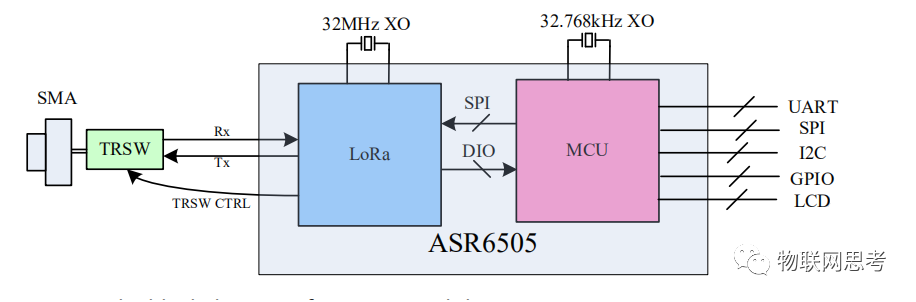

The ASR6505 is a chip developed by Shanghai Aojie Technology (ASR) based on the STM8L152 and SX1262 SIP package. It combines the RF characteristics of the SX1262 with the MCU characteristics of the STM8L. Compared to the above two development methods, the ASR6505 has advantages in cost and size. Additionally, the ASR6505 simplifies RF design and provides a rich set of peripheral interfaces (GPIO, ADC, I2C, SPI, UART, LCD, etc.) for secondary development. The official SDK is also provided.

From the above image, it is clear that the ASR6505 is a package of LoRa and MCU, where the SPI and DIO pins are already internally connected.

The subsequent development of end devices will also be based on this.

——————END——————

Recommended Reading

Architecture of LoRa IoT