Software-defined chips represent an emerging methodology in integrated circuit design. The goal is to achieve high performance, energy efficiency, flexibility, and security on a single chip, gaining a comprehensive advantage over traditional chip designs. Related research areas such as spatial computing architectures, dynamically reconfigurable structures, and high-level synthesis have been hot topics in the fields of computer architecture, solid-state circuits, and electronic design automation. The exploration of new reconfigurable programmable device technologies characterized by dynamic reconfiguration, coarse-grained computing, and software-defined hardware has already begun both domestically and internationally, becoming a strategic research direction fiercely contested by world powers.

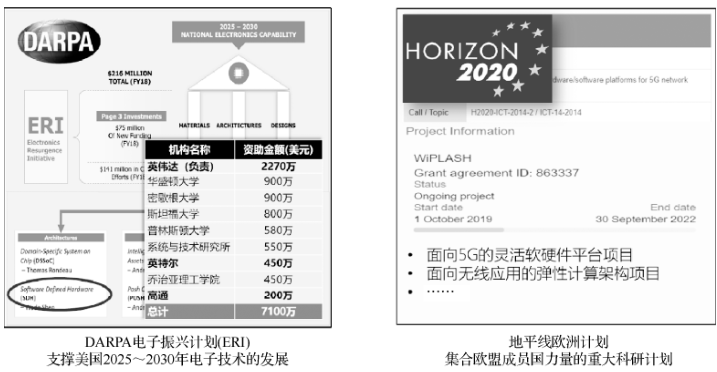

As shown in Figure 1, DARPA identified software-defined hardware technology as one of the supporting technologies for electronic technology development over the next decade in 2017. The aim is to establish “runtime reconfigurable hardware and software that achieves performance close to that of dedicated circuits without sacrificing the programmability of data-intensive algorithms.” Its features include: ① both software code and hardware structure can be dynamically optimized based on input data; ② hardware reuse is supported for new problems and algorithms. Therefore, DARPA believes that the key to implementing software-defined hardware is rapid hardware reconfiguration and dynamic compilation. According to DARPA’s project plan, the energy efficiency of software-defined hardware could exceed that of general-purpose processors by two orders of magnitude within the next five years, with reconfiguration speeds reaching 300 to 1000 ns. This project clearly outlines the research objectives for software-defined hardware, guiding the development direction in this field.

Figure 1: DARPA’s “Electronics Revitalization Program” and the EU’s “Horizon 2020” program

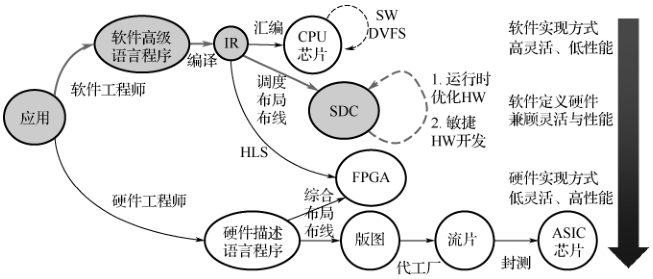

There is no essential difference between software-defined chips and software-defined hardware; however, as seen in Figure 2, agile development of chips is an additional feature of software-defined chips. Similarly, the EU’s “Horizon 2020” program has similar plans in the direction of software-defined hardware, but with a greater emphasis on specific applications such as communications.

Figure 2: Programming usage patterns of software-defined chips

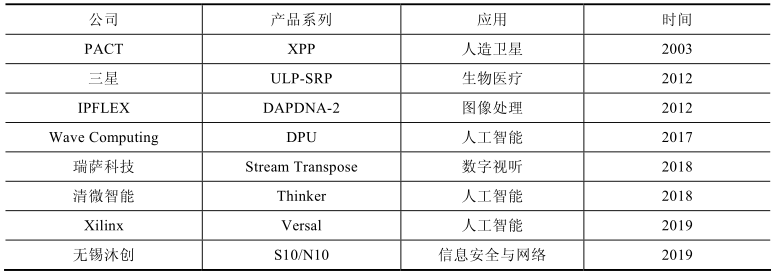

Research related to software-defined chips is even more abundant. Table 1 lists some representative products. The European Space Agency used PACT’s CGRA devices’ IP on Astrium’s satellite payload as early as around 2010. The dynamic reconfigurable structure ADRES proposed by IMEC in Europe around 2004 has been applied in Samsung’s biomedical and high-definition television products. Japan’s Renesas Technology has utilized its DRP structure proposed in 2004. With the addition of coarse-grained programmable computing arrays, Xilinx’s new product Versal represents the development of software-defined SoCs. In academia, research teams from Stanford University, UCLA, and MIT have also conducted long-term research in this direction, with results continuously published in top conferences in related fields.

Table 1: Industrialization status of research related to software-defined chips

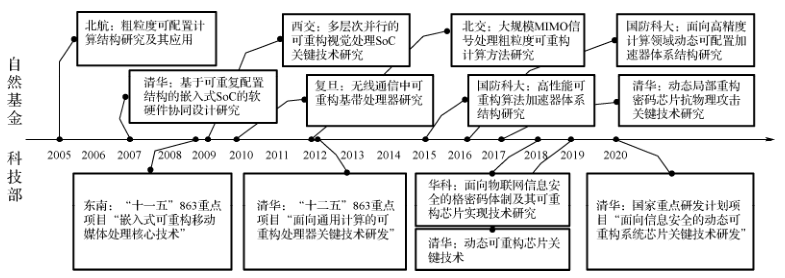

Research related to software-defined chips in China has been ongoing for nearly 20 years. Figure 3 summarizes the project support from various ministries and commissions in China. The National Natural Science Foundation of China launched the “Major Scientific Program for Basic Research on Semiconductor Integrated Chip Systems” in 2002, which laid the groundwork for the theoretical research of reconfigurable computing chips. In the past decade, the National Natural Science Foundation has supported topics related to reconfigurable computing almost every year. The Ministry of Science and Technology has supported the research and development of reconfigurable computing chip technology through the “11th Five-Year” 863 key project on “Embedded Reconfigurable Mobile Media Processing Core Technology” and the “12th Five-Year” 863 key project on “Key Technology Research and Development for Reconfigurable Processors for General Computing.” The industrialization of domestic research has been thriving in recent years, incubating startups based on reconfigurable computing technology such as Qingwei Intelligent and Wuxi Muchuang.

Figure 3: Support for research related to software-defined chips in China

The book “Software-Defined Chips” is divided into two volumes.

The first volume mainly introduces the evolution of the concept of software-defined chips from the development of integrated circuits and computing architectures, systematically analyzes the technical principles, characteristic analysis, and key issues of software-defined chips, and focuses on systematically introducing the hardware architecture design methods of software-defined chips from aspects such as architecture design primitives, hardware design space, and agile design methods. It also details the complete process from high-level languages to software-defined chip configuration information from the perspective of compilation systems.

ISBN 978-7-03-068779-1

Editor: Zhao Yanchun

The second volume analyzes the research focus of the programming model of software-defined chips by tracing the co-evolution of modern general-purpose processors and programming models. It introduces how to utilize the dynamic reconfigurable characteristics of software-defined chips to enhance the hardware security and reliability of chips, analyzes the challenges faced by software-defined chips, and looks forward to the development direction for achieving technological breakthroughs in the future, covering the latest research on software-defined chips in fields such as artificial intelligence, cryptographic computing, and 5G communications, as well as emerging application directions for the future.

ISBN 978-7-03-068780-7

Editor: Zhao Yanchun

(Edited by: Wang Fang)

Read Science Together!

Science Press | WeChat ID: sciencepress-cspm

Professional Quality Academic Value

Original Good Read Scientific Taste

Science Press Video AccountHardcore and Informative Audiovisual Science Disseminating science, we welcome you to light up ★ the star mark, like, and view ▼

Science Press Video AccountHardcore and Informative Audiovisual Science Disseminating science, we welcome you to light up ★ the star mark, like, and view ▼