Introduction

The ARM Cortex-M series cores are efficient, low-power processor architectures designed specifically for embedded systems and Internet of Things (IoT) devices. Their core functionalities cover real-time performance, low power consumption, high integration, and ease of use, making them widely applicable in fields such as smart homes, industrial control, and wearable devices.

Below is a comprehensive analysis of the Cortex-M cores:

1. Overview of Cortex-M Core Features

The Cortex-M series is optimized for different application scenarios, covering a wide range of needs from ultra-low power to high-performance AI edge computing:

-

Cortex-M0/M0+

- Positioning Entry-level, ultra-low power, low cost.

- Features Thumb-2 instruction set (16/32-bit mixed), 2-stage pipeline, supports hardware multiplication and interrupt controller (NVIC).

- Applicable Scenarios Simple control tasks (e.g., sensor nodes, appliance control).

Cortex-M3

- Positioning Balances performance and power consumption, enhances real-time capabilities.

- Features Supports nested vector interrupt controller (NVIC), memory protection unit (MPU), 3-stage pipeline, higher clock frequency.

- Applicable Scenarios Complex real-time control (e.g., motor control, industrial automation).

Cortex-M4

- Positioning Optimized for digital signal processing (DSP).

- Features Adds single-precision floating-point unit (FPU) and DSP instructions (e.g., SIMD) on top of M3.

- Applicable Scenarios Audio processing, sensor fusion, drone control.

Cortex-M7

- Positioning High-performance computing.

- Features Dual-issue 6-stage pipeline, supports TCM (Tightly Coupled Memory), clock frequency up to 400MHz+.

- Applicable Scenarios Graphics processing, high-speed communication (e.g., industrial gateways).

Cortex-M23/M33/M35P

- Positioning Security and IoT optimization.

- Features Supports TrustZone security extension (isolating secure and non-secure areas), enhanced MPU.

- Applicable Scenarios Payment terminals, smart locks, secure IoT devices.

Cortex-M55

- Positioning Entry-level AI/ML edge computing.

- Features Integrates Arm Helium technology (MVE v1, 64-bit SIMD extension), enhancing AI inference performance.

- Applicable Scenarios Voice recognition, simple image classification (e.g., smart speakers).

Cortex-M85

- Real-time video analysis (e.g., security cameras), multi-modal sensor fusion (industrial robots).

- Driver assistance systems (LiDAR point cloud processing, driver state monitoring).

- Based on Armv8.1-M architecture, supports Arm Helium technology (MVE v2), providing 128-bit SIMD vector operations, AI inference performance up to 4 times higher than M55.

- Integrates enhanced memory subsystem, supports higher bandwidth TCM and L1 cache, clock frequency up to 1GHz+.

- Security Upgrade TrustZone for Armv8-M + Physically Unclonable Function (PUF), supports AES-256/SHA-3 hardware encryption.

- Energy Efficiency Optimization Utilizes advanced processes (e.g., 5nm), dynamic voltage frequency scaling (DVFS).

- Positioning The pinnacle of AI edge computing performance, balancing high performance and real-time capabilities.

- Features

- Based on Armv8.1-M architecture, supports Arm Helium technology (MVE v2), providing 128-bit SIMD vector operations, AI inference performance up to 4 times higher than M55.

- Integrates enhanced memory subsystem, supports higher bandwidth TCM and L1 cache, clock frequency up to 1GHz+.

- Security Upgrade TrustZone for Armv8-M + Physically Unclonable Function (PUF), supports AES-256/SHA-3 hardware encryption.

- Energy Efficiency Optimization Utilizes advanced processes (e.g., 5nm), dynamic voltage frequency scaling (DVFS).

- Applicable Scenarios

- Real-time video analysis (e.g., security cameras), multi-modal sensor fusion (industrial robots).

- Driver assistance systems (LiDAR point cloud processing, driver state monitoring).

2. Core Functional Module Analysis

1. Core Architecture

- Thumb-2 Instruction Set compatible with 16/32-bit instructions, code density saves 30-40% compared to pure 32-bit instructions.

- Pipeline Design ranges from 2 stages in M0 to 6-stage dual-issue pipeline in M85, enhancing instruction parallelism.

- Low Power Modes

- Sleep Mode turns off CPU cores while keeping peripherals running (power consumption as low as μA).

- Stop Mode turns off the clock while retaining RAM data (quick wake-up).

- Standby Mode powers only the wake-up circuit (minimum power consumption, requires reset to wake).

2. Interrupt and Exception Handling

- NVIC (Nested Vector Interrupt Controller)

- Supports 1 to 240 interrupts, dynamic priority configuration, hardware auto-push/pop stack, interrupt latency as low as 12 cycles.

- SysTick Timer provides a precise time-slice scheduling basis for RTOS.

3. Memory and Protection

- Memory Protection Unit (MPU) (M3/M4/M7/M33/M85):

- Defines 8 to 16 memory region permissions (read/write/execute), preventing buffer overflow and other attacks.

- TCM (Tightly Coupled Memory) (M7/M55/M85):

- Zero-wait-cycle memory for storing critical code/data (e.g., real-time control loops or AI model weights).

4. DSP and Floating-Point Operations

- DSP Extended Instructions (M4/M7/M55/M85):

- M85’s Helium (MVE v2) completes 8 INT8 or 4 FP16 operations in one cycle, supporting frameworks like TensorFlow Lite Micro.

- FPU (Floating Point Unit)

- Single precision (M4/M33) or double precision (some M7/M85) floating-point operations, suitable for sensor data fusion.

5. Debugging and Tracing

- SWD/JTAG Interface supports online debugging and code flashing.

- CoreSight Technology (M7/M85):

- ETM/ITM real-time tracing of instruction execution (M7).

- SDC-600 (new in M85): high-speed tracing buffer (ETB), captures AI model execution paths.

6. Security Extensions

- TrustZone for Armv8-M (M23/M33/M85):

- Hardware isolation of secure and non-secure domains, protecting sensitive data such as keys and firmware.

- Physically Unclonable Function (PUF) (M85): generates a unique chip fingerprint to resist hardware cloning attacks.

3. Typical Application Scenarios

The ARM Cortex-M series CPU cores are widely used in embedded device products, with typical application scenarios/products including:

- IoT Devices Low-power sensor nodes (M0+/M23).

- Industrial Control Real-time motor control (M3/M4), predictive maintenance (M85).

- Consumer Electronics Smartwatches (M33), noise-canceling headphones (M55).

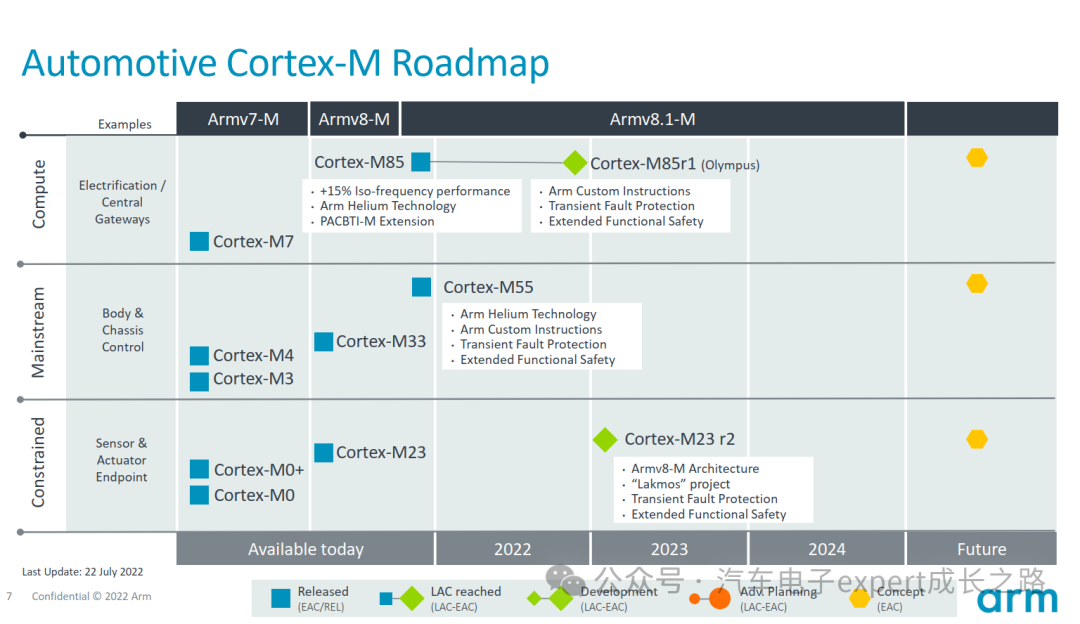

- Automotive Electronics Body control (M0+/M3/M4F/M33/M7), driver assistance (M85).

- AIoT Edge Computing Voice recognition (M55), real-time video analysis (M85).

- Security Devices Smart locks (M23), payment terminals (M33).

4. Development Toolchain

- IDE Keil MDK, IAR Embedded Workbench, VSCode + ARM GCC.

- AI Development TensorFlow Lite Micro, Arm ML Embedded Evaluation Kit (supports M55/M85).

- Debugging Tools J-Link, ULINK Pro, CoreSight Trace Analyzer (M85).

5. Conclusion and Future Trends

The Core Advantages of the Cortex-M Series:

- Comprehensive Coverage from 50MHz M0+ to 1GHz M85, meeting needs from simple control to complex AI edge computing.

- Energy Efficiency Ratio achieves TOPS/Watt level AI efficiency through advanced processes and instruction set optimizations (e.g., Helium).

- Hard Real-Time and Security μs-level interrupt response + TrustZone, suitable for high-reliability scenarios in industrial and automotive applications.

The Breakthrough Significance of Cortex-M85:

- Performance Innovation achieves 1TOPS computing power at the MCU level for the first time, supporting edge real-time video analysis and multi-modal AI.

- New Benchmark for Edge Intelligence drives the deployment of AI models in battery-operated devices (e.g., AR glasses, drones) through MVE v2 and 5nm technology.

Future Evolution Directions

- AI Native Architecture further expands SIMD bit width (e.g., 256 bits), supporting BF16/INT4 data types.

- Heterogeneous Computing collaborates with Cortex-A or NPU to build a layered edge computing platform.

- Full-Stack Security from hardware PUF to over-the-air (OTA) security updates, forming an end-to-end protection system.

Enwei Hu

April 18, 2025, in Chongqing