Introduction

I am very honored to participate in this development board review, thanks to Hangzhou Pingtouge Semiconductor Co., Ltd. and the Beagle community for their support. I received the world’s first high-performance TH1520 RISC-V SBC development board, BeagleV-Ahead. The BeagleV Ahead development board uses the Pingtouge’s TH1520 as the main control, making it an open-source RISC-V single-board computer (SBC) that is very suitable for RISC-V developers in the open-source community. The BeagleV Ahead inherits the unified design language of the Beagle development board and adopts the same dimensions as BeagleBone Black, with identical P8 and P9 expansion interfaces, thus supporting existing BeagleBone expansion boards. The BeagleV Ahead is equipped with a powerful quad-core RISC-V processor and rich configurations, yet offers an ultra-high cost-performance ratio, making it a value-for-money, portable RISC-V “pocket development board” suitable for anyone wishing to participate in RISC-V development, ready to use upon powering on.

Hardware Parameters

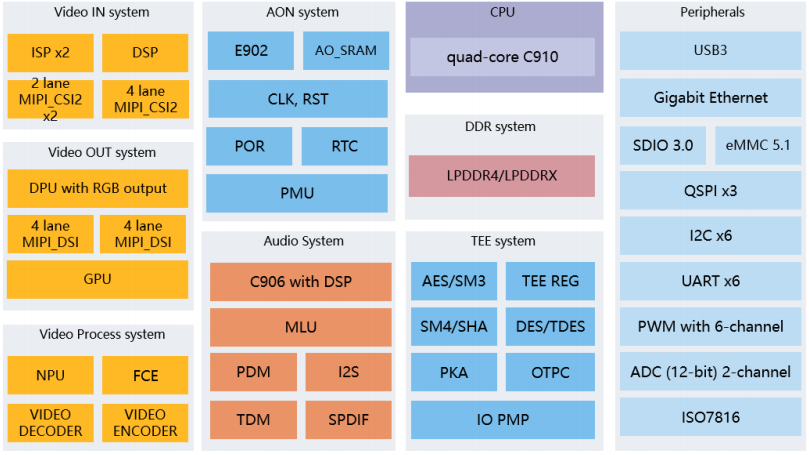

The main control chip is Pingtouge’s TH1520 SoC, which is a low-power, high-performance, and highly secure AI processor chip with multimodal perception and multimedia AP capabilities, suitable for AI edge computing applications such as video conference all-in-one machines, face recognition attendance control, and medical imaging. Based on a multi-core heterogeneous architecture, it integrates a quad-core C910 and a single-core C906 processor with a RISC-V instruction architecture and embeds multiple powerful hardware acceleration engines, featuring an NPU with 4TOPS@int8 AI computing power. It supports dual-channel external memory interfaces, LPDDR4/LPDDR4X, providing a maximum storage bandwidth of 34GB/s. It has a rich set of peripheral interfaces to meet different application scenarios.

-

In terms of video: supports H.265/H.264/VP9 standard video encoding, with a maximum resolution of 4K@40fps, supports H.265/H.264/VP9/AVS2 and other multi-format video decoding, with a maximum resolution of 4K@75fps, supports JPEG encoding and decoding, with a maximum resolution of 32Kx32K.

-

In terms of graphics processing: it has an embedded 3D GPU, fully compatible with OpenGL ES1.1/2.0/3.0/3.1, OpenCL 1.1/1.2/2.0, and Vulkan1.1/1.2, supports 2D acceleration engines, as well as general DSP accelerators.

TH1520 Main Chip Parameters

| Hardware | Description |

|---|---|

| CPU Processor | RISC-V 64GCV C910*4@2GHz supports little-endian mode with a 9~12 stage deep pipeline architecture, 3 issue and 8 execute superscalar architecture, fully transparent to software with in-order fetching, out-of-order issuing, out-of-order completion and in-order retirement two-level high buffer structure, Harvard structure with one-level high buffer and shared second-level high buffer supporting MESI consistency protocol, second-level cache supporting MOESI consistency protocol, each core supports 64KB I cache and 64KB D Cache, four cores share 1MB L2 Cache, supports private interrupt controller CLINT and public interrupt controller PLIC, two-level TLB memory management unit for virtual-physical address translation and memory management instructions, low-power access technology for high buffer prediction, low-power execution technology for short loop cache, supports segment load/store instructions, supports timer functions, supports TEE and REE, TEE/REE supports configurable core number at startup, supports custom and RISC-V compatible multi-core debugging framework, independent power domain, supports DVFS. |

| AI Computing Engine – NPU | Supports 4TOPS@INT8 general NNA computing power, main frequency 1GHz, supports TensorFlow, ONNX, Caffe, supports CNN, RNN, DNN, etc., supports convolution, activation, unit operations (addition, multiplication, max, min), pooling (min, max, average), normalization, deconvolution, lossless weight data compression, flexible bit depth support: flexible input/output and intermediate data bit depth, 4~16 bits bandwidth reduction. |

| AI Computing Engine – FCE | Supports dot product algorithm feature accelerator, supports multiple feature sizes from 128 to 256, stepping 32, supports signed and unsigned INT4/INT8 feature values, supports library comparison pause function, supports big-endian and little-endian mode conversion for library data, target vector and perturbation vector, supports basic database XOR perturbation preprocessing, million face database comparison in 50ms. |

| DSP | Supports two independent DSP cores, main frequency 1GHz, supports 256 8×8 MAC, supports 16 single-precision VFPU, supports image histogram statistics, 32KB instruction Cache, 2 128KB data RAM. |

| Video VI Interface | 1 path 4-lanes and 2 paths 2-lanes MIPI CSI-2 input, each lane supports 2.5Gbit/s, 2 paths 2-lanes MIPI CSI-2 can be stitched into 1 path 4-lanes MIPI CSI-2, 3 paths MIPI input can be mapped to 2 ISPs or DMA, supports RAW6, RAW7, RAW8, RAW10, RAW12 input formats, 4-lanes MIPI CSI supports maximum 13M sensor input, 2-lanes MIPI CSI supports maximum 5M sensor input, supports low-cost HDR algorithm processing for single exposure sensor. |

| Video VO Interface | 16-/24-bit RGB digital interface output, supports maximum 1080p@30fps, 2 paths 4-lanes MIPI DSI output, each lane supports 2.5Gbit/s, HDMI interface* supports HDMI 2.0, backward compatible with HDMI 1.4* supports maximum 1080p@120fps, 4Kx2K@60fps* input reference clock 13.5MHz to 600MHz* maximum total bandwidth 18Gbps* supports 8-channel audio output* supports CEC (Consumer Electronics Control)* supports HPD (Hot Plug Detection)* supports HDCP 1.4. |

| Image Signal Processor | Supports two independent ISP processing, supports RAW 8~16 bit input, supports IR 10 bit/YUV420 8 bit/RGB888 output, supports RGB Bayer/RGB IR pattern 4×4 input processing, supports maximum 13M pixel input (12M pixel processing), supports LSC and DPC, supports 3A (AE, AWB, AF) algorithms, supports 2D/3D image denoising and image sharpening, supports color enhancement, highlight suppression, backlight compensation, gamma correction, etc., supports anti-flicker, supports fisheye correction, supports HDR and WDR. |

| Video Decoder | Supports H.264 BP/MP/HP@level 5.1 decoding, maximum 4K resolution, supports H.265/HEVC Main Profile@level 5.1 decoding, maximum 4K resolution, supports VP9 Profile-2 decoding, maximum 4K resolution, supports AVS2.0 decoding, maximum 4K resolution, supports VP6/7/8/AVS/AVS+/VC1/MPEG4 decoding, maximum 1920×1080 resolution, decoding performance maximum 4K@75fps, supports multiple encoding and multiple decoding, and supports simultaneous encoding and decoding JPEG encoding and decoding. |

| Video Encoder | Supports H.264 BP/MP/[email protected] encoding, maximum 4K resolution, supports H.265/HEVC Main Profile encoding, maximum 4K resolution, only supports I frames and P frames, does not support B frame encoding performance maximum 4K@40fps, supports multiple encoding and multiple decoding, and supports simultaneous encoding and decoding JPEG encoding and decoding. |

| 2D Graphics Accelerator | 2D operations multi-source blending supports YUV format rectangular operations/clear/block transfer: 4 pixel/cycle. |

| Image Processing Unit | Supports APIs Vulkan 1.1/1.2, OpenCL 1.1/1.2/2.0, OpenGL ES 3.0/3.1/3.2 based on fragment 3D graphics rendering, supports multiple fragments processing simultaneously, programmable high-quality anti-aliasing support, advanced DMA operations reduce main CPU load, compressed texture encoding, lossless data compression firmware execution dedicated processor. |

| Display Processing Unit | Supports dual video display, one connected to HDMI interface, resolution 4K@30fps, one connected to MIPI DSI interface, resolution 1080p@60fps, two displays support a total of 6 overlay layers, the number of layers can be flexibly configured, supports rotation and scaling video timing generation filtering and scaling vertical and horizontal scaling programmable filtering hardware cursor. |

| Audio Interface | Supports 1 8-channel I2S external CODEC audio input, up to 384kbps, supports 3 2-channel I2S/PCM external CODEC or Bluetooth voice, supports low-power VAD, supports 8-channel PDM data interfacing with external DMIC, supports 8-channel TDM/PCM input, supports 2 SPDIF-IN/OUT, supports sample rates of 32/44.1/48/88.2/96/192kHz. |

| Audio Processor | C906 single-core processor* main frequency 500~800MHz* RV64IMA[FD]C[V] instruction architecture* 5-stage single-issue in-order execution pipeline* one-level Harvard structure instruction and data cache, size 32KB, cache behavior 64B* Sv39 memory management unit, achieving virtual-physical address translation and memory management* supports AXI4.0 128-bit Master interface* supports in-core interrupts CLINT and interrupt controller PLIC* configurable floating-point unit and vector unit* SIMD128 processing unit. |

| Security Engine | TEE+REE two-layer security architecture supports AES/DES/3DES/SM4 encryption and decryption algorithms, maximum speed 200MB/s, supports HASH/SM3, maximum speed 200MB/s, supports RSA/SM2 hardware random number generator. |

| Hardware-based isolation mechanism supports secure boot, built-in sensor provides physical protection for secure circuits. | |

| Storage Interface | On-chip memory: BootROM: 128KB, shared SRAM: 1.5MB, off-chip storage:* supports 32/64 bit LPDDR4/LPDDR4X, maximum speed 4266Mbps* SPI NOR/NAND Flash interface* eMMC5.1 interface, maximum speed supports HS400* SD 3.0 interface. |

| Peripheral Interface | GMAC* supports 2 paths of Gigabit Ethernet* supports 10/100/1000Mbps data transfer rate RGMII interface, USB supports one USB 3.0 DRD, can work as host or device, compatible with USB 2.0, UART supports 8 UART* 1 path with flow control UART, maximum speed 4Mbps* 3 paths support infrared UART, I2C, ISO7816, GPIO, SAR-ADC, PWM, PVT Sensor, EFUSE. |

Initial Experience

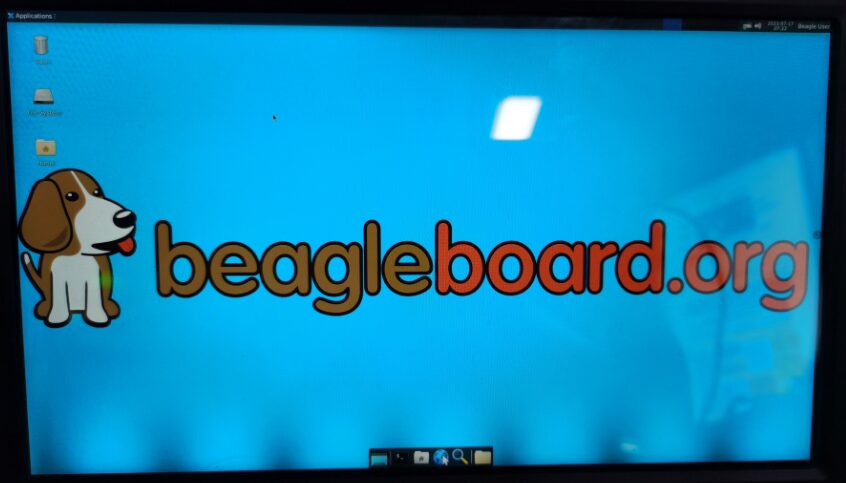

Screen Display Effect:

The board has a MicroHDMI interface, which can connect to an HDMI screen via “MicroHDMI” to HDMI. The BeagleV-Ahead has strong image performance and can support output of 4K/60Fps images, compatible with 4K/60FPS display devices.

The HDMI screen display effect is as follows:

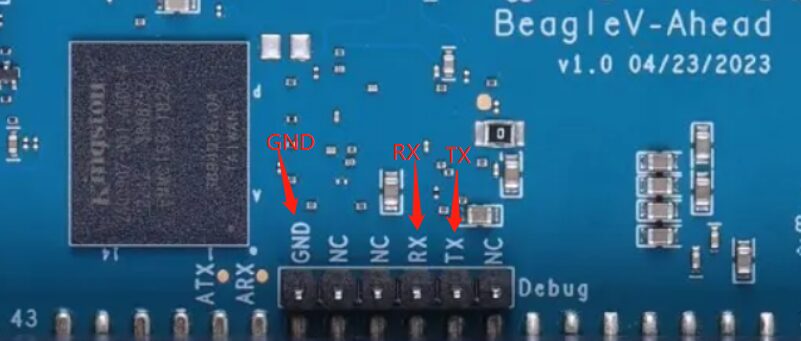

Serial Debugging:

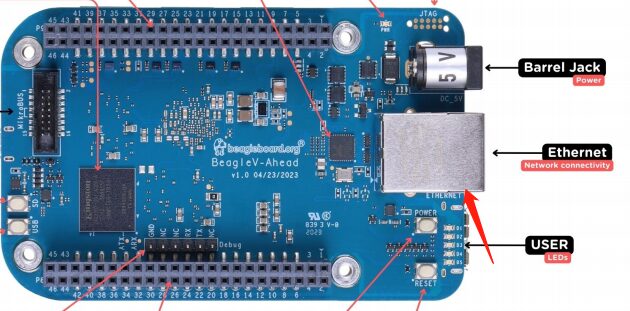

The BeagleV-Ahead exposes the UART interface to a 2.54mm pin header. By connecting a USB to TTL serial module, the board can be operated via command line. It is located on the side of the P8 female header and is a 6-pin header; we only need to use 2.54 Dupont wires to connect the RX, TX, and GND pins to use the serial port.

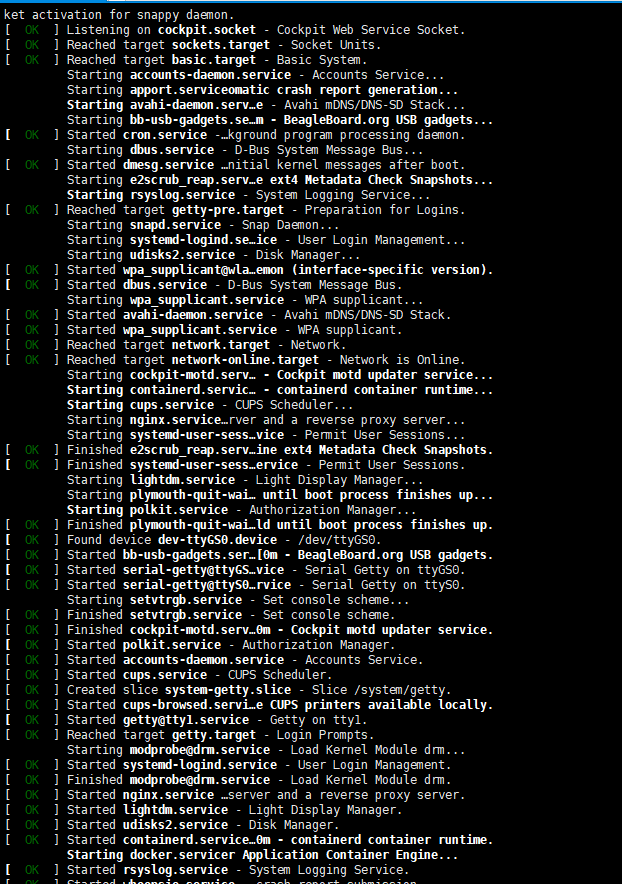

Boot startup log:

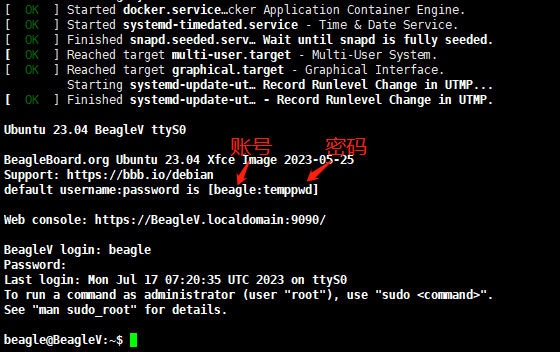

Serial terminal login:

Network Cable Testing:

The BeagleV-Ahead not only provides wireless networking capabilities but also offers an RJ45 wired network interface for faster and more stable network requirements. The front of the BeagleV-Ahead features an RTL8211F RGMII Gigabit Ethernet PHY chip.

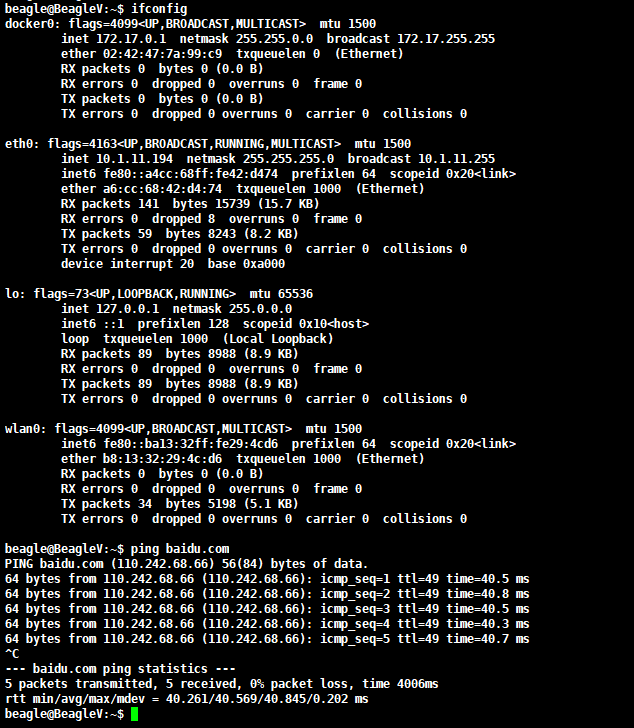

Network testing:

Conclusion

-

The BeagleV-Ahead feels very compact, a pocket-sized board. -

The TH1520 provides a rich set of interfaces; the BeagleV-Ahead basically exposes all interfaces. -

There are also a few downsides to the board: 1) The USB interface is uncommon; if you need to connect a mouse, etc., you need to purchase a micro-B to USB-A adapter. 2) The current firmware has some display lag, possibly due to the GPU not being fully compatible.