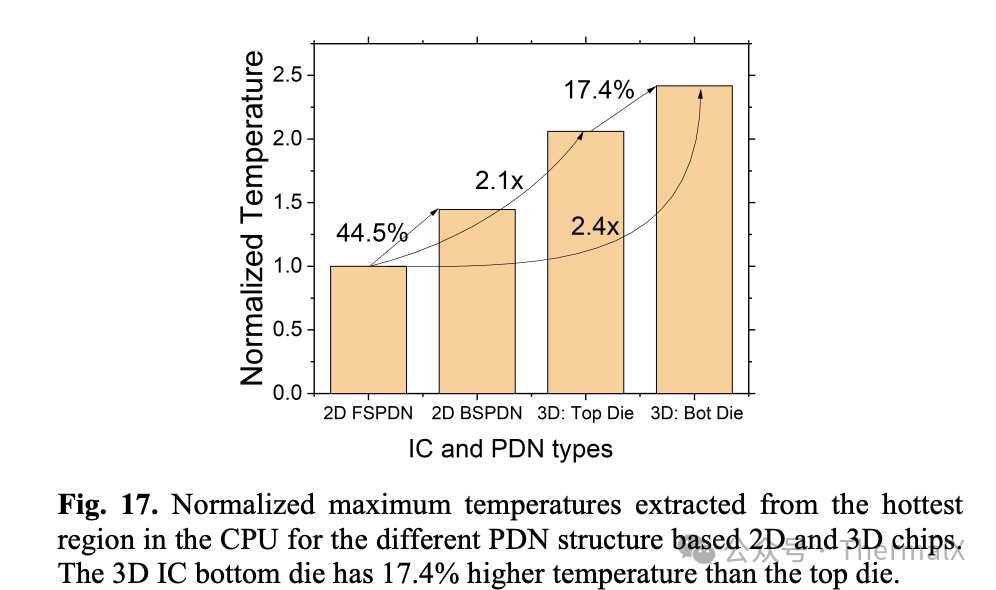

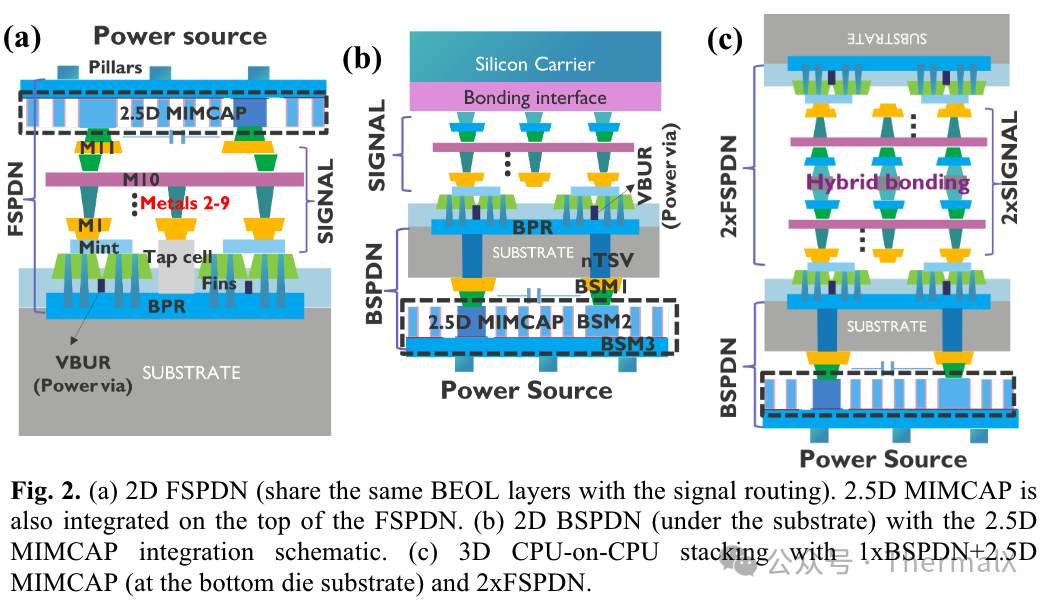

This literature is from IMEC, published in 2022, focusing on the impact of BSPDN on the study of PPAT.The front end (FEOL) is an active driver of chip power/performance/area (PPA). As scaling approaches the physical limits of semiconductor devices, the back end (BEOL)/middle end (MEOL)/packaging becomes increasingly important for PPA improvements in chips/systems. At 2nm and below, BSPDN back interconnects (beneath the chip/substrate) have also been proposed to complement traditional back-end processes (BEOL).Two nTSV-BPR connection processes after silicon thinning in BSPDN:

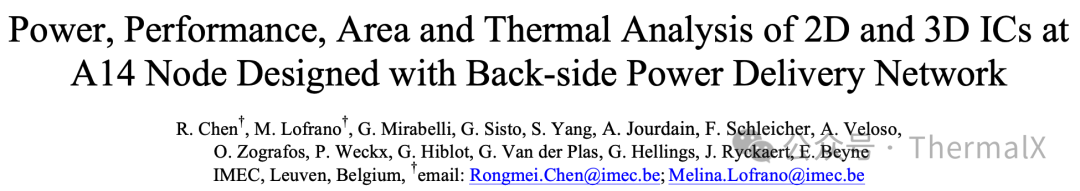

This literature is from IMEC, published in 2022, focusing on the impact of BSPDN on the study of PPAT.The front end (FEOL) is an active driver of chip power/performance/area (PPA). As scaling approaches the physical limits of semiconductor devices, the back end (BEOL)/middle end (MEOL)/packaging becomes increasingly important for PPA improvements in chips/systems. At 2nm and below, BSPDN back interconnects (beneath the chip/substrate) have also been proposed to complement traditional back-end processes (BEOL).Two nTSV-BPR connection processes after silicon thinning in BSPDN: Schematic diagrams of FSPDN and BSPDN:

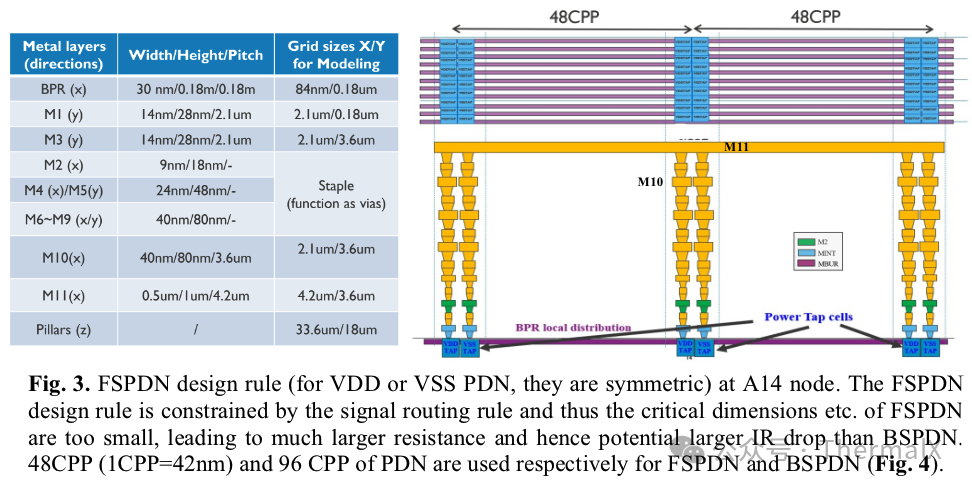

Schematic diagrams of FSPDN and BSPDN: The design rule of FSPDN at the A14 node. FSPDN may lead to a potentially large IR drop compared to BSPDN.

The design rule of FSPDN at the A14 node. FSPDN may lead to a potentially large IR drop compared to BSPDN. Design rule of BSPDN:

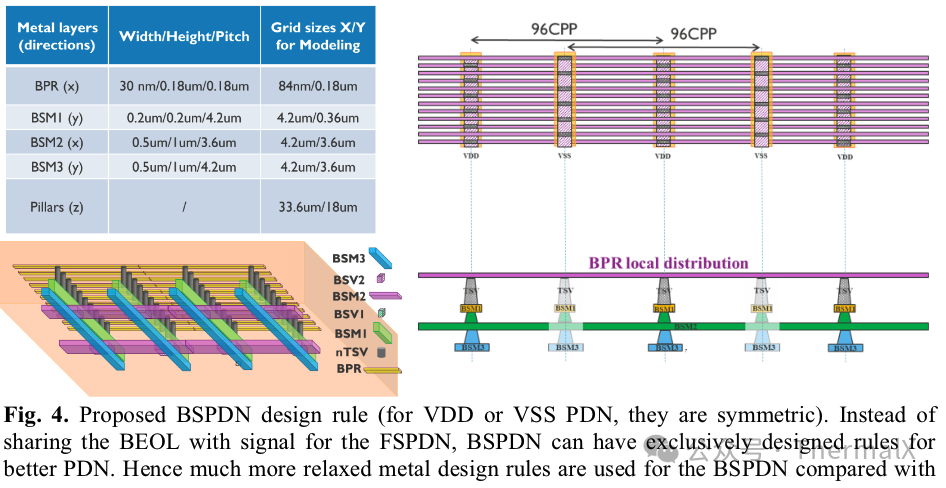

Design rule of BSPDN: The author uses RO simulation to model the IR drop of the CPU.Voltage transient performance of BSPDN and FSPDN and the impact of 2.5D MIMCAP:

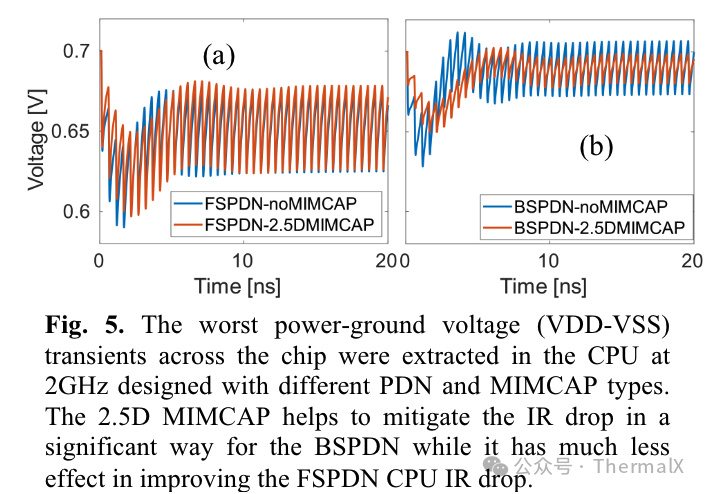

The author uses RO simulation to model the IR drop of the CPU.Voltage transient performance of BSPDN and FSPDN and the impact of 2.5D MIMCAP: IR drop cloud map of FSPDN:

IR drop cloud map of FSPDN: IR drop cloud map of BSPDN:

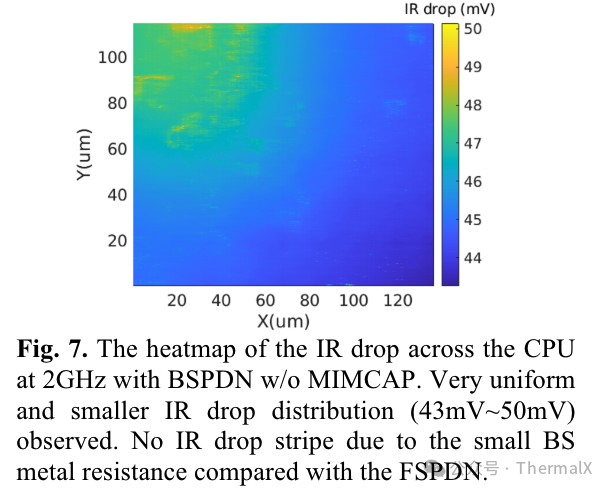

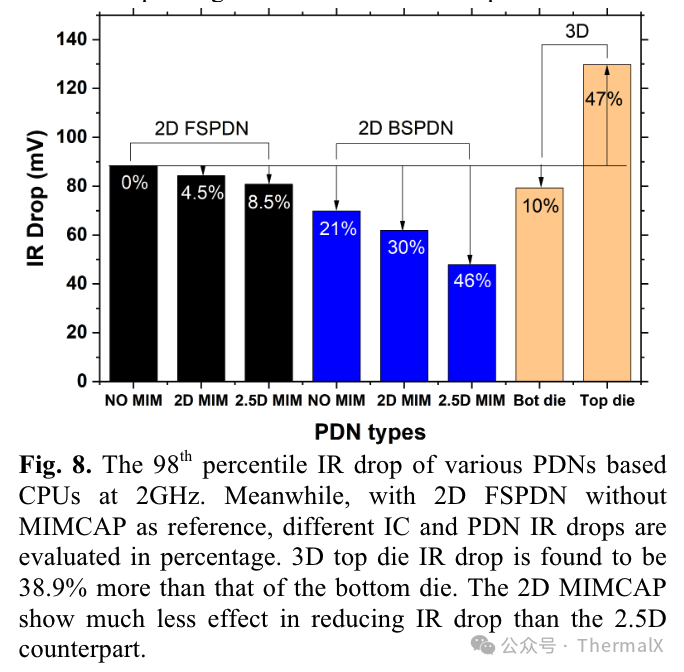

IR drop cloud map of BSPDN: Summary of IR drop under different designs: (The IR drop of the 3D Die in the figure seems inconsistent with the description in the text)

Summary of IR drop under different designs: (The IR drop of the 3D Die in the figure seems inconsistent with the description in the text) Analysis of the impact of IR drop on CPU timing based on RO simulation:

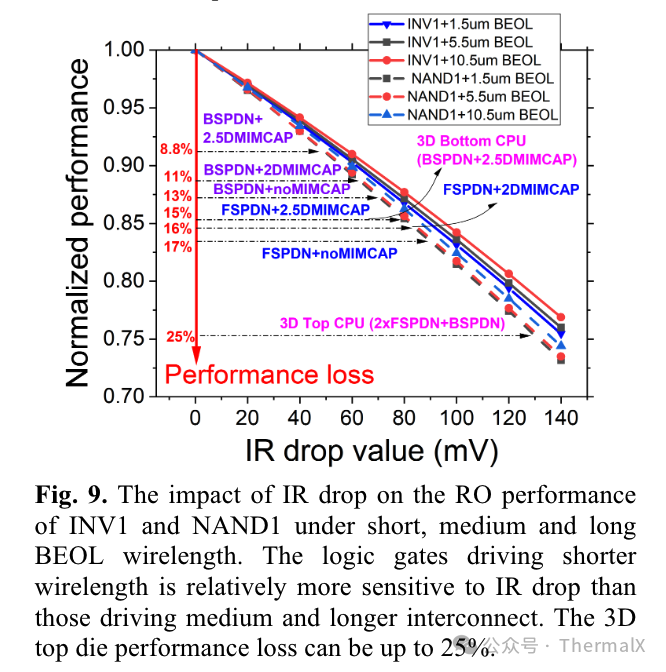

Analysis of the impact of IR drop on CPU timing based on RO simulation: Power consumption of PDN under different PDN designs:

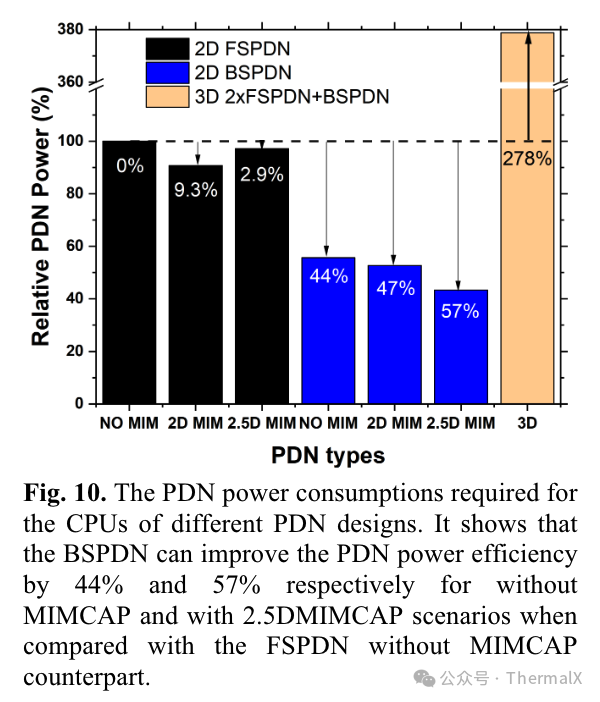

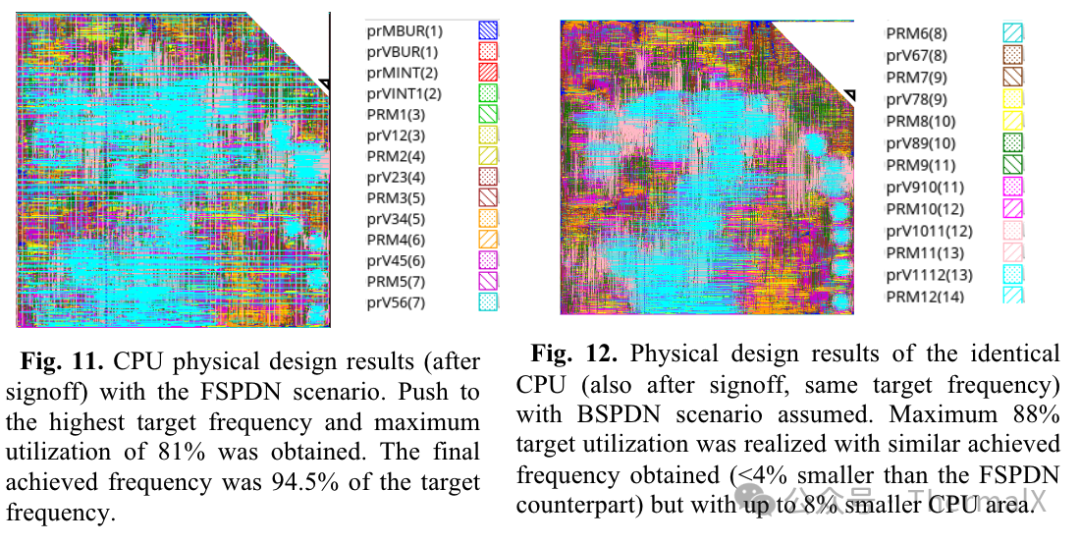

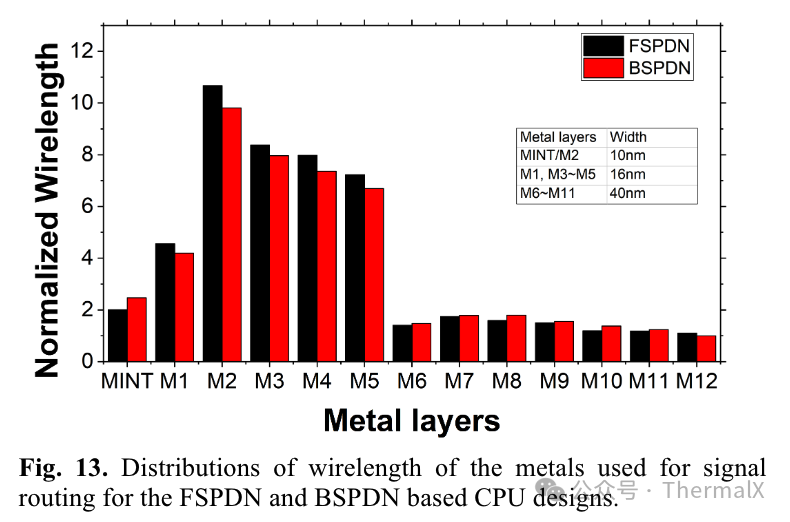

Power consumption of PDN under different PDN designs: Physical design results under different PDN designs: BSPDN can save 8% area.

Physical design results under different PDN designs: BSPDN can save 8% area.

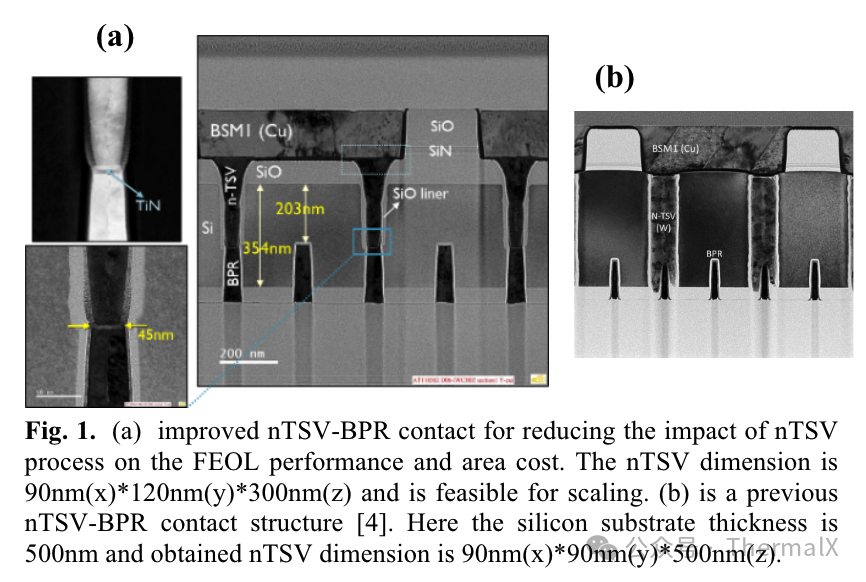

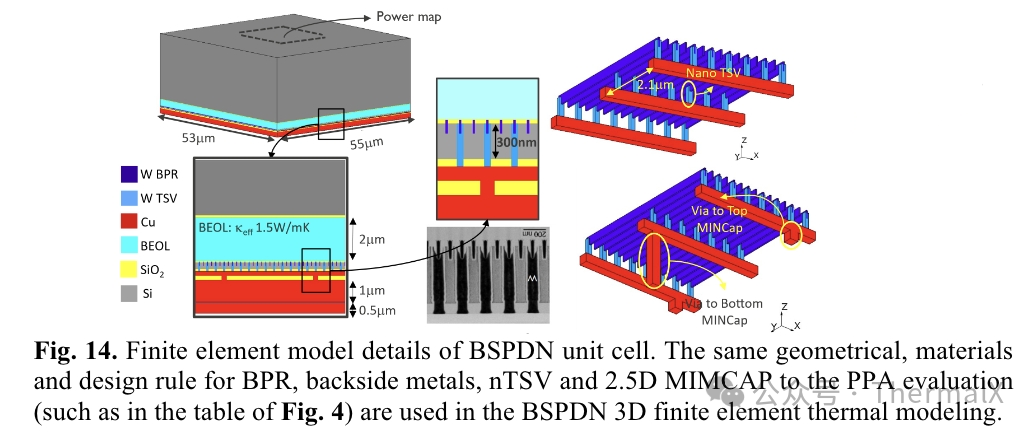

The author conducts thermal simulation evaluation based on the FEM method.Thermal simulation model of BSPDN:

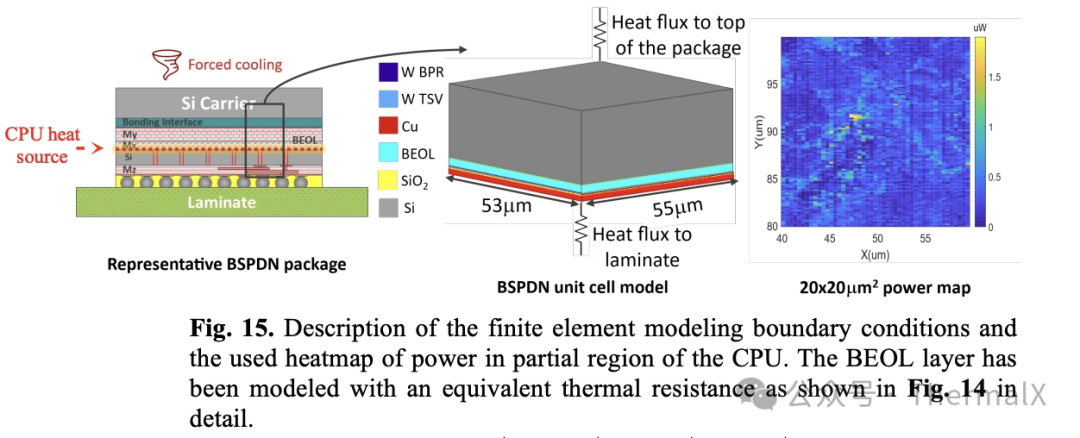

The author conducts thermal simulation evaluation based on the FEM method.Thermal simulation model of BSPDN: Package-level thermal model/boundary conditions/power map:

Package-level thermal model/boundary conditions/power map: Due to the increase in vertical thermal resistance caused by BSPDN BEOL/Bonding, and the increase in diffusion thermal resistance due to silicon thinning, thermal performance is worse than FSPDN.

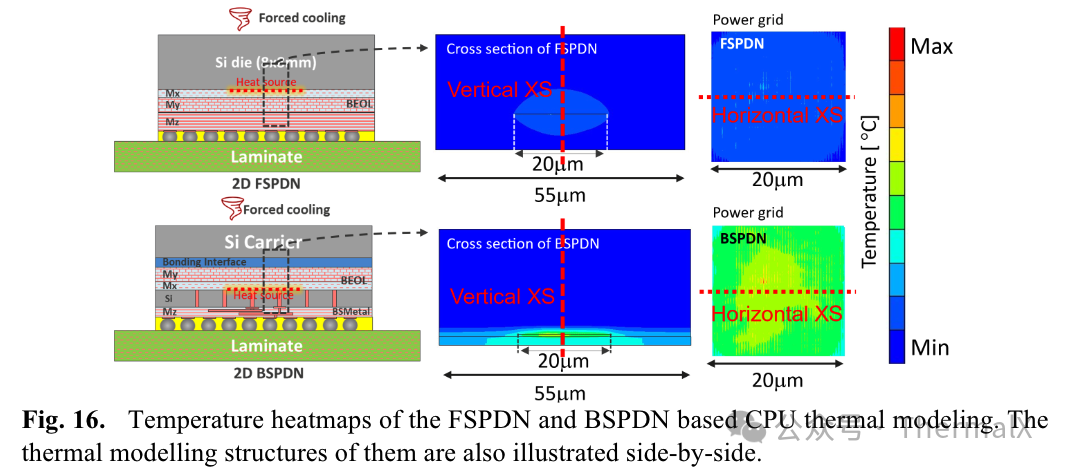

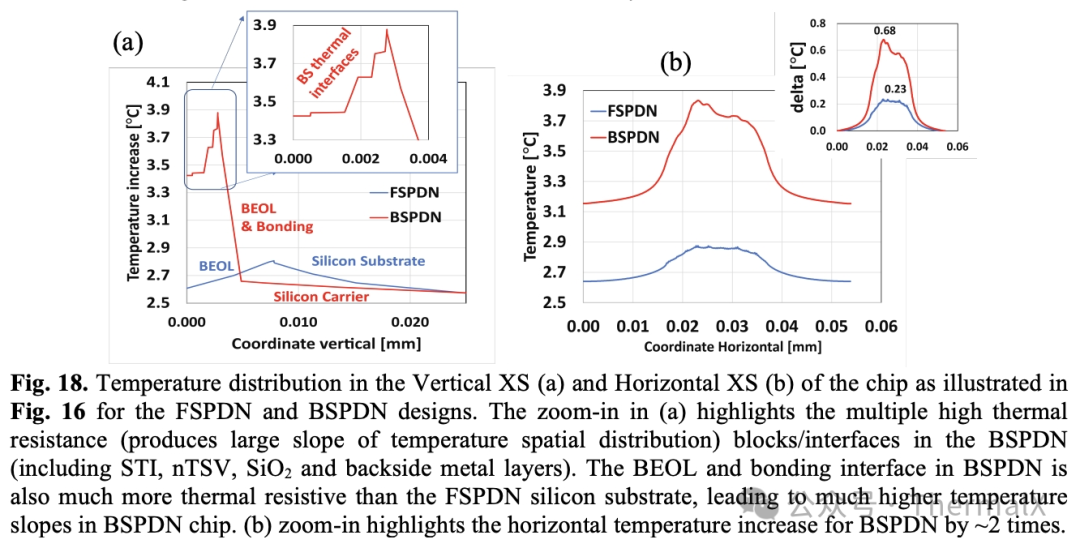

Due to the increase in vertical thermal resistance caused by BSPDN BEOL/Bonding, and the increase in diffusion thermal resistance due to silicon thinning, thermal performance is worse than FSPDN. Cross-sectional temperature distribution:

Cross-sectional temperature distribution: Thermal model of 3DIC:

Thermal model of 3DIC: Temperature distribution of 3DIC:

Temperature distribution of 3DIC:

Temperature under different structures: 3D>2D BSPDN>2D FSPDN