Fundamentals of Low-Power Design: A Comprehensive Analysis of Multi-Bit Cells

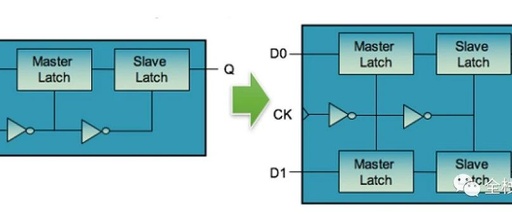

This article was originally published in the Zhihu column [The Path of Digital IC Backend Engineers]. Multi-bit cells have been widely used in numerous chip designs as a means to control power consumption, and various EDA tools provide extensive and comprehensive support for them. Today, we will start with the basic structure and principles of … Read more