Phase One

1

Sand

Silicon is the second most abundant element in the Earth’s crust, and deoxygenated sand (especially quartz) contains up to 25% silicon as silicon dioxide (SiO2), which is the foundation of the semiconductor manufacturing industry.

2

Silicon Smelting

12-inch/300mm wafer level. Silicon is purified through multiple steps to achieve semiconductor-grade quality, known as electronic-grade silicon (EGS), with an average of no more than one impurity atom in every million silicon atoms.

Phase Two

1

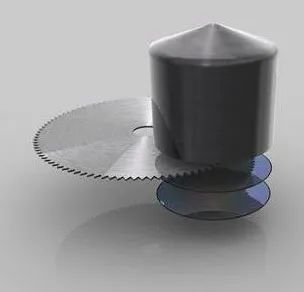

Silicon Ingot Cutting

Cut horizontally into round individual silicon wafers, which we commonly refer to as wafers.

2

Wafer

The cut wafers are polished to become nearly flawless, with surfaces that can even be used as mirrors.

Phase Three

1

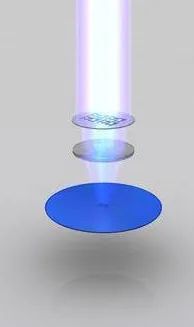

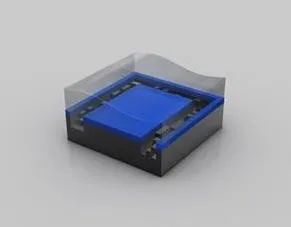

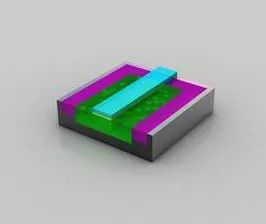

Photo Resist

The blue part in the image is the photo resist liquid that is poured onto the wafer during rotation, similar to making traditional film. The rotation allows the photo resist to spread very thin and very evenly.

2

Photolithography

The photo resist layer is subsequently exposed to ultraviolet (UV) light through a mask, becoming soluble. The chemical reaction that occurs is similar to the change of film at the moment the shutter of a mechanical camera is pressed. The mask prints the pre-designed circuit pattern, and the UV light shining through it onto the photo resist layer forms each layer of the microprocessor’s circuit pattern. Generally, the circuit pattern obtained on the wafer is one-fourth of the pattern on the mask.

This leads to transistor sizes in the range of 50-200 nanometers. A single wafer can yield hundreds of processors, but from here we will narrow our focus to one of them, demonstrating how to make transistors and other components. Transistors act as switches, controlling the direction of current.

Today’s transistors are so small that approximately 30 million can fit on the head of a pin.

Phase Four

1

Dissolving Photo Resist

The photo resist exposed to ultraviolet light during the lithography process is dissolved away, leaving behind a pattern consistent with the mask.

2

Etching

Chemicals are used to dissolve the exposed parts of the wafer, while the remaining photo resist protects the areas that should not be etched.

3

Removing Photo Resist

After etching is complete, the photo resist has fulfilled its purpose and is removed, revealing the designed circuit pattern.

Phase Five

1

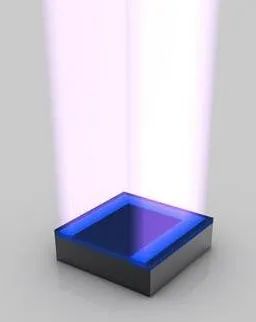

Photo Resist

Another layer of photo resist (blue part) is poured on, followed by photolithography, and the exposed parts are washed away, leaving the remaining photo resist to protect the areas that will not undergo ion implantation.

2

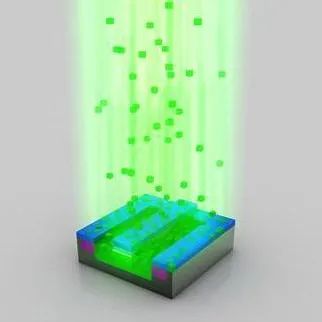

Ion Implantation

In a vacuum system, ions of doped atoms are accelerated and injected into solid materials, forming special implanted layers in the injected areas, altering the conductivity of those regions of silicon. The speed of the injected ion beam can exceed 300,000 kilometers per hour after being accelerated by an electric field.

3

Removing Photo Resist

After ion implantation is complete, the photo resist is also removed, and the implanted area (green part) has been doped with different atoms. Note that the green color at this point differs from before.

Phase Six

1

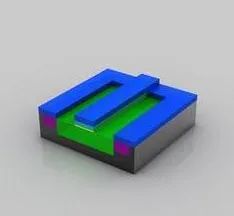

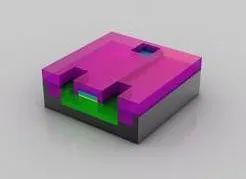

Transistor Ready

At this point, the transistor is essentially complete. Three holes are etched into the insulating material (magenta) and filled with copper to interconnect with other transistors.

2

Electroplating

A layer of copper sulfate is electroplated onto the wafer, depositing copper ions onto the transistor. Copper ions will move from the positive electrode (anode) to the negative electrode (cathode).

3

Removing Photo Resist

After electroplating is complete, copper ions deposit on the surface of the wafer, forming a thin layer of copper.

Phase Seven

1

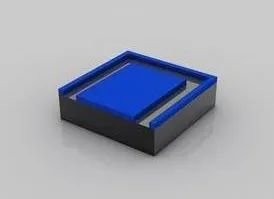

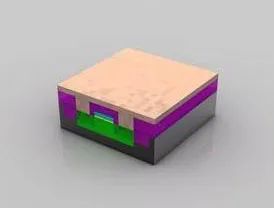

Polishing

Excess copper is polished away, essentially smoothing the surface of the wafer.

2

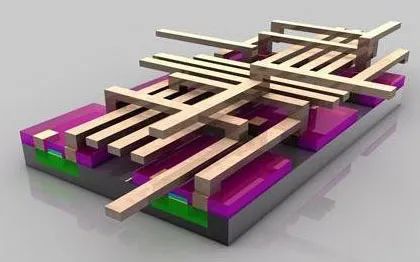

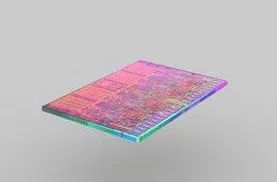

Metal Layer

At the transistor level, a combination of six transistors, approximately 500 nanometers. A composite interconnect metal layer is formed between different transistors, with specific layouts depending on the different functionalities required by the corresponding processor.

The surface of the chip appears exceptionally smooth, but it can actually contain more than twenty layers of complex circuits, which, when magnified, reveal an extremely intricate circuit network resembling a futuristic multi-layer highway system.

3

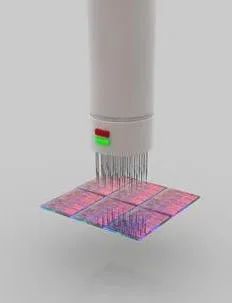

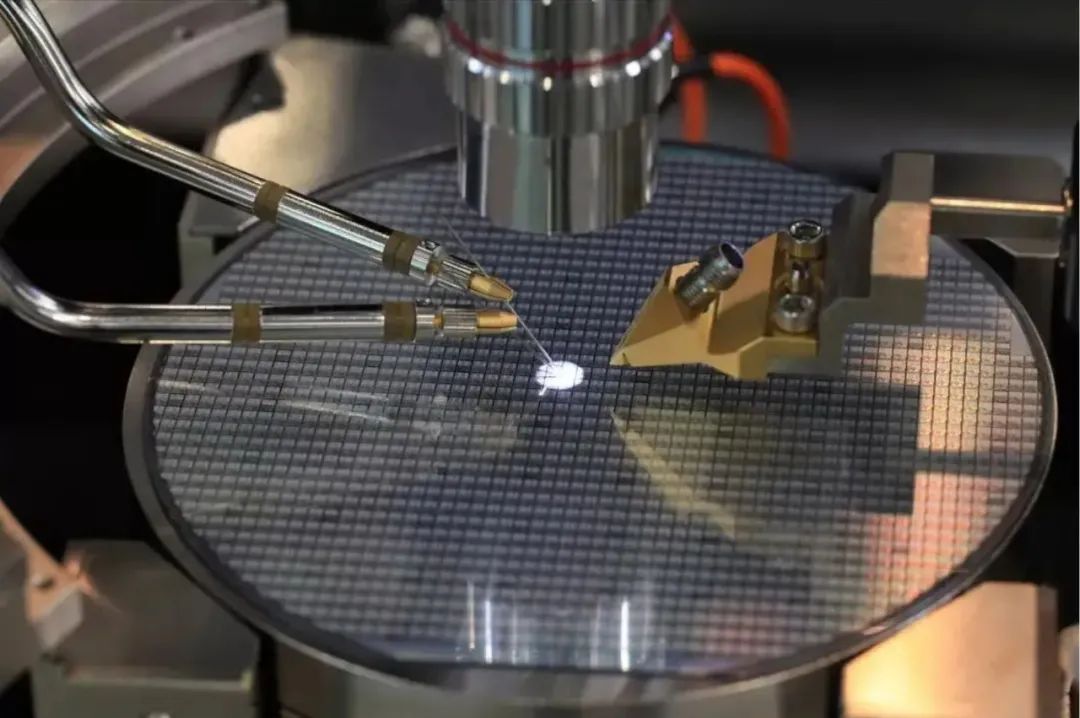

Wafer Testing

At the core level, approximately 10mm/0.5 inches. The image shows a portion of the wafer undergoing its first functional test, using a reference circuit pattern for comparison with each chip.

4

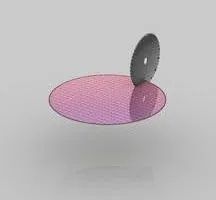

Wafer Slicing

At the wafer level, 300mm/12 inches. The wafer is sliced into pieces, each piece being the core (die) of a processor.

Phase Eight

1

Single Core

At the core level. A single core cut from the wafer, here showcasing the Core i7 core.

2

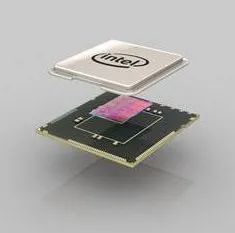

Packaging

At the packaging level, 20mm/1 inch. The substrate (base), core, and heat sink are stacked together to form the appearance of the processor we see. The substrate (green) serves as a base and provides electrical and mechanical interfaces for the processor core to interact with other parts of the PC system. The heat sink (silver) is responsible for dissipating heat from the core.

3

Removing Photo Resist

At this point, a complete processor is obtained (here is a Core i7).

Phase Nine

1

Grade Testing

The final test can identify the key characteristics of each processor, such as maximum frequency, power consumption, and heat generation, determining the processor’s grade, whether it is suitable for making the high-end Core i7-975 Extreme or the low-end Core i7-920.

The above content describes the manufacturing process of chips. We have now entered the technological era, heavily reliant on computer science and technology, with CPUs being essential components of various computers. Without even discussing the architectural design, the production of CPUs embodies the wisdom of humanity, incorporating the most advanced processes, production technologies, and cutting-edge machinery available in the world today.

Material provided by: Xu Yiwen

Editor: Lan Wenping

Review: News Publicity Center

Source: Qingdao Sixty-Seven Middle School , Reprinted from: Global Physics 2022-10-16