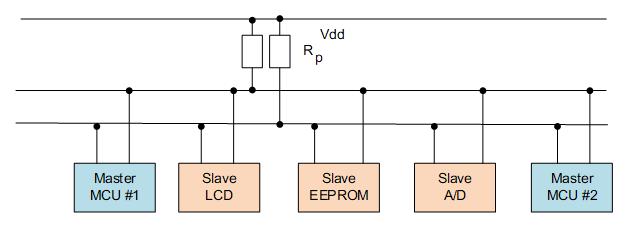

I2C Bus

<span> synchronous, bidirectional, half-duplex two-wire serial interface bus</span>. Here, half-duplex means that at any given time, communication can only occur in one direction.

-

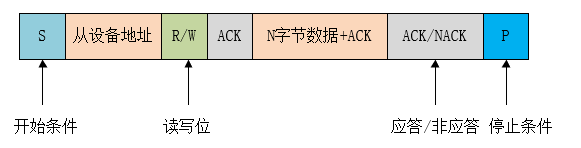

Start Condition: When SCL is high, the master pulls SDA low, indicating that data transmission is about to begin. -

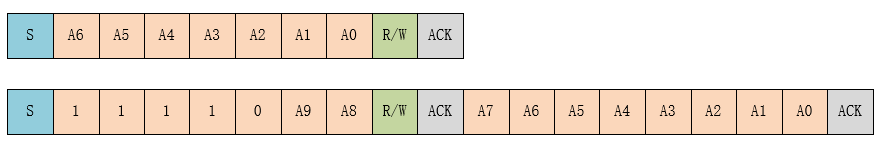

Slave Address: The first byte sent by the master is the slave address, with the highest 7 bits being the address and the lowest bit being the R/W read-write control bit, where 1 indicates a read operation and 0 indicates a write operation.

-

Acknowledge Signal: After transmitting one byte of data, the receiver needs to reply with an ACK (acknowledge). When writing data, the slave sends ACK; when reading data, the master sends ACK. When the master reads the last byte of data, it can send NACK (Not acknowledge) followed by a stop condition. -

Data: After sending the slave address, commands may be sent based on the slave, followed by data transmission, which can be sent by either the master or the slave, with each data byte being 8 bits, and there is no limit to the number of data bytes. -

Repeated Start Condition: During a communication session, if the master needs to transmit data to different slaves or switch read/write operations, it can send another start condition. -

Stop Condition: When SDA is low, the master pulls SCL high and keeps it high, then pulls SDA high, indicating that the transmission is over.

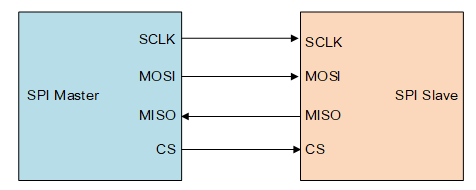

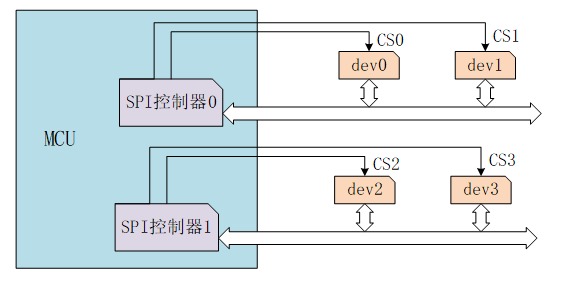

SPI Bus

<span> synchronous, bidirectional, full-duplex four-wire serial interface bus</span>, originally proposed by Motorola. SPI consists of a system of “one master device + multiple slave devices.” It should be noted that as long as only one master device is activated at any time, multiple SPI master devices can exist in the system. It is commonly used for communication between EEPROM, FLASH, real-time clocks, AD converters, digital signal processors, and digital signal decoders.

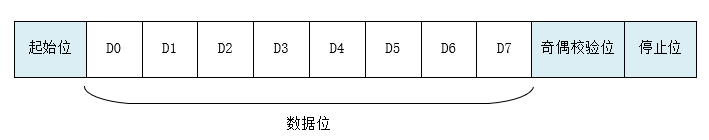

UART

<span> Universal Asynchronous Receiver-Transmitter</span>, is an asynchronous serial communication protocol that transmits each character of data one bit at a time. It is a frequently used data bus in application development.

-

Start Bit: Indicates the beginning of data transmission, with a logic level of “0”.

-

Data Bits: Possible values are 5, 6, 7, 8, or 9, indicating the number of bits of data being transmitted. The typical value is 8, as one ASCII character is 8 bits.

-

Parity Bit: Used by the receiver to check the received data, ensuring the number of “1” bits is even (even parity) or odd (odd parity), thus verifying the correctness of data transmission. This bit is optional.

-

Stop Bit: Indicates the end of a data frame, with a logic level of “1”.

-

Baud Rate: The rate of serial communication, represented by the number of valid bits transmitted per unit time, measured in bits per second (bps). Common baud rate values include 4800, 9600, 14400, 38400, and 115200, with higher values indicating faster data transmission. A baud rate of 115200 means 115200 bits of data are transmitted per second.

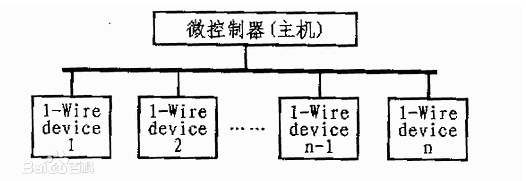

1-Wire Interface

<span> asynchronous half-duplex communication protocol</span> developed by Maxim Dallas Semiconductor, also known as the Dallas 1-Wire® protocol. It utilizes a single signal line DQ for communication according to the master-slave communication model.

Parallel Interface

1

《1700字干货 | 嵌入式系统编程软件架构该注意哪些方面?》

2

《1700字干货 | 嵌入式工程师不能不知道的3种常见嵌入式设备通信协议……》

3

《“2020年嵌入式软件秋招经验和对嵌入式软件未来的一点思考”》