Click the aboveblue text to follow us

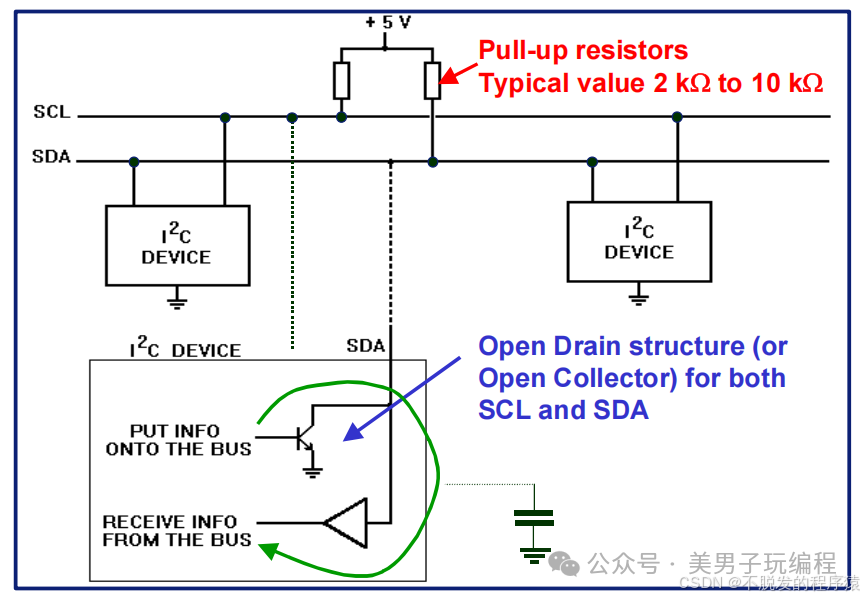

The I2C bus, as a widely used communication protocol in embedded systems, has its stability and reliability directly affecting the overall performance of the system.

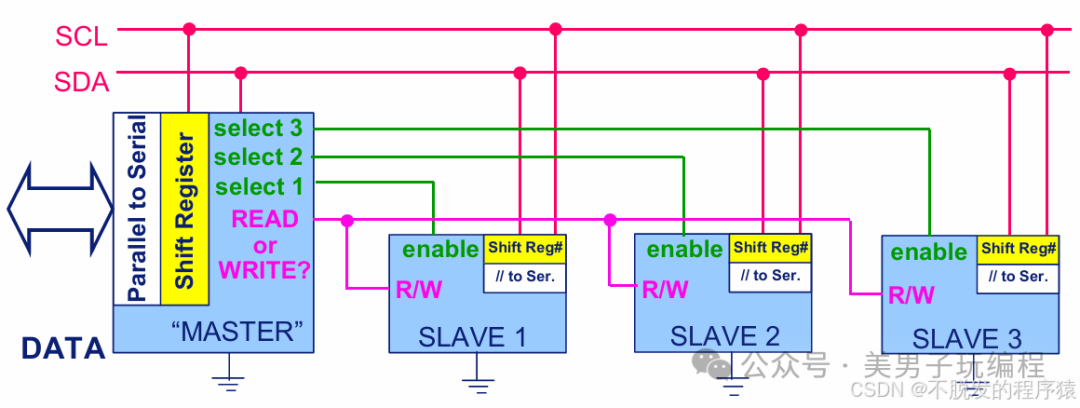

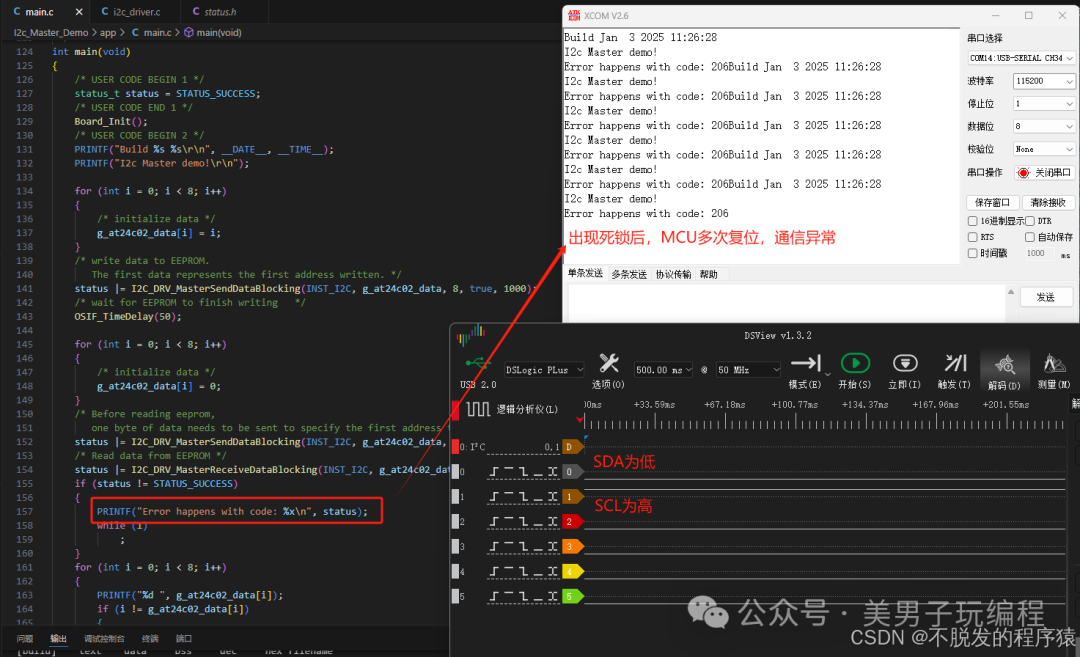

An I2C deadlock refers to a situation where the bus is stuck and unable to continue communication, usually caused by a slave device inadvertently pulling the SDA or SCL line low, preventing the master device from initiating new transactions.

Common causes of deadlocks include:

- Noise or interference: External electromagnetic interference may cause the clock edges of SCL to be lost or data errors on SDA. For example, noise may lead the slave device to mistakenly believe that communication is still ongoing, thus keeping SDA low.

- Glitches at startup: During system power-up or reset, I/O signals may experience brief pulses, causing the slave device to misinterpret the state and get the bus stuck.

- Software issues: For instance, if debugging is done at breakpoints during transactions or if the software crashes, the master device may not properly terminate communication, leaving the slave device waiting for clock pulses.

For example, if the master device restarts while reading data, and the slave device is still in transmission mode, the SDA line may be continuously pulled low, resulting in a deadlock.

1

Deadlock Detection Methods

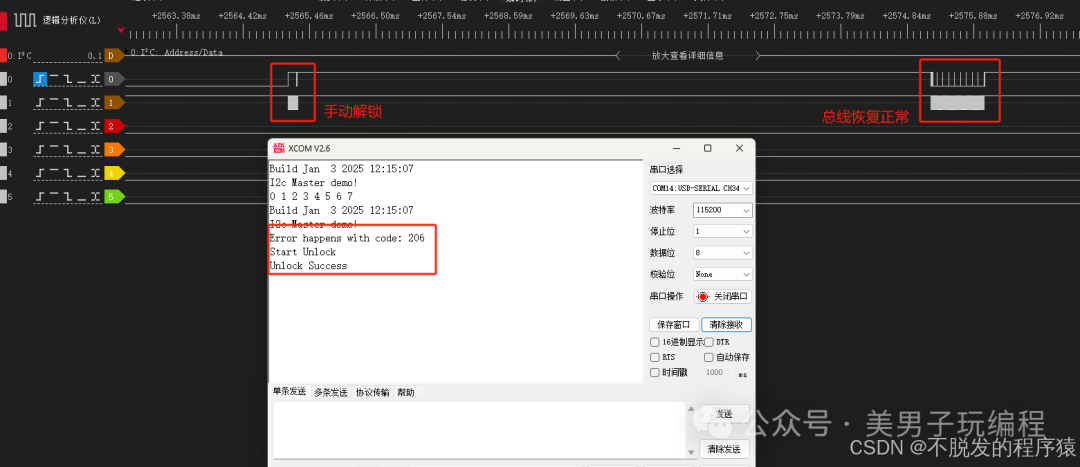

The main method for detecting I2C deadlocks is to use a timeout mechanism. During I2C communication, a timer is set, and if the bus access or data transfer is not completed within the expected time, deadlock detection is triggered.

Specific implementation can be:

- Start the timer at the beginning of each I2C transaction.

- If the transaction times out (for example, 35 ms, referring to SMBus recommendations), it is assumed that the bus may be stuck.

This method is implemented at the software level and does not require additional hardware support. Evidence suggests that this method is particularly effective in real-time systems, especially in detecting when a slave device is stuck.

2

Deadlock Prevention Measures

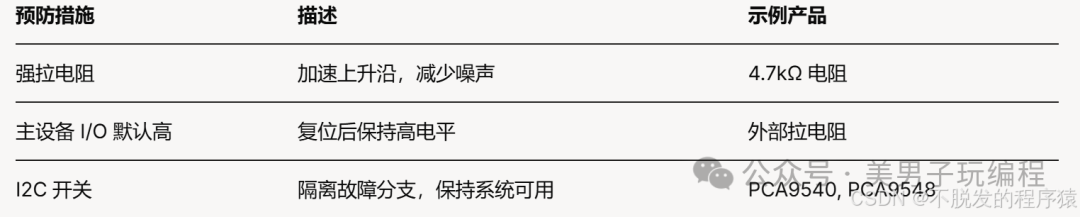

Hardware and software measures to prevent I2C deadlocks include:

Hardware Design:

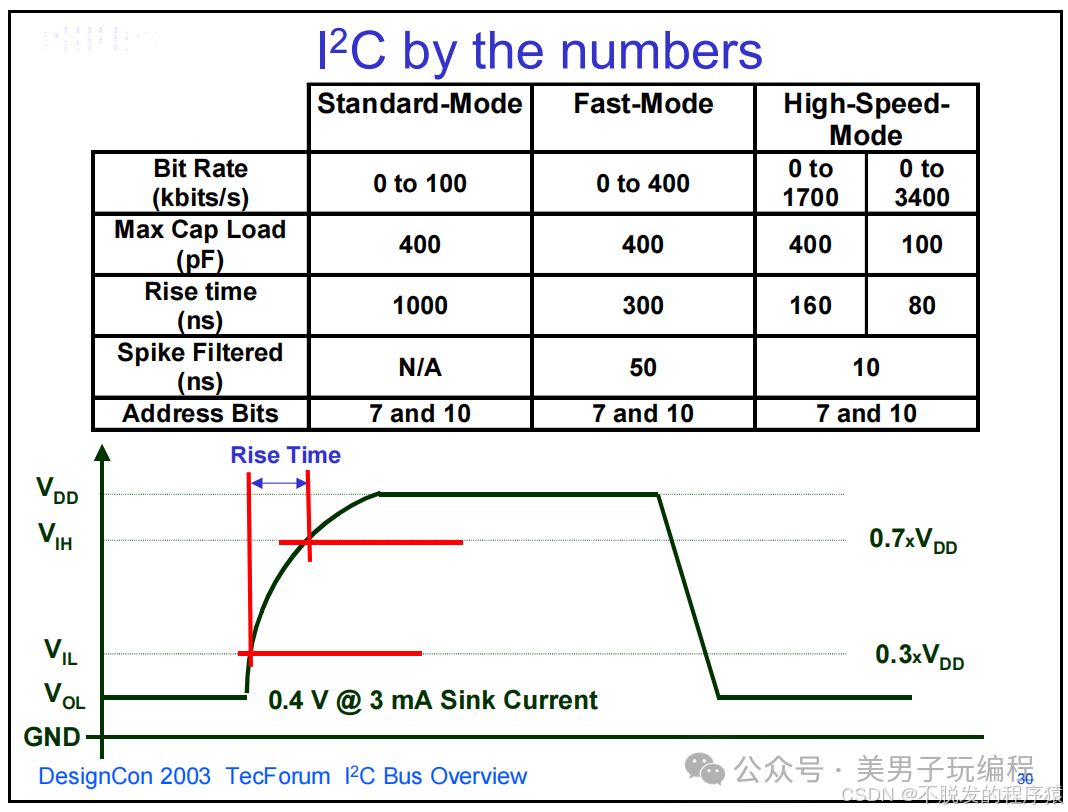

- Use strong pull-up resistors: A pull-up resistor of 4.7kΩ is recommended to speed up the rise time of SDA and SCL, reducing noise impact.

- Ensure the master device I/O defaults to high level: Maintain a high level through pull-up resistors after reset to avoid startup glitches.

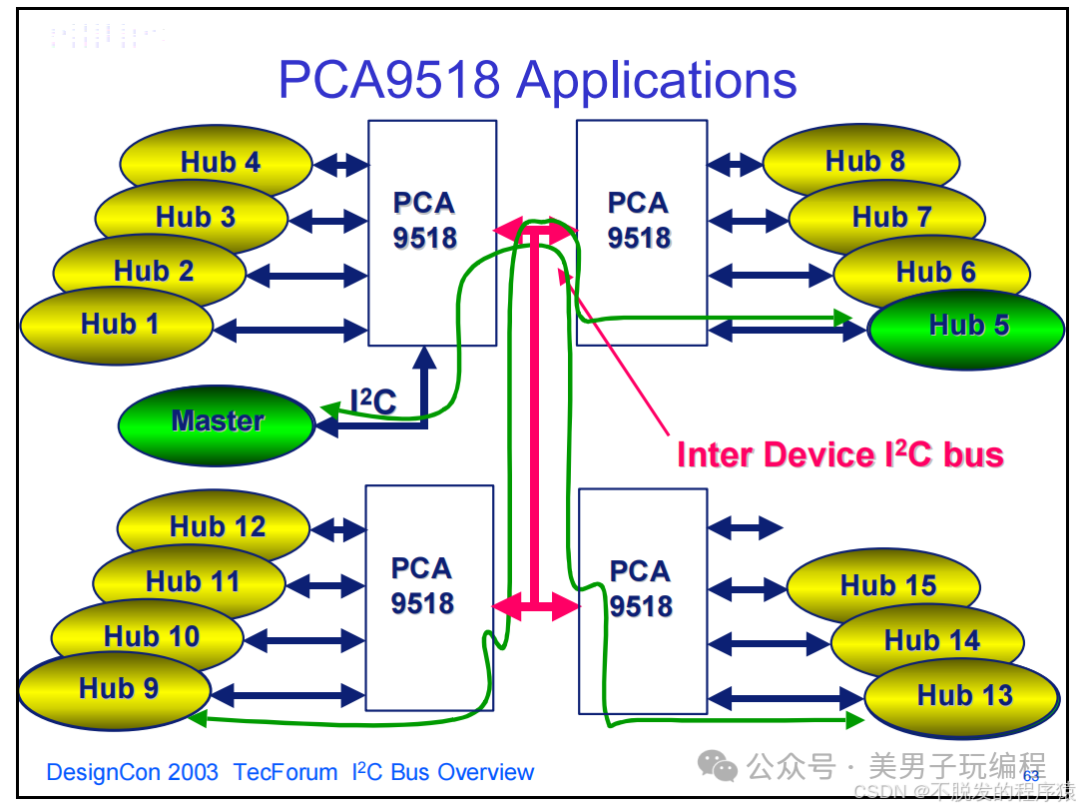

- Use I2C switches: Divide the bus into multiple branches; if one branch hangs, the faulty device can be isolated through the switch. For example, NXP’s PCA9540 (2 channels) or PCA9548 (8 channels) supports dynamic branch management.

Software Design:

- Avoid interrupting the master device program during transactions.

- Execute a recovery sequence at system startup to clear any potential initial deadlocks.

3

Deadlock Resolution Strategies

Methods for resolving I2C deadlocks can be categorized into software and hardware approaches.

Software Method

Manually generate at least 10 clock pulses from the master device to force the slave device to release the bus. This is based on the recovery mechanism of the I2C specification, which typically requires 9 clock pulses to transmit one byte of data, with an additional pulse to ensure release.

#define I2C_RECOVER_NUM_CLOCKS 10U#define I2C_RECOVER_CLOCK_FREQ 50000U#define I2C_RECOVER_CLOCK_DELAY_US (1000000U / (2U * I2C_RECOVER_CLOCK_FREQ))void i2c_recover(void) { // Configure SCL as GPIO output // Initialize SCL to high level for (uint32_t i = 0; i < I2C_RECOVER_NUM_CLOCKS; i++) { // Pull SCL low delay_us(I2C_RECOVER_CLOCK_DELAY_US); // Pull SCL high delay_us(I2C_RECOVER_CLOCK_DELAY_US); } // Reconfigure SCL to I2C mode}

Hardware Method

If the slave device has a reset pin, it can be reset through hardware signals to restore communication.Using I2C switches to isolate faulty branches keeps other branches functioning normally. For example, if a slave device on one branch hangs, it can be programmed to turn off that branch using the PCA9540.

Although I2C deadlocks can occur, they can be effectively resolved through timeout detection, strong pull-up resistor prevention, and clock pulse recovery. Hardware isolation (such as I2C switches) further enhances system reliability, making it suitable for complex embedded applications. Mastering these methods can significantly improve the stability and user experience of embedded systems.

Clickto read the original text for more exciting content~

Clickto read the original text for more exciting content~