PCI Express is a technology that often makes headlines, from the release of every generation of Intel and AMD processors to the recent significant drop in prices of M.2 interface solid-state drives. Therefore, this core bus technology of modern computers, how exactly does it work?

PCI vs. PCI Express: High Clock Speeds Determine High Speeds

Before PCIe, the mainstream bus technology was the PCI standard.

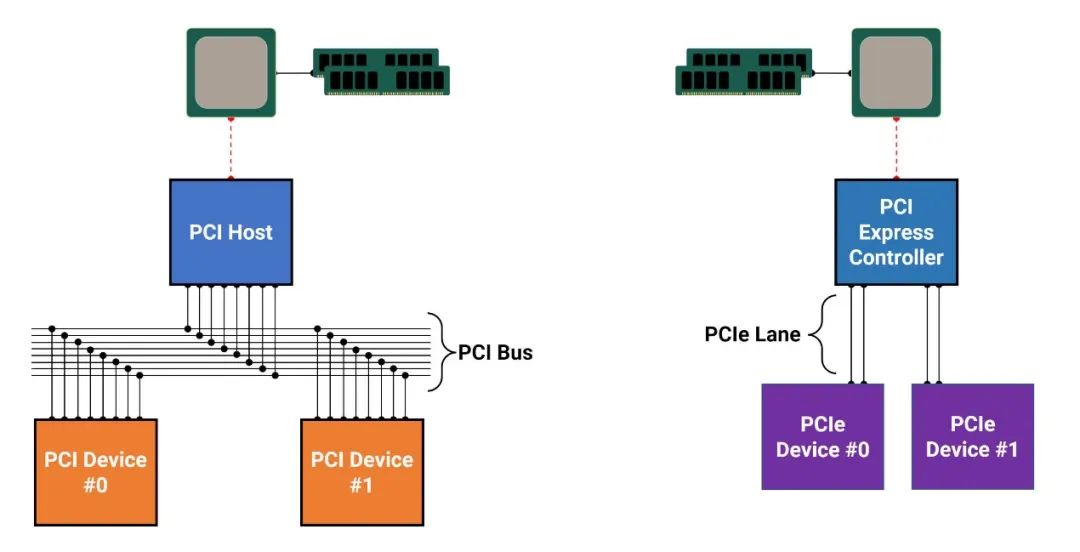

Despite the similar names, PCI Express and the PCI bus have almost nothing in common.

PCIe is a point-to-point system—on a bus line, only one device uses the bus and does not share it with any other devices—this is completely different from buses like USB, which use a centralized controller to schedule and rotate access.

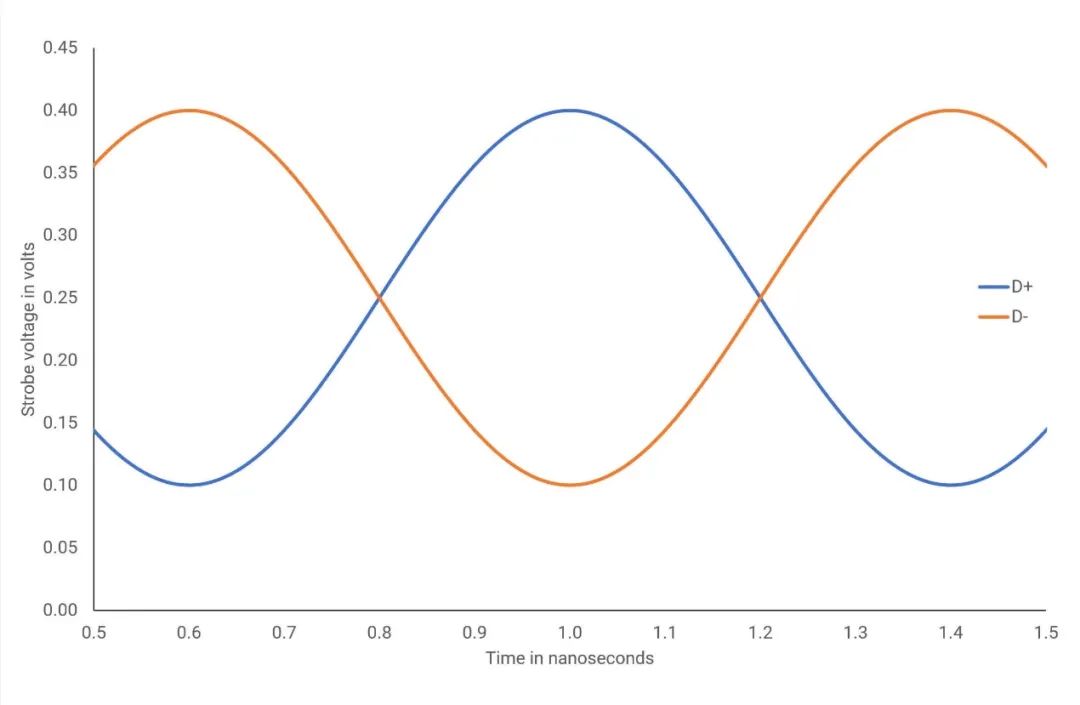

PCIe uses serial communication, sending one bit of data per clock signal cycle. This method eliminates the clock skew problems that can occur with parallel communication, ultimately allowing PCIe to operate at higher clock speeds (slow clock at 1250MHz, while the previous PCI was only 66MHz), thus forming the high-speed characteristics of the PCIe bus.

Idealized diagram of PCI Express pulse cycles

Idealized diagram of PCI Express pulse cycles

The serial nature of PCIe also reduces the number of lines required for data transmission; a complete PCI bus data channel requires 32 lines, while PCIe only needs 4 lines, which is still to accommodate full-duplex operation (see below).

This set of four lines is more commonly known as a PCIe lane, where x1 indicates one lane, x4 indicates four lanes, x16 indicates sixteen lanes, and so on.

A single-lane PCIe 1.0 bus can transfer data at a minimum rate of about 200 MB/s in one direction.

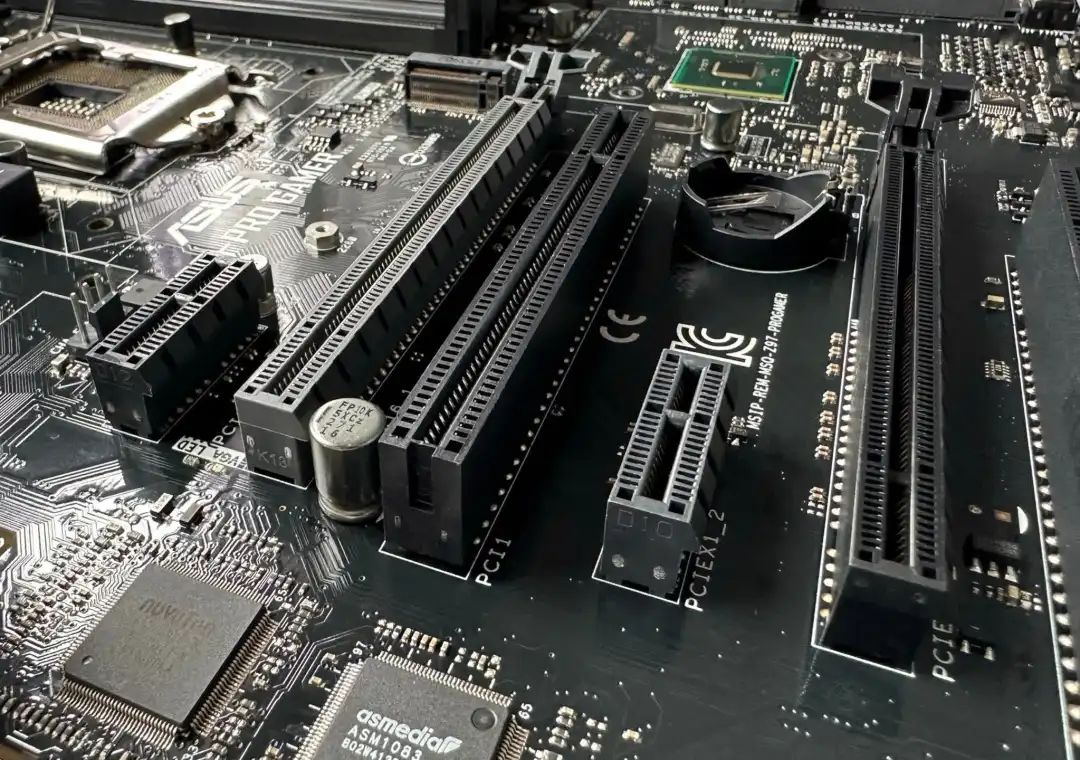

The combination of serial communication and packet-based data transmission means that PCIe slots only require relatively few pins.

The minimum pin count for any PCI Express device is 18 (not all pins need to be used), so the shortest PCIe X1 slot is quite small, needing only 18 pins.

From left to right: PCIe x1, PCIe x16, PCI, PCIe x1, PCIe x16, showing the increase in pin count as multiples of 18

From left to right: PCIe x1, PCIe x16, PCI, PCIe x1, PCIe x16, showing the increase in pin count as multiples of 18

PCI Express: Fewer Wires, High Speed, Currently the Best Internal Bus

From its inception, the purpose of creating PCIe was to expand its application as much as possible.

After more than a decade of CPU evolution, PCIe has ultimately replaced all other buses used to connect CPUs to the rest of the motherboard and most expansion card slots.

Although both AMD and Intel have developed their own point-to-point ultra-fast connection systems for CPUs, such as Intel’s QuickPath Interconnect technology connecting CPUs to traditional Northbridge chips; and AMD’s HyperTransport for direct connections to system memory and graphics card slots, they ultimately turned to using PCI Express to connect to the motherboard Southbridge.

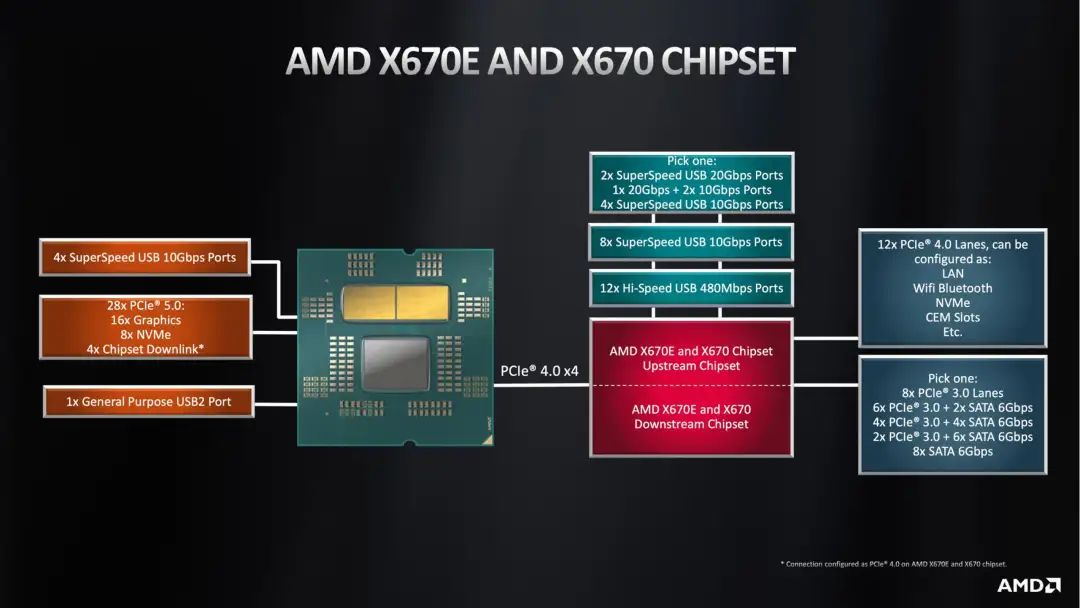

However, due to their different approaches to implementing PCIe bus controllers, the number of buses, connection speeds, and scenarios differ.

For example, AMD’s Ryzen 9 7950X processor and X670E motherboard chip have 28 and 20 PCIe lanes respectively. For the Ryzen CPU, 16 lanes are used for the graphics card slot, 8 lanes for two drives (NVME), and the remaining 4 for communication with the motherboard. The PCIe lanes in the X670E chip can be used for various data scenarios, such as network cards, Bluetooth adapters, expansion slots, and drives.

How Fast Will PCI Express Be in the Future?

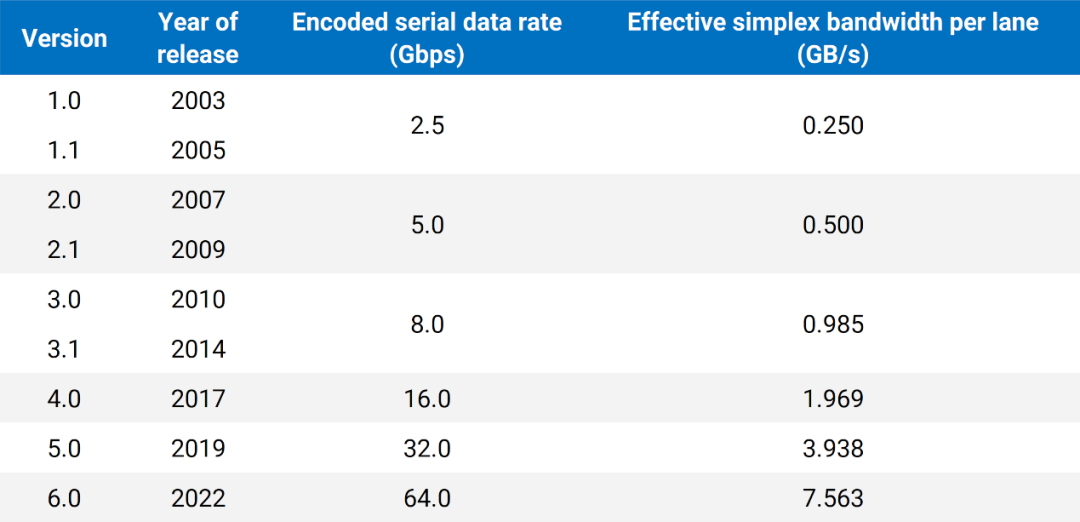

Since its first release in 2003, PCI-SIG has updated the specifications eight times.

For version 6.0, the signaling method switched from NRZ to PAM4 (first used in GDDR6X memory), and coding was abandoned to support various error correction systems.

In terms of bandwidth data, the peak throughput of a single DDR4-3200 memory is 25 GB/s, so the four channels of PCIe 6.0 can match that.

However, power supply will become a major issue for future PCIe. For a full-length x16 card, the current PCIe standard limits its power consumption to 75.9 W, which is why graphics cards currently use external power supplies.

The PCIe 7.0 specification is expected to be released in 2025, with anticipated data transfer rates doubling again to 128Gbps. It is unlikely that home PCs will achieve such speeds for many years, and the widespread adoption of PCIe 7.0 may not occur until the mid-2030s.

If this speed can be achieved, what changes in hardware performance will occur by then?

First, graphics cards will connect to the PCIe controller within the CPU, with a bandwidth of 242 GB/s. Theoretically, the core graphics card of that time could reach the performance of many current discrete graphics cards—because its bandwidth capability combined with PCIe 7.0’s memory bandwidth would allow the core graphics card to access system memory as if it were current discrete graphics accessing card memory.

Of course, with the development of dedicated applications such as artificial intelligence, data, and computing servers, whether PCIe 7.0 devices will be fast enough at that time, we will only know when the time comes.

Editor: Xiong Le

·END·