01

Using the make tool

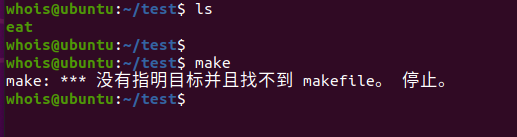

When programming on Windows, we use an IDE with a graphical interface and corresponding buttons, such as build or run, to compile. By directly entering the make command in the console, it will automatically invoke the make tool.

02

02

Makefile

The make tool will look for a makefile in the current directory, and the naming of the Makefile must be either makefile or Makefile, with both lowercase and uppercase ‘m’ being acceptable.03

Basic Syntax of makefile

-

Set vim first line indentation

vi /etc/vim/vimrc (files ending with rc are generally configuration files)Enter “set tabstop=4” on the last line, save and exit. You will find that the indentation in vim has changed to four spaces.

-

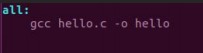

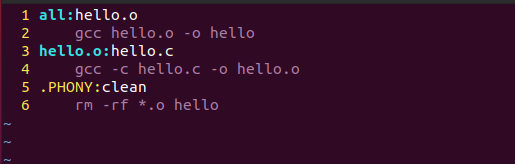

Basic Syntax of Makefile

Syntax format: Target : Dependency (tab) command Example: Target – left: all Dependency – right: none Command: gcc hello.c -o hello We can use a phony target to declare clean to avoid conflicts with files of the same name in the current directory. Phony target format:.PHONY : Target

Target – left: all Dependency – right: none Command: gcc hello.c -o hello We can use a phony target to declare clean to avoid conflicts with files of the same name in the current directory. Phony target format:.PHONY : Target 04

04

Makefile Variables and Variable Assignment

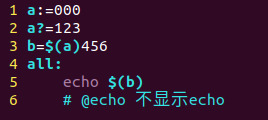

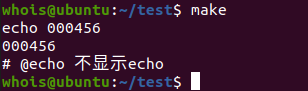

Variables can be used in many places, such as targets, dependencies, or commands.Variable assignment can use: “=”, “?=”, “:=”, “+=”Variable usage: is done through $().These variables are very helpful for subsequent learning of buildroot and yocto.

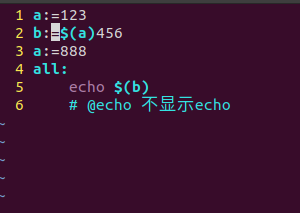

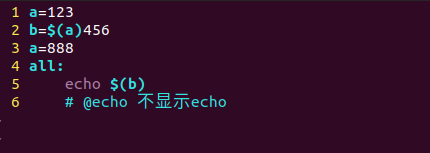

- Using “:=” to assign a variable is immediate assignment; when executing a:=123, the variable value is already determined. The first assignment is the standard.

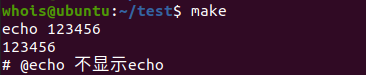

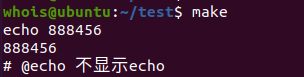

2. Using “=” for assignment is deferred assignment; the value assigned is the last specified value in the makefile. Since we finally assigned the variable a to 888, the final printout is 888456, not 123456.

3. Using “?=” for assignment means if the variable a has not been assigned a value before, it will be assigned 123; if it has already been assigned, it will retain the previous value of 000, so it prints 000456, not 123456.

Here a:= and a= are equivalent.

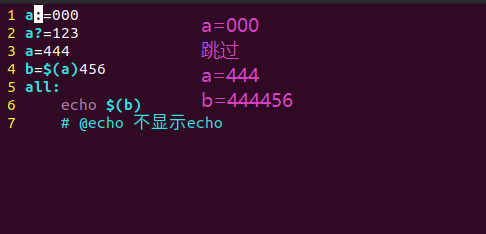

Here a:= and a= are equivalent. 4. Using “+=” for assignment is appending assignment, which adds new strings into the previously defined string. However, there will be spaces in between.

4. Using “+=” for assignment is appending assignment, which adds new strings into the previously defined string. However, there will be spaces in between. 05

05

Automatic Variables – Very Important

| $@ | Represents all targets |

| $< | Represents the first dependency file, if the dependency pattern is %, it represents a series of files. ( % is a wildcard, similar to * in Linux) |

| $^ | Represents all dependencies |

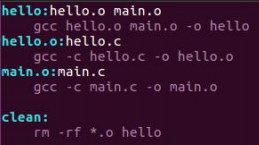

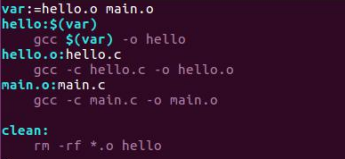

07 If there are these filesmain.chello.chello.hFirst writing: Using this makefile can also compile successfully, but once the number of files to compile increases, writing the makefile this way will become very complex. Therefore, automatic variables come into play.Second writing:

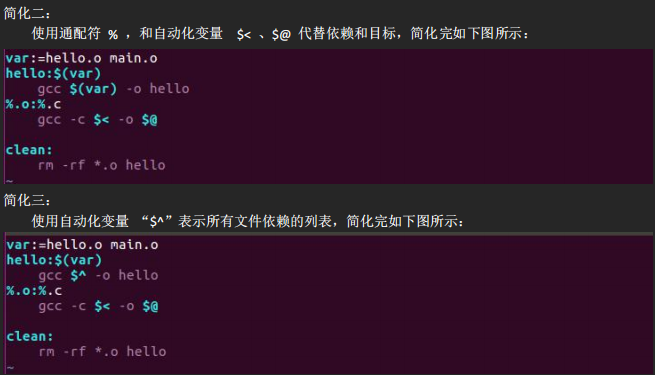

Using this makefile can also compile successfully, but once the number of files to compile increases, writing the makefile this way will become very complex. Therefore, automatic variables come into play.Second writing: Later, if we add dependency files, we can directly add them after the variable var.Third writing: Remember and save this firmly.

Later, if we add dependency files, we can directly add them after the variable var.Third writing: Remember and save this firmly.

- $< : %.o

- $@ : %.c

- $^ : hello.o main.o

08

wildcard function

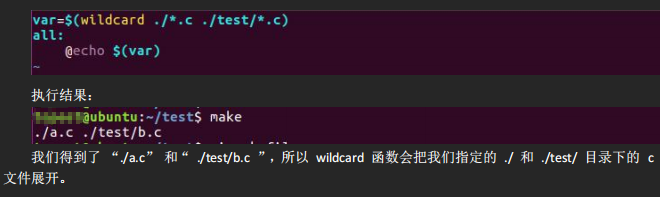

Format: $(wildcard PATTERN)

Function: Expands the specified directory

echo When prefixed with @ symbol, the echo command will not display

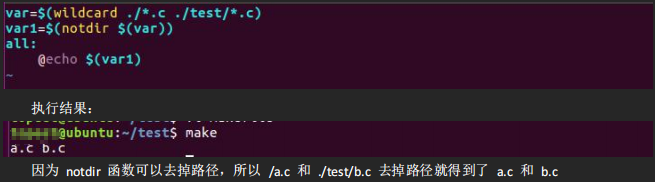

notdir function

Format: $(notdir $(var))

Function: Removes the path.

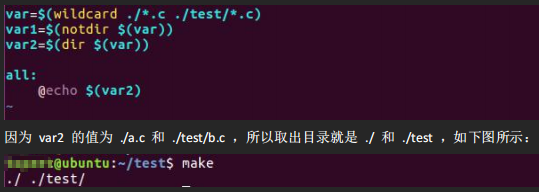

dir function

Function: Extracts the directory, where the directory refers to the part before the last backslash /; if there is no backslash /, it returns the current directory.

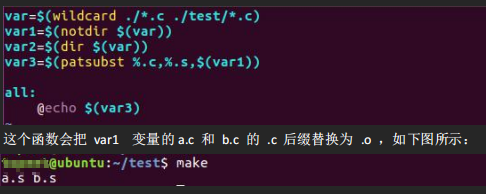

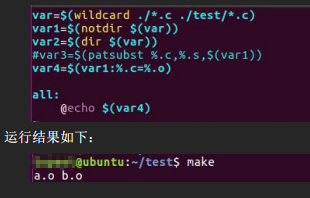

patsubst function

Format: $(patsubst original_file, target_file, file_list)

Function: Replaces file extensions

| Previous Content |

| Embedded File System Construction Techniques |

| Embedded Linux | What are BootLoader, Linux Kernel, and File System? |

| Quick Guide to Linux Root Directory |

| Linux | GCC Compilation Guide |

| Linux | Environment Variable PATH + Writing Your First Command |

| … |

Therefore, I am here

Click the card below to follow me

↓↓↓

If you find it interesting, please click

Save

Like

Look

+1

❤❤❤