Skip to content

The development of computing over the past 30 years can be roughly divided into three stages: in 1995, Microsoft Windows ushered in the PC era dominated by x86 architecture CPUs; in 2007, Apple’s iPhone opened the smartphone era dominated by Arm architecture; and in 2012, the success of the convolutional neural network AlexNet based on NVIDIA GPUs marked the beginning of the artificial intelligence (AI) era. After 10 years of rapid development, AI has expanded from the cloud to the edge and terminals, infiltrating data centers, edge servers, 5G base stations, and various smart terminals.

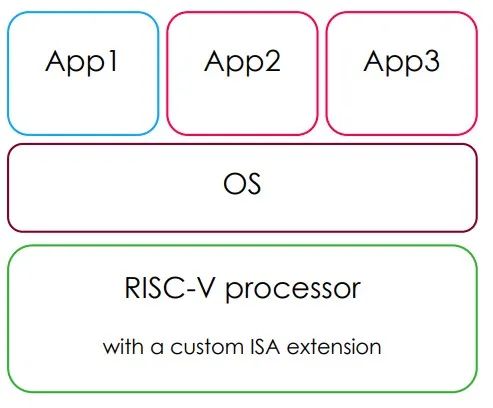

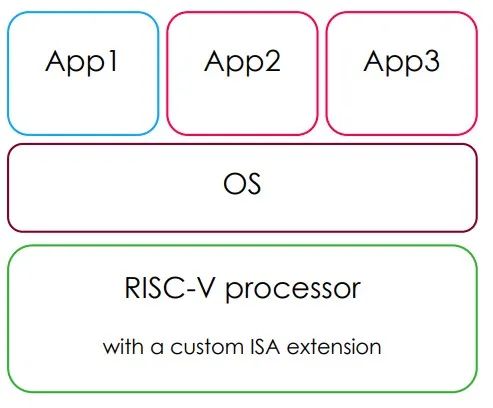

RISC-V can support both customized ISA extensions regardless of whether the application uses them. (Image: Codasip)

While Arm architecture processors are expanding from mobile phones to emerging IoT, automotive ADAS/autonomous driving, and various AI application scenarios, the open-source and flexible RISC-V microprocessor architecture is also thriving. Arm and RISC-V can be seen in an increasing number of computational application designs. At the chip level, microcontrollers (MCUs) widely used in embedded computing and AI chips aimed at edge/terminal computing have become the main battleground for Arm and RISC-V architecture microprocessor cores to face off.

Customizable Instruction Set (ISA)

The RISC-V instruction set architecture has supported basic ISA, standard extensions, and customizable ISA extension instructions from the very beginning. Arm initially did not support customized extensions, but under competitive pressure, it has started to open up customization features to Arm ecosystem partners. Even the closed x86 ecosystem has begun to loosen, with Intel recently considering external licensing and even the possibility of customizable extensions.

Due to the absence of historical burdens from Arm and x86, RISC-V ISA has a relatively simple instruction planning. It expands based on specific application needs on top of the standard instruction set, providing great flexibility for various fragmented emerging applications. For example, RISC-V vector extension (RVV) enables processor cores to accelerate single instruction stream computations of massive datasets, making it particularly suitable for the following computational tasks: machine learning, image compression processing, data encryption, audio and video multimedia processing, voice recognition, and natural language processing. These are essential computational tasks for implementing AI in emerging IoT applications.

Support for customized extension instructions in RISC-V may be the key to success or failure in certain specific applications. Using customized extension instructions does not conflict with its main ISA and can support general RISC-V software simultaneously.

Codasip CTO Zdeněk Přikryl

In the above RISC-V software stack schematic, RISC-V processors with customizable ISA extensions can support real-time embedded operating systems (such as embOS, FreeRTOS, or RT-Thread), as well as operating systems with higher performance requirements (such as Linux, Android, or Windows). App1 on it does not require performance enhancements and does not use customized ISA extension instructions, only needing standard compilers. App2 and App3, however, utilize customized ISA extensions to enhance performance, thus requiring compilers compatible with customized ISA extensions.

Codasip is a European developer focused on RISC-V and Domain Specific Architecture (DSA) processor solutions. According to the company’s CTO Zdeněk Přikryl, for any MCU manufacturer, whether based on RISC-V or Arm architecture, if a general design is adopted, there will inevitably be compromises in performance. Artificial intelligence typically requires high processing performance, while edge applications require low power consumption and small size for MCUs. However, the reality is that general processor cores rarely meet this combination of performance requirements. For some edge AI applications, adding custom instructions to the RISC-V processor core can enable algorithms to be executed thoroughly within relatively limited processing resources. Customizable domain-specific architectures can make processors more suitable for AI algorithms and software workloads.

Impact of Microprocessor Cores on Performance

The architecture of processor cores is a key factor affecting processor performance; advanced architectures have more powerful instruction sets and superior computational units, thus possessing greater computing power. Moreover, under the same processor architecture, using different implementation technologies can also affect performance. For example, implementing CPU no-wait instruction access using bus concurrency architecture technology can improve computational performance by more than 30% compared to processors of the same level.

To measure MCU performance, two dimensions must be considered: on one hand, the main frequency, and on the other hand, the core architecture. The main frequency is easy to understand, akin to speed; for MCUs of the same architecture, the higher the main frequency, the faster the MCU’s speed. Advanced architectures allow cores to execute more instructions in a unit of time, meaning more tasks can be completed. Therefore, if we only look at the main frequency, we cannot determine the performance of MCUs of different architectures. Generally speaking, the more advanced the core architecture, the more instructions and data it can process in a unit of time.

Thus, it can be seen that the higher the main frequency and the more advanced the core architecture of the MCU, the better its performance. This can be likened to a race: when the stride length is the same (i.e., the architecture is the same), the runner with a faster stride frequency (higher main frequency) runs faster; and when the stride frequency is the same (same main frequency), the runner with a longer stride (higher instruction execution efficiency) runs faster.

Of course, other factors such as memory capacity and wafer process also influence processor performance to some extent. For example, the larger the cache, the higher the processor’s data access hit rate, and the greater the efficiency of core computation.

Generally, embedded MCUs primarily demand stability, reliability, safety, and real-time control characteristics from processor cores, while edge AI chips often require higher computing performance and storage capacity, as well as lower power consumption. For MCUs, the differences between different architecture cores are more reflected in software and development ecosystems rather than performance. For AI chips, in addition to the functional requirements of general processors, there will also be specific needs for algorithms and applications, which may require relevant computational power and performance, such as SIMD/Vector capabilities, DSP capabilities, and openness of extended instructions.

According to Yan Junsheng, the market director of Guomin Technology, Arm cores currently have the largest market share in the MCU market, with a relatively complete ecosystem and a mature architecture, making them widely applicable. However, Arm cores are limited by a closed instruction set architecture, licensing, and patent costs, which make fine-grained customization inconvenient. Additionally, there are significant performance differences among different Arm cores, and as the working frequency of Arm cores increases, the power consumption of MCU chips rises quickly. Therefore, how to reduce power consumption while using high-frequency Arm core MCUs is a considerable challenge for MCU manufacturers.

For general MCUs, the benefit of adopting Arm architecture is compatibility with the mainstream ecosystem, allowing for full reuse of existing application designs and lowering the design-in threshold. Most domestic MCU manufacturers have entered the MCU market based on this concept, which has proven to meet the development needs of China’s semiconductor industry. However, this approach has also increasingly highlighted the issue of homogenization in domestic MCU chips. If competition is limited to price, it does not benefit the entire industry and most of the companies within it. Some capable and visionary domestic MCU manufacturers have recognized this and begun to shift toward differentiated product planning and market competition.

In terms of processor core selection, in addition to Arm, RISC-V is now also an option. The RISC-V architecture boasts advantages such as low power consumption, low cost, open-source, modularity, simplicity, small area, and fast speed. However, its shortcomings are also apparent, mainly reflected in: the development toolchain is not user-friendly; the software ecosystem is not well-developed; and there is a lack of a rich selection of chip series. Ultimately, this is due to its relatively short development time and incomplete overall ecosystem.

Wei Lu, product marketing director at Aipute Microelectronics, stated that their company has consistently adhered to the use of proprietary cores and various IPs required for MCUs since its inception. Although achieving autonomous control of microprocessors through technological innovation is quite challenging, the value and advantages of persistence are also very evident. To address the current pain points of RISC-V MCU development, Aipute has collaborated with PingTouGe to create a “development editing toolchain.” Currently, the compiler can support “what you see is what you get,” supporting multiple RTOS including AliOS, with a complete ecosystem from the bottom layer to the basic system and core components.

To address the richness of selection issues faced by engineers and developers, Aipute has developed a complete series of RISC-V products: from 20Pin to 200Pin, from 32KHz to 2GHz, and from 32-bit to 64-bit processors. Wei Lu indicated that the company plans to release 25 series, covering more than 300 models of RISC-V products, targeting consumer, industrial, and automotive-grade applications.

Edge AI Chips: Arm or RISC-V?

Shiqing Technology is a startup developing edge AI chips based on RISC-V cores. Its co-founder and president, Yu Xin, expressed his views on Arm and RISC-V architectures in an interview with “Electronic Engineering Magazine.” Arm has a better ecosystem, including development tools, operating system support, a broad developer base, and a wider range of selectable models. However, AI chips require efficient support for various artificial intelligence algorithms, which is not inherently a strength of general processors. Simply relying on Arm’s native extensions like VFP and NEON has limited effectiveness. Therefore, AI chips need more specialized processor cores, which fall outside the scope covered by Arm (or general processors).

Shiqing Technology President Yu Xin

In contrast to Arm, the openness, modularity, and scalability of RISC-V will help AI processors better integrate with application and algorithm characteristics and requirements. Shiqing has also explored this aspect, with the Timesformer processor developed based on the RISC-V architecture designed specifically for edge voice and vision algorithm characteristics, which is a unique advantage of RISC-V.

In terms of software and ecosystem, AI chips based on RISC-V architecture still face some challenges. However, since AI applications often require chip manufacturers to provide a complete solution of chips + algorithms, the underlying architecture is not particularly sensitive to most downstream customers, which somewhat masks the shortcomings of RISC-V.

Best Match Between Microprocessors and Applications

For processor architecture, there is no absolute good or bad; it depends on the specific application requirements. General-purpose chips using Arm architecture will have inherent advantages that are difficult to shake in the short term. Arm is a 32-bit Reduced Instruction Set (RISC) processor architecture with a wide range of applications, currently mainly in smartphones, PCs, servers, automotive, IoT, and artificial intelligence solutions. In emerging application fields, particularly in embedded product application areas such as smart control, edge computing, and portable products, Arm architecture processors have very good application prospects. For example, IoT, industrial networking and control, smart appliances and smart home IoT terminals, consumer electronics, motor drives, battery and energy management, smart meters, medical electronics, automotive electronics, security, biometrics, communications, sensors, machine automation, etc., are all very suitable for Arm architecture MCU products.

According to Yan Junsheng, Guomin Technology is currently primarily developing a series of chip products based on Arm Cortex-M0, Cortex-M4, Cortex-M7, etc., focusing on general MCUs, security chips, and wireless RF, which are now widely used in electric control, industrial, automotive, medical, IoT, and consumer fields, and are expanding into subdivided MCU markets such as automotive-grade MCUs, digital power, and motor control.

IoT applications and those with strong specificity are more suitable for MCUs based on RISC-V. RISC-V is an ISA suitable for both general MCUs and specific domain accelerators (such as AI), with modularity and customizability advantages, meaning it can be deployed to meet the specific needs of applications, thus tailoring solutions for various IoT application requirements. IoT applications belong to a long-tail market, which is highly fragmented, with many relatively small but diverse applications emerging continuously. As for specialized markets, RISC-V, with its open-source and low-cost characteristics, is even more at home.

Wei Lu revealed that Aipute plans to enter both the general market and specialized market in 2022. In the specialized market, its new products will cover fields the company has already entered, including motor drives, touch buttons, HMI, intelligent voice, and other application scenarios; in the general market, it plans to launch general-purpose MCUs with a variety of rich peripherals, covering frequencies from 48MHz to 250MHz, and storage capacities from 64K/8K to 512K/128K, including key peripherals such as USB, CAN, SDIO, and encryption engines.

Yu Xin from Shiqing believes that for specialized AI chips, which require better integration of algorithms and hardware through innovative underlying architecture, RISC-V may be a good choice, allowing chip developers more flexibility to design the microarchitecture of processors, and some underlying and basic toolchains and instruction sets do not need to be reinvented, which is largely a feasible approach to leverage RISC-V’s strengths while avoiding its weaknesses.

Future Ecosystem Development

Arm’s reduced instruction set has low power consumption, low cost, high concurrent processing efficiency, and fast upgrade speed, and it inherently has IoT genes, giving it a competitive advantage in 5G network infrastructure and IoT application fields. The current trend for Arm is to develop towards servers and high-performance computing, which may encroach on more x86 market share. The markets Arm will face in the future mainly include servers, mobile terminals, ICT infrastructure, automotive, and embedded scenarios. The overall participatory capability and market growth space of the Arm ecosystem in these applications are enormous, presenting very good development prospects.

Currently, the vast majority of the entire MCU ecosystem is still dominated by Arm architecture, with many manufacturers choosing to replicate and be compatible with European and American chips. However, we are gradually seeing more domestic manufacturers join the RISC-V ranks. Now, end customers are also beginning to accept RISC-V MCUs.

When it comes to building the RISC-V MCU ecosystem, Wei Lu stated that Aipute will work with PingTouGe to create a complete RISC-V toolchain and MCU ecosystem. In addition to RISC-V’s CSI component certification, Aipute will also establish the “1520” ecosystem standard, which means getting started in 1 day, prototyping in 5 days, and mass production in 20 days. Currently, Aipute has independently developed a complete development kit, including debugging tools, programming tools, and compilation software, which can make it very convenient for engineers to use RISC-V MCUs.

The RISC-V ecosystem has rapidly developed in embedded applications. With the emergence of high-performance RISC-V cores, the RISC-V ecosystem will develop towards high-performance computing. However, in the foreseeable future (say within 3-5 years), it will be relatively difficult for RISC-V to compete head-on with Arm. Yu Xin believes that RISC-V may first break through in some niche areas and then seek to expand, which is a more realistic path. Certain niche areas are less sensitive to ecosystem and have higher differentiation requirements, such as edge AI chips. Additionally, for the domestic market, areas with higher demands for “independent control” are also fertile ground for RISC-V development, such as the Xinchuang industry.

In summary, as a latecomer and relatively niche RISC-V, it needs to leverage its advantages of openness, simplicity, scalability, and modularity, fully capitalize on its strengths while avoiding weaknesses, to gradually grow and eventually form a situation of “three-way contention” with Arm and x86.

Original from EET Electronic Engineering Magazine

Wei Lu, product marketing director at Aipute Microelectronics, stated that their company has consistently adhered to the use of proprietary cores and various IPs required for MCUs since its inception. Although achieving autonomous control of microprocessors through technological innovation is quite challenging, the value and advantages of persistence are also very evident. To address the current pain points of RISC-V MCU development, Aipute has collaborated with PingTouGe to create a “development editing toolchain.” Currently, the compiler can support “what you see is what you get,” supporting multiple RTOS including AliOS, with a complete ecosystem from the bottom layer to the basic system and core components.

To address the richness of selection issues faced by engineers and developers, Aipute has developed a complete series of RISC-V products: from 20Pin to 200Pin, from 32KHz to 2GHz, and from 32-bit to 64-bit processors. Wei Lu indicated that the company plans to release 25 series, covering more than 300 models of RISC-V products, targeting consumer, industrial, and automotive-grade applications.

Edge AI Chips: Arm or RISC-V?

Shiqing Technology is a startup developing edge AI chips based on RISC-V cores. Its co-founder and president, Yu Xin, expressed his views on Arm and RISC-V architectures in an interview with “Electronic Engineering Magazine.” Arm has a better ecosystem, including development tools, operating system support, a broad developer base, and a wider range of selectable models. However, AI chips require efficient support for various artificial intelligence algorithms, which is not inherently a strength of general processors. Simply relying on Arm’s native extensions like VFP and NEON has limited effectiveness. Therefore, AI chips need more specialized processor cores, which fall outside the scope covered by Arm (or general processors).

Shiqing Technology President Yu Xin

In contrast to Arm, the openness, modularity, and scalability of RISC-V will help AI processors better integrate with application and algorithm characteristics and requirements. Shiqing has also explored this aspect, with the Timesformer processor developed based on the RISC-V architecture designed specifically for edge voice and vision algorithm characteristics, which is a unique advantage of RISC-V.

In terms of software and ecosystem, AI chips based on RISC-V architecture still face some challenges. However, since AI applications often require chip manufacturers to provide a complete solution of chips + algorithms, the underlying architecture is not particularly sensitive to most downstream customers, which somewhat masks the shortcomings of RISC-V.

Best Match Between Microprocessors and Applications

For processor architecture, there is no absolute good or bad; it depends on the specific application requirements. General-purpose chips using Arm architecture will have inherent advantages that are difficult to shake in the short term. Arm is a 32-bit Reduced Instruction Set (RISC) processor architecture with a wide range of applications, currently mainly in smartphones, PCs, servers, automotive, IoT, and artificial intelligence solutions. In emerging application fields, particularly in embedded product application areas such as smart control, edge computing, and portable products, Arm architecture processors have very good application prospects. For example, IoT, industrial networking and control, smart appliances and smart home IoT terminals, consumer electronics, motor drives, battery and energy management, smart meters, medical electronics, automotive electronics, security, biometrics, communications, sensors, machine automation, etc., are all very suitable for Arm architecture MCU products.

According to Yan Junsheng, Guomin Technology is currently primarily developing a series of chip products based on Arm Cortex-M0, Cortex-M4, Cortex-M7, etc., focusing on general MCUs, security chips, and wireless RF, which are now widely used in electric control, industrial, automotive, medical, IoT, and consumer fields, and are expanding into subdivided MCU markets such as automotive-grade MCUs, digital power, and motor control.

IoT applications and those with strong specificity are more suitable for MCUs based on RISC-V. RISC-V is an ISA suitable for both general MCUs and specific domain accelerators (such as AI), with modularity and customizability advantages, meaning it can be deployed to meet the specific needs of applications, thus tailoring solutions for various IoT application requirements. IoT applications belong to a long-tail market, which is highly fragmented, with many relatively small but diverse applications emerging continuously. As for specialized markets, RISC-V, with its open-source and low-cost characteristics, is even more at home.

Wei Lu revealed that Aipute plans to enter both the general market and specialized market in 2022. In the specialized market, its new products will cover fields the company has already entered, including motor drives, touch buttons, HMI, intelligent voice, and other application scenarios; in the general market, it plans to launch general-purpose MCUs with a variety of rich peripherals, covering frequencies from 48MHz to 250MHz, and storage capacities from 64K/8K to 512K/128K, including key peripherals such as USB, CAN, SDIO, and encryption engines.

Yu Xin from Shiqing believes that for specialized AI chips, which require better integration of algorithms and hardware through innovative underlying architecture, RISC-V may be a good choice, allowing chip developers more flexibility to design the microarchitecture of processors, and some underlying and basic toolchains and instruction sets do not need to be reinvented, which is largely a feasible approach to leverage RISC-V’s strengths while avoiding its weaknesses.

Future Ecosystem Development

Arm’s reduced instruction set has low power consumption, low cost, high concurrent processing efficiency, and fast upgrade speed, and it inherently has IoT genes, giving it a competitive advantage in 5G network infrastructure and IoT application fields. The current trend for Arm is to develop towards servers and high-performance computing, which may encroach on more x86 market share. The markets Arm will face in the future mainly include servers, mobile terminals, ICT infrastructure, automotive, and embedded scenarios. The overall participatory capability and market growth space of the Arm ecosystem in these applications are enormous, presenting very good development prospects.

Currently, the vast majority of the entire MCU ecosystem is still dominated by Arm architecture, with many manufacturers choosing to replicate and be compatible with European and American chips. However, we are gradually seeing more domestic manufacturers join the RISC-V ranks. Now, end customers are also beginning to accept RISC-V MCUs.

When it comes to building the RISC-V MCU ecosystem, Wei Lu stated that Aipute will work with PingTouGe to create a complete RISC-V toolchain and MCU ecosystem. In addition to RISC-V’s CSI component certification, Aipute will also establish the “1520” ecosystem standard, which means getting started in 1 day, prototyping in 5 days, and mass production in 20 days. Currently, Aipute has independently developed a complete development kit, including debugging tools, programming tools, and compilation software, which can make it very convenient for engineers to use RISC-V MCUs.

The RISC-V ecosystem has rapidly developed in embedded applications. With the emergence of high-performance RISC-V cores, the RISC-V ecosystem will develop towards high-performance computing. However, in the foreseeable future (say within 3-5 years), it will be relatively difficult for RISC-V to compete head-on with Arm. Yu Xin believes that RISC-V may first break through in some niche areas and then seek to expand, which is a more realistic path. Certain niche areas are less sensitive to ecosystem and have higher differentiation requirements, such as edge AI chips. Additionally, for the domestic market, areas with higher demands for “independent control” are also fertile ground for RISC-V development, such as the Xinchuang industry.

In summary, as a latecomer and relatively niche RISC-V, it needs to leverage its advantages of openness, simplicity, scalability, and modularity, fully capitalize on its strengths while avoiding weaknesses, to gradually grow and eventually form a situation of “three-way contention” with Arm and x86.

Original from EET Electronic Engineering Magazine