From the development history of ASIC in the era of Bitcoin mining machines, we can see the unique advantages of ASIC in the field of dedicated parallel computing: high computing power, low power consumption, low cost, and strong specialization. The TPU recently exposed by Google, which is dedicated to artificial intelligence deep learning computing, is actually also an ASIC.The era of artificial intelligence is gradually approaching, and these traditional chips, FPGA and ASIC, will usher in a new explosion in the age of artificial intelligence.

In-Depth Introduction to FPGA

FPGA Beginner’s Tutorial

Heterogeneous Computing Chip (ASIC/FPGA etc.) Technology Collection (1)

Heterogeneous Computing Chip (ASIC/FPGA etc.) Technology Collection (2)

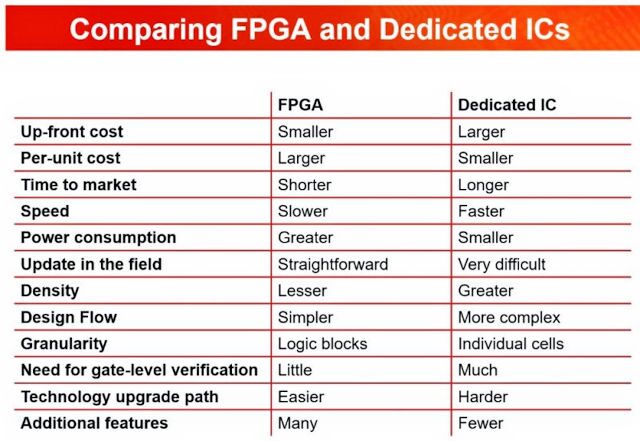

Ates Berna, General Manager and Managing Partner of ElectraIC in Istanbul, Turkey, recently posted a comparative summary chart on LinkedIn showing the differences between FPGA and ASIC.

Although this is not a detailed chart, I believe it serves as a good icebreaker when you need a relatively complex high-performance, non-standard IC to solve design challenges, leading to discussions about your choices between FPGA and ASIC.

I often receive questions about FPGA versus ASIC, and I think it is valuable to discuss the chart published by Berna. Therefore, here is a more detailed line-by-line discussion of the items in the chart:

This is my line-by-line discussion of the chart:

Upfront Cost:The upfront cost of ASIC is very high. First, there is the cost of ASIC development tools. You need a fairly large toolchain to develop ASIC, which you must rent or purchase, and you need to know how to use these tools. If your design team does not have this knowledge, you need to include the cost of training the team in your upfront cost list. In addition, you will incur significant NRE (non-recurring engineering) costs, which can amount to hundreds of thousands or millions of dollars, paid to the silicon foundry to build your ASIC. NRE costs cover mask manufacturing and inspection, reserving a spot in the foundry’s busy manufacturing schedule to produce your ASIC, chip testing and sorting, packaging, and final testing. In contrast, FPGA are off-the-shelf components, so there are no foundry NRE costs, and FPGA tools are much cheaper than ASIC design tools, roughly three orders of magnitude lower. Depending on the FPGA, you can even purchase parts through distribution and receive them the next day.

Unit Cost:This is where ASIC shines. Because you typically design ASIC to meet your exact design requirements, you only purchase the silicon that you really want. There is little or no waste. Therefore, assuming you have projected product sales to justify creating an ASIC, the unit cost of ASIC should be lower than that of FPGA. This is because FPGA has a large chip overhead. First, your design may not be able to utilize 100% of any given FPGA. If you’re lucky, you might achieve a 90% utilization rate. Typically, you may not be able to use up to 10% or more of the FPGA resources to meet routing and timing goals due to excessive routing congestion, and if you try to use the entire FPGA, the signals become too long and slow. Additionally, the signal routing matrix on FPGA is very rich to ensure you can route your design on FPGA.

Time to Market:So far, FPGA is the leader in time to market. If you are ready to manufacture the PCB, you can ship on the same day the FPGA design is completed. All you need to do is flash the final configuration into the EEPROM on the board, test it, package it, and ship it. In contrast, when you finish the ASIC design, you send the design to the silicon foundry and hold a tape-out party. Then, you wait for months while the foundry accepts your design, inspects it, manufactures the chips, tests the chips, packages the chips, and sends the packaged ASIC back to you. When you receive the completed ASIC box, you can build and test your circuit board. Meanwhile, similar products from competitors, based on FPGA, will have been on the market while you wait for the ASIC from the foundry. If time to market is critical for you, FPGA may be your best choice.

Speed:Assuming your designers know what they are doing, ASIC extracts the highest performance from any given IC process node. Due to the large (capacitive) programmable routing matrix of FPGA, performance is typically lost by about an order of magnitude compared to ASIC for any given IC process node.

Power Consumption:This is not obvious, but the silicon inefficiency of FPGA in unit cost and speed also increases the power consumption of FPGA compared to ASIC. All those extra routing matrix transistors on FPGA leak, leading to higher static power consumption. The longer routing inherent in FPGA due to the Manhattan routing required in ordered FPGA adds capacitance to each routing, leading to higher dynamic power consumption. However, FPGA vendors can combat the extra power consumption in their FPGA.

For example, Lattice Semiconductor chose a 28nm FDSOI process technology for its Nexus FPGA to reduce static power consumption. There are many such design techniques to reduce power consumption, but FPGA has large chips, and large chips have a lot of capacitance.

Field Update:This is easy to understand. SRAM-based FPGA can be easily reprogrammed in the field. Change the configuration stored in flash memory and update your design. In the early days of FPGA design, you had to pull the old configuration EPROM or EEPROM out of its IC socket and insert a new configuration to perform a field update. Nowadays, you are likely to perform reprogrammable designs through USB or JTAG ports. Some final product designs allow for wireless updates, although there are many security issues with allowing wireless hardware updates.

In contrast, updating ASIC typically requires a board swap (known as a service call in the wireless industry). Some ASIC designs incorporate embedded FPGA (eFPGA) structures from eFPGA vendors such as Achronix, Flex Logix, Menta, or QuickLogic to allow for a limited number of field updates without service calls. If you want to adopt this approach, you can even obtain an open-source FPGA structure generator and toolkit called OpenFPGA. However, if you embed FPGA architecture in ASIC, then isn’t ASIC becoming FPGA?

Density:Because device density is closely related to unit cost, the same argument applies to FPGA versus ASIC, with a slight increase. In any given process technology, due to the routing overhead and resource utilization constraints of FPGA, you can always design a larger device, one with more resources than ASIC, as mentioned above.

Design Process:Unlike ASIC, the physical design of FPGA has already been completed for you and verified by the FPGA vendor before you see the device, although there may be errata. You typically use a vendor’s toolchain to design the FPGA configuration, although some wealthy design companies use ASIC-level layout and routing tools from one of the big three EDA vendors: Cadence, Siemens/Mentor, and Synopsys. For ASIC design, you typically take a mixed approach, purchasing EDA tools from the big three EDA companies, and perhaps also some additional design tools from new EDA startups that have not yet been absorbed by one of the big three EDA companies.

Granularity:The digital granularity of ASIC is a gate, or in some cases, a transistor. FPGA must have a coarser granularity, about a logic unit. Otherwise, the routing overhead of FPGA would become completely impractical. This difference in granularity between ASIC and FPGA leads to higher unit costs for FPGA and a relative lack of density.

Gate-Level Verification Requirement:Both FPGA and ASIC require design-level verification. However, FPGA is not gate-level fine-grained, so they do not require gate-level verification. You place each gate in the ASIC design, so you need to verify each gate.

Technology Upgrade Path:Theoretically, upgrading from one FPGA series to the next within a vendor’s product line is easier. For example, migrating designs through three Xilinx 7 series devices: Artix, Kintex, and Virtex is relatively easy. However, migrating to FPGA from other vendors also means migrating to the design tools of other FPGA vendors, which is not particularly easy, although it is not as difficult as some might think. Engineers have managed to master the toolchains of more than one FPGA vendor. They just complain a lot when making changes. ASIC has no technology upgrade path. To upgrade ASIC, you need to design, verify, and manufacture a new ASIC.

Additional Features:Here, I must differ from the chart above. Although FPGA vendors have long sought to add additional functional blocks to their FPGA, almost anything available on FPGA can be designed or purchased and placed on ASIC. This may not be easy, but it is usually possible. Claims about ASIC IP include embedded FPGA IP. Perhaps the chart is intended to suggest that it is easier for FPGA vendors to stuff many other cutting-edge features into their parts. For example, FPGA vendors have been leading the way in high-speed SerDes design for the past 20 years. If you want a fast SerDes, you are likely to find the fastest in the latest devices from FPGA vendors, especially Achronix, Intel, and Xilinx.

Of course, there are many other design considerations that did not appear in the chart above. For example, there is an intermediate step between FPGA and ASIC—structured ASIC—which offers many (but not all) of the advantages of ASIC at lower NRE costs compared to ASIC. Fifteen years ago, many companies offered structured ASIC and suggested they were the next generation of gate arrays. For many commercial reasons, only one commercial structured ASIC vendor remains—Intel, which acquired the last structured ASIC vendor, eASIC, in 2018.

Although the chart that triggered this article is not comprehensive, it does provide a good starting point for making decisions between FPGA and ASIC. So far, this article should have hit a nerve with someone, so please feel free to comment and let us know your thoughts.

Source: Semiconductor Industry Observation

Download Links:

ASIC Technology Thematic Analysis

China ASIC Chip Industry Quality Report

2020 China FPGA Chip Industry Research Report

China FPGA Chip Industry Report

2021 Overview of the Chinese Intelligent Network Card Industry

Source: Smart Computing Chip World

Reprint Statement: ReprintThis article from this account must indicate the author and source. If there are copyright issues with articles published by this account, please leave a message for processing. Thank you.

Recommended Reading

For more architecture-related technology knowledge summaries, please refer to the “Architect’s Full Store Technical Data Pack” related e-book (37 bookstechnical data pack summary details can be obtained through “Read the original text” link).

The entire store content is continuously updated. Now order the “Full Store Technical Data Pack (All)”, and you can enjoy free updates of the entire store content in the future, with a price of only 198 yuan (original total price 350 yuan).

Warm Reminder:

Scan the QR code to follow the public account, click Read the original text link to get the “Architect’s Technical Full Store Data Pack Summary (All)” e-book data details.