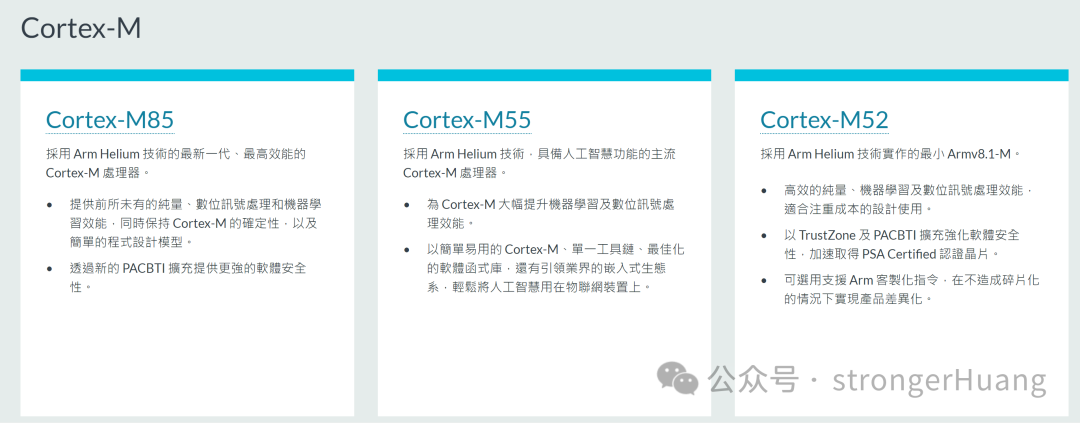

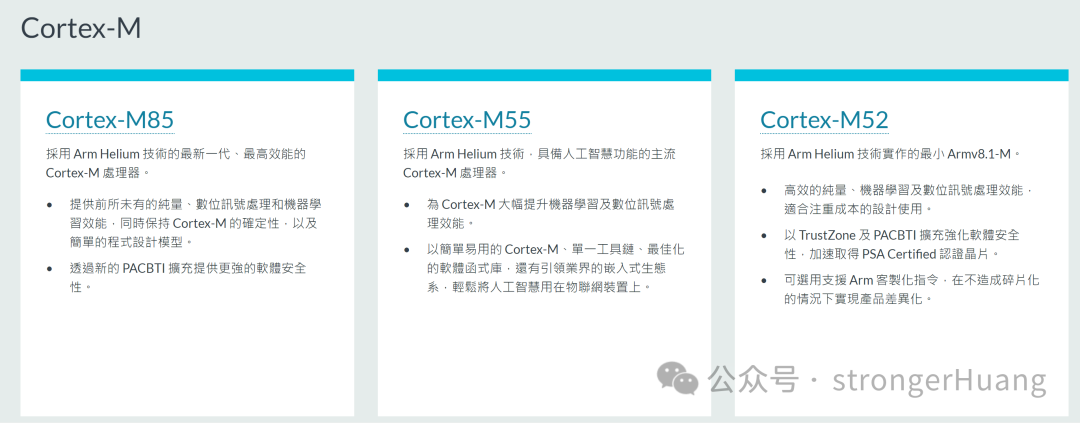

Cortex-M is an ARM core aimed at MCUs, which has been around for about 20 years, with the most classic being the Cortex-M3 core, which is one of the most widely used cores on the market today.

As of now (September 2024), the latest and most powerful microcontroller core is the Cortex-M85.

The Cortex-M85 has upgraded many features compared to the Cortex-M3 core, making it stronger.

So, as a regular user (developer), what are the differences in using Cortex-M85 and Cortex-M3 core microcontrollers?

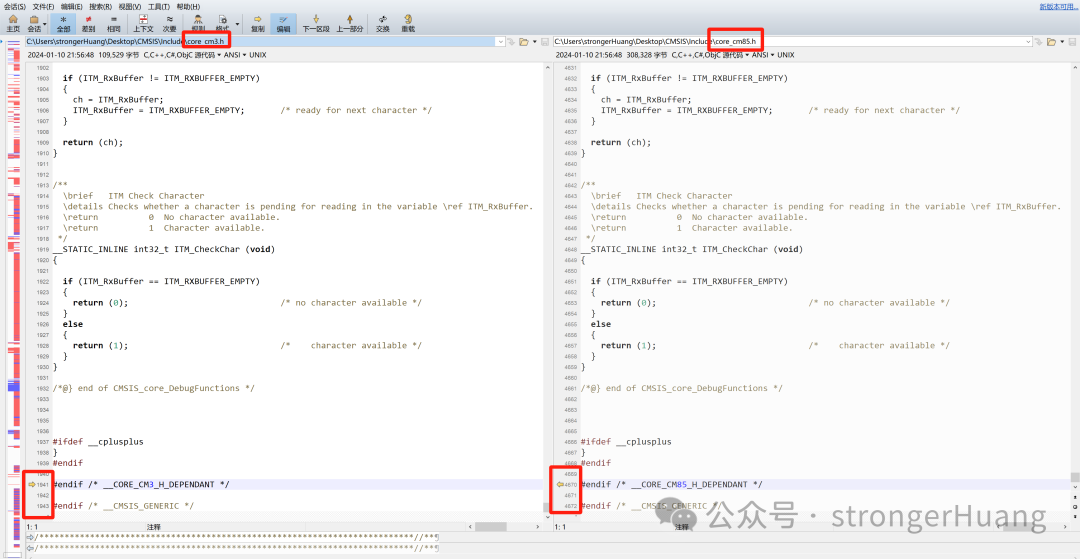

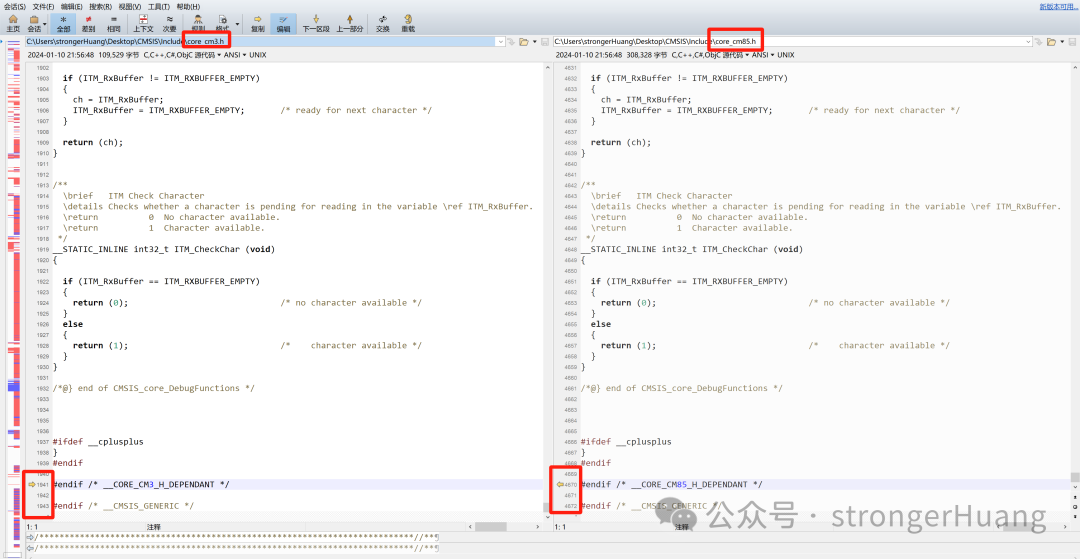

Microcontroller developers often interact with the core_cm3.h (core_cm85.h) files, which define most of the content related to the core. The interfaces we call most often are also from here.

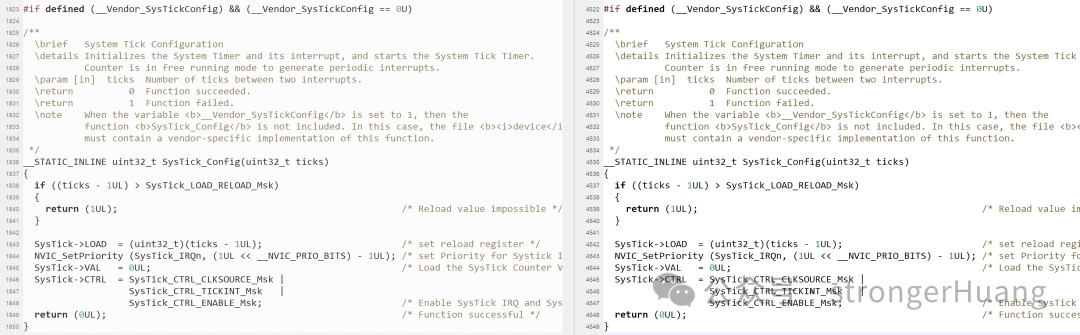

Let’s compare these two source files:

By comparing the source code, you will intuitively find that cm85 has significantly more lines of code than cm3, with 1943 lines and 4672 lines respectively. Of course, with so many more lines, the left side shows more red (differences).

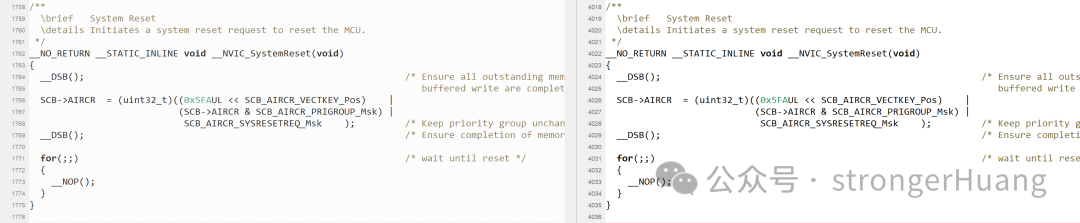

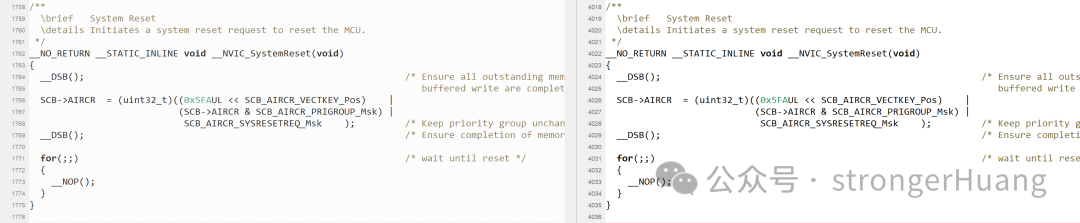

Although the left side shows more red, most of it is just additional lines and macro definitions. Upon closer inspection, many parts are actually the same, such as the system reset function we commonly use:

__NO_RETURN __STATIC_INLINE void __NVIC_SystemReset(void){ __DSB(); /* Ensure all outstanding memory accesses included buffered write are completed before reset */ SCB->AIRCR = (uint32_t)((0x5FAUL << SCB_AIRCR_VECTKEY_Pos) | (SCB->AIRCR & SCB_AIRCR_PRIGROUP_Msk) | SCB_AIRCR_SYSRESETREQ_Msk ); /* Keep priority group unchanged */ __DSB(); /* Ensure completion of memory access */ for(;;) /* wait until reset */ { __NOP(); }

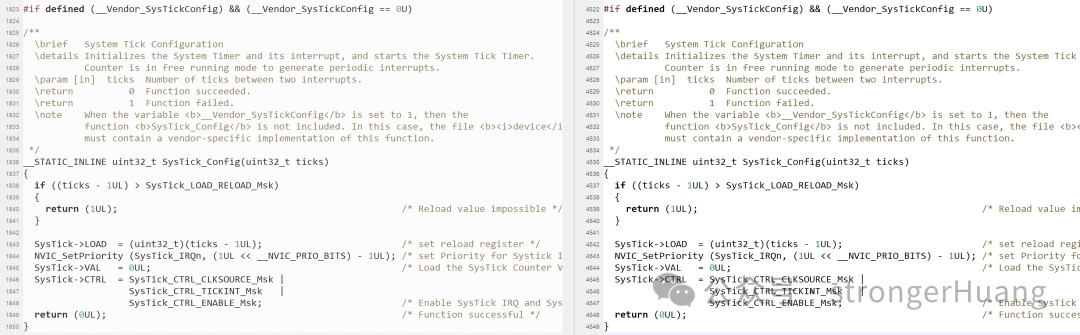

For example, the system Tick configuration function:

__STATIC_INLINE uint32_t SysTick_Config(uint32_t ticks){ if ((ticks - 1UL) > SysTick_LOAD_RELOAD_Msk) { return (1UL); /* Reload value impossible */ } SysTick->LOAD = (uint32_t)(ticks - 1UL); /* set reload register */ NVIC_SetPriority (SysTick_IRQn, (1UL << __NVIC_PRIO_BITS) - 1UL); /* set Priority for Systick Interrupt */ SysTick->VAL = 0UL; /* Load the SysTick Counter Value */ SysTick->CTRL = SysTick_CTRL_CLKSOURCE_Msk | SysTick_CTRL_TICKINT_Msk | SysTick_CTRL_ENABLE_Msk; /* Enable SysTick IRQ and SysTick Timer */ return (0UL); /* Function successful */}

In fact, you will find that the commonly used function interfaces on the Cortex-M3 microcontroller are basically the same as on the CM85, which also indicates that most interfaces of the CM85 are backward compatible with CM3.

Cortex-M85 Microcontroller SysTick

The timer is a commonly used module in microcontrollers, whether for delays or RTOS heartbeats (system clocks), timers are used. Therefore, ARM has considered this situation and integrated a SysTick module into every Cortex-M core.

Here, we will discuss the usage of SysTick in conjunction with the Renesas RA8D1 (Cortex-M85 core) microcontroller.

Using e2 studio and FSP software package

The software package provided by the tool is actually the most practical. Here, using IO toggling and SysTick delay as an example, I will guide you step by step to create a project and demonstrate the effect.

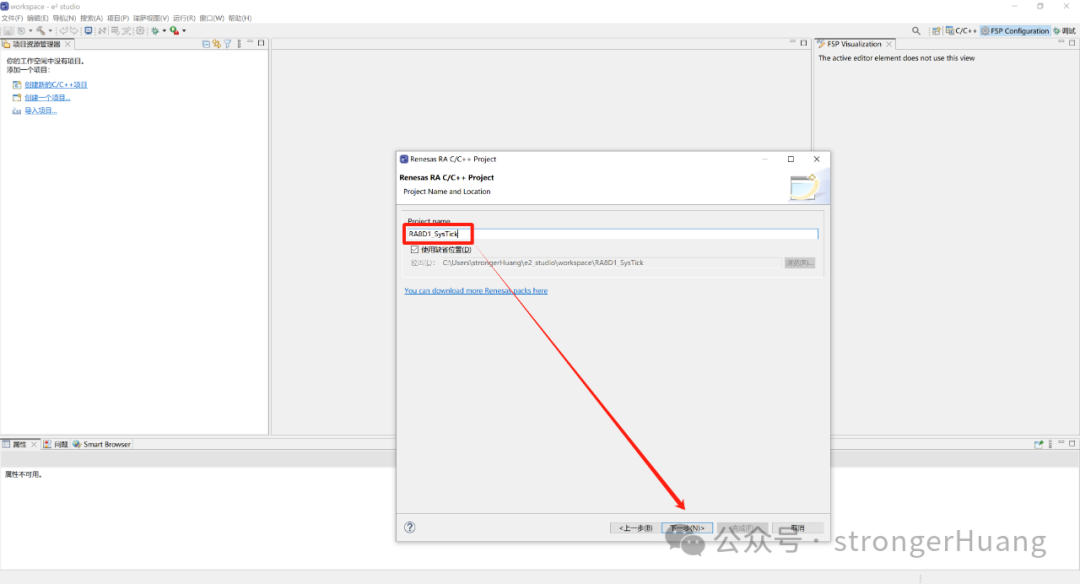

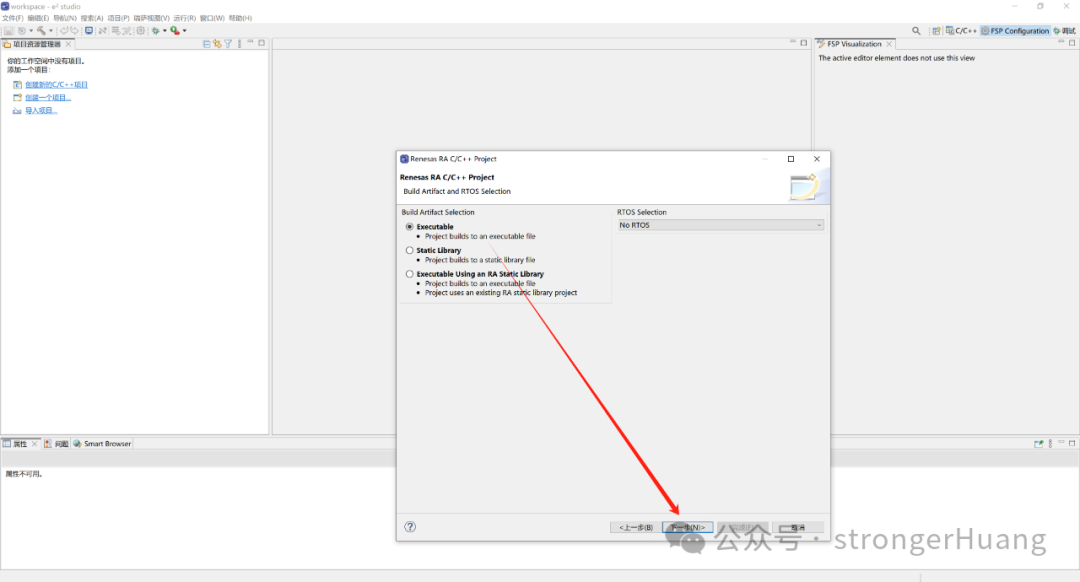

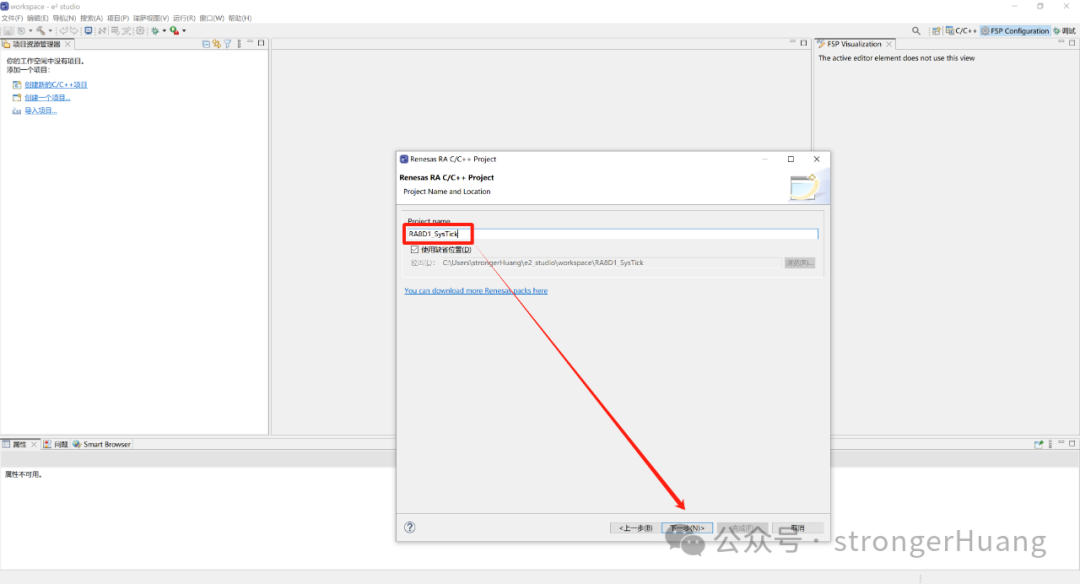

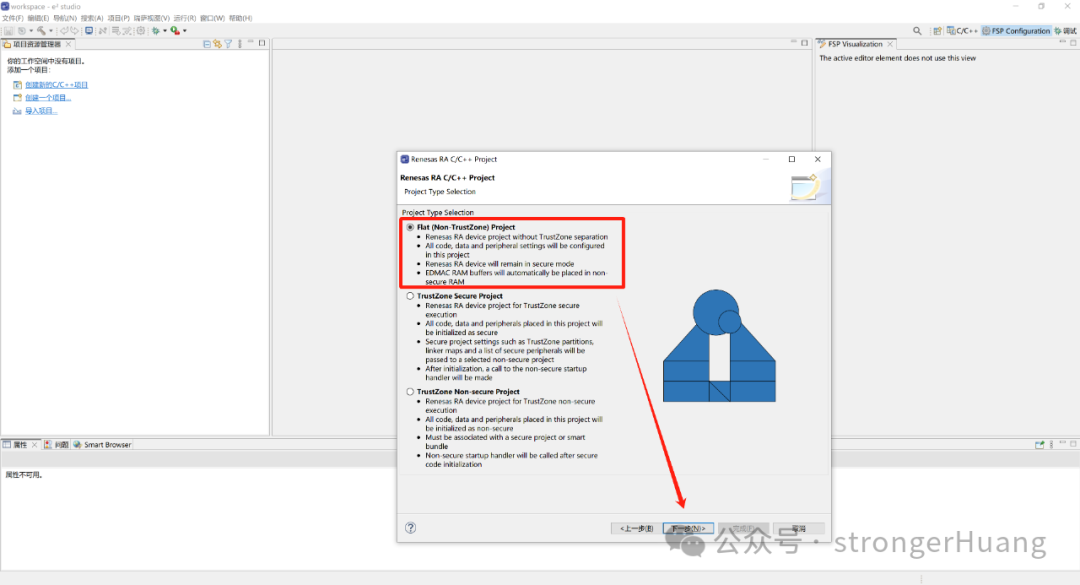

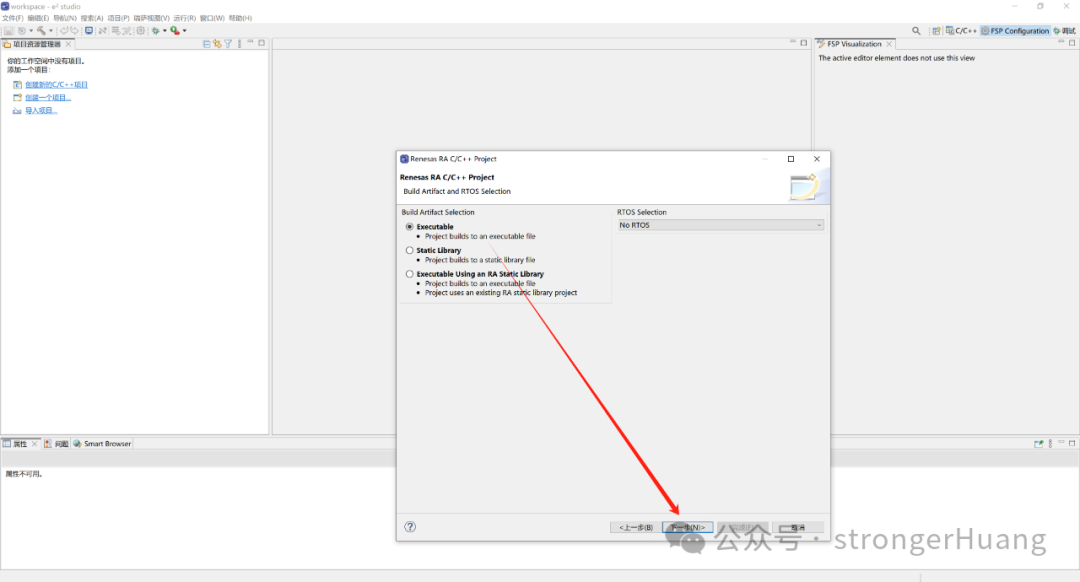

1. Open e2 studio to create a microcontroller project

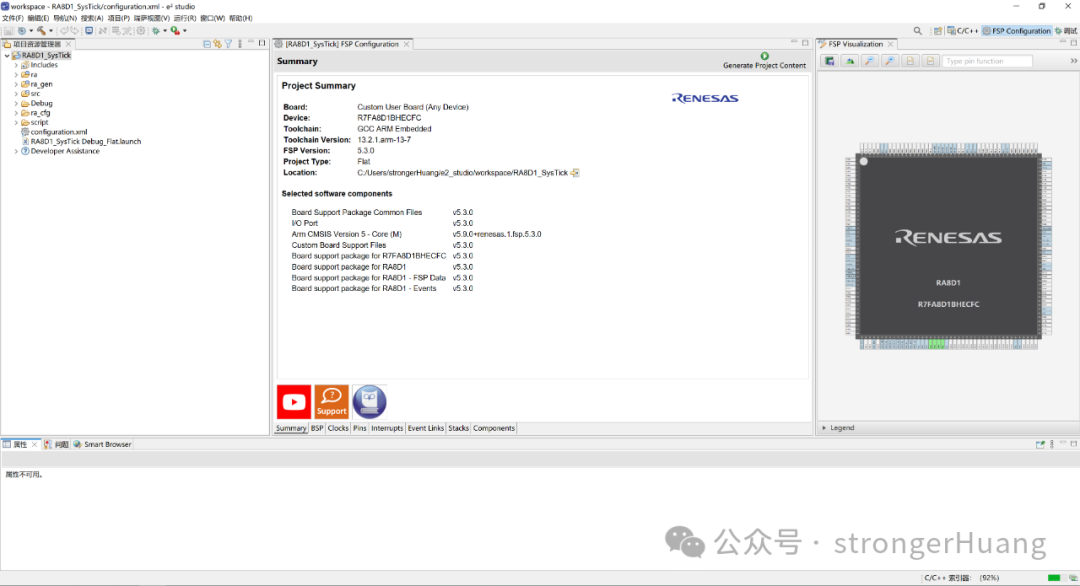

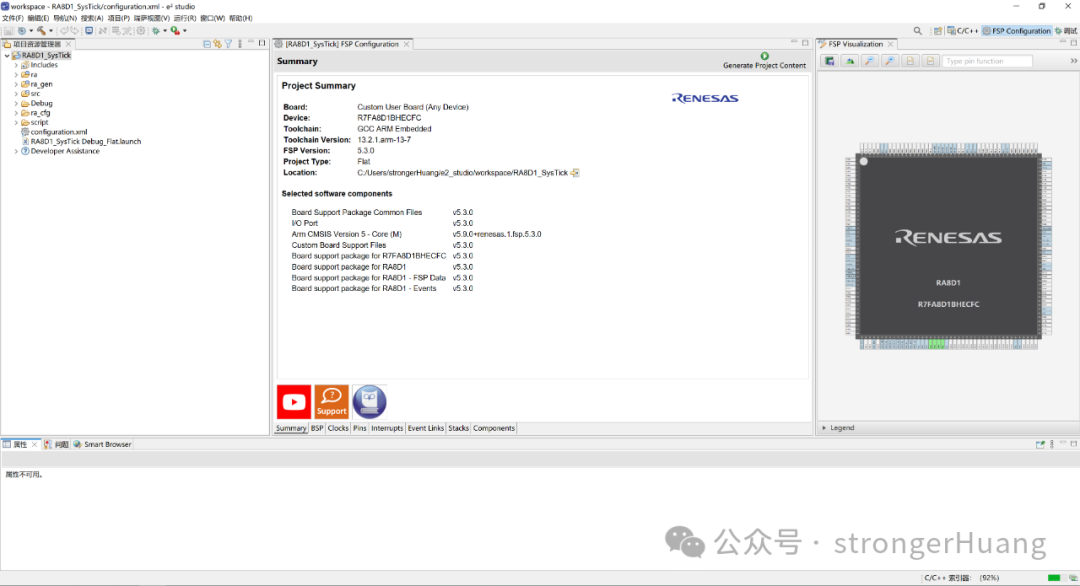

We named the project: RA8D1_SysTick

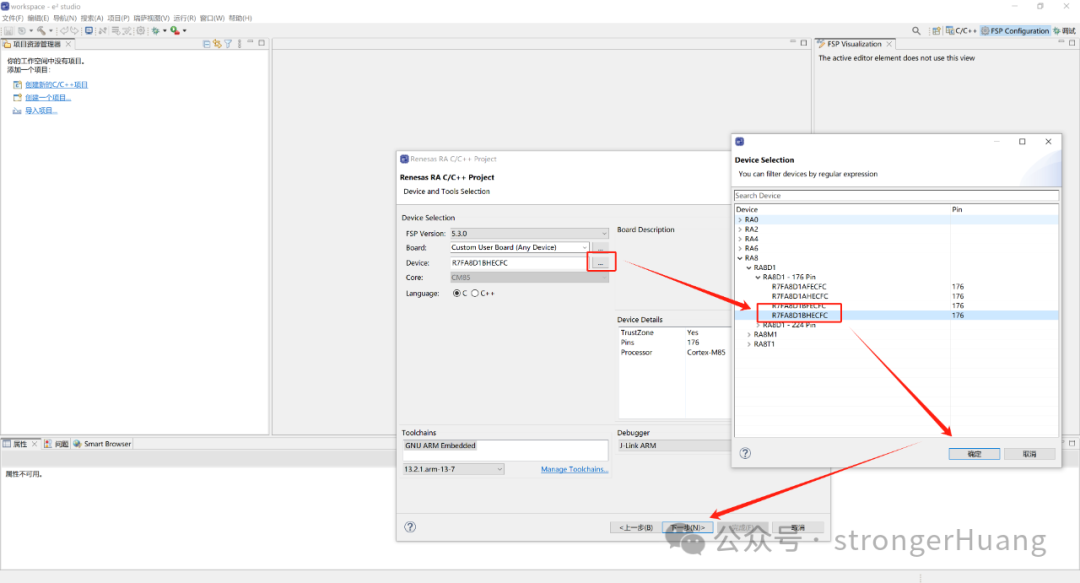

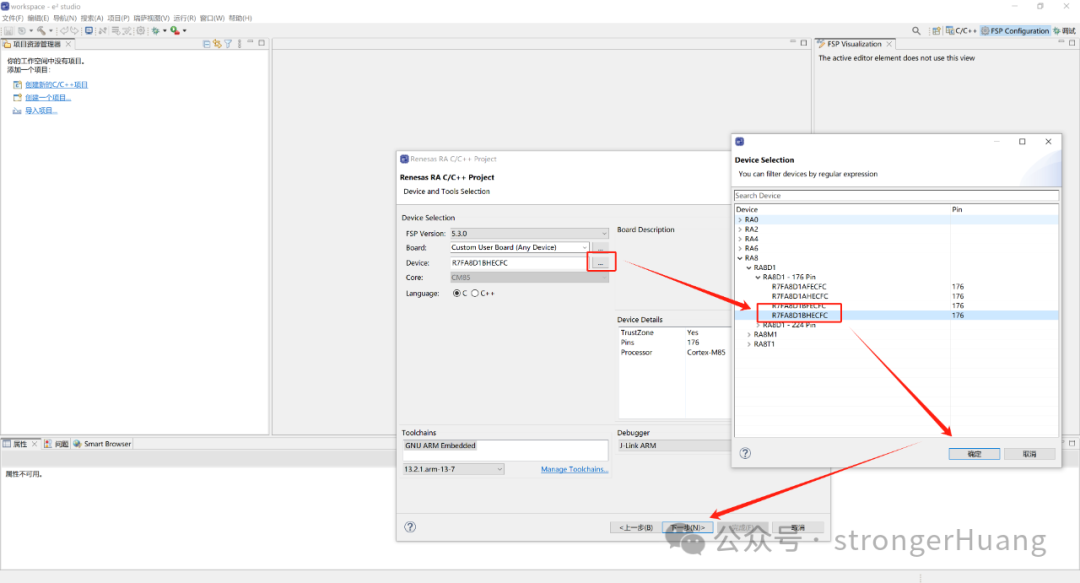

Select the corresponding chip model: R7FA8D1BEC

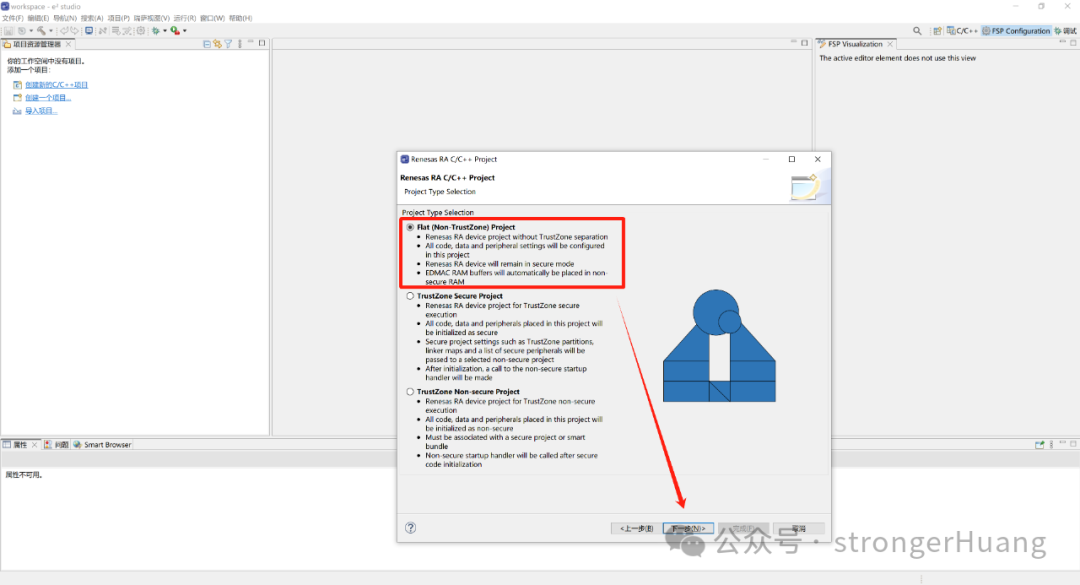

Basically, you just need to click a few buttons, and a complete project will be created.

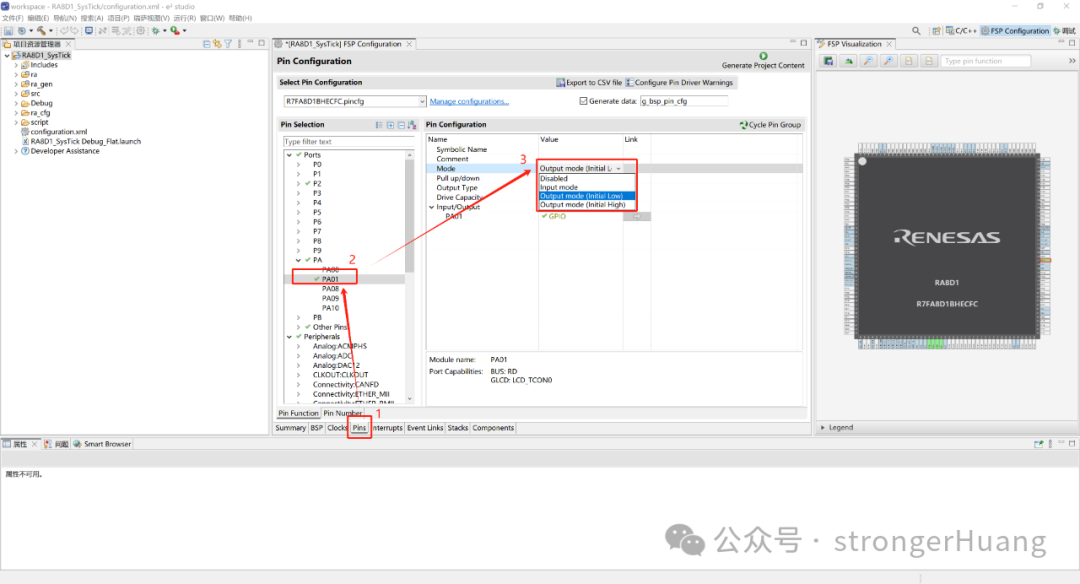

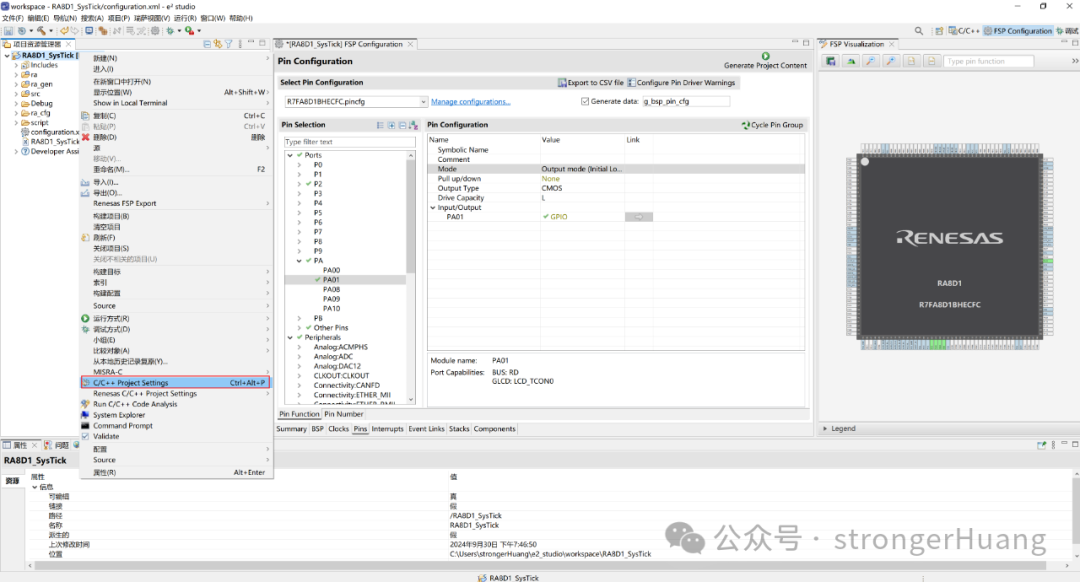

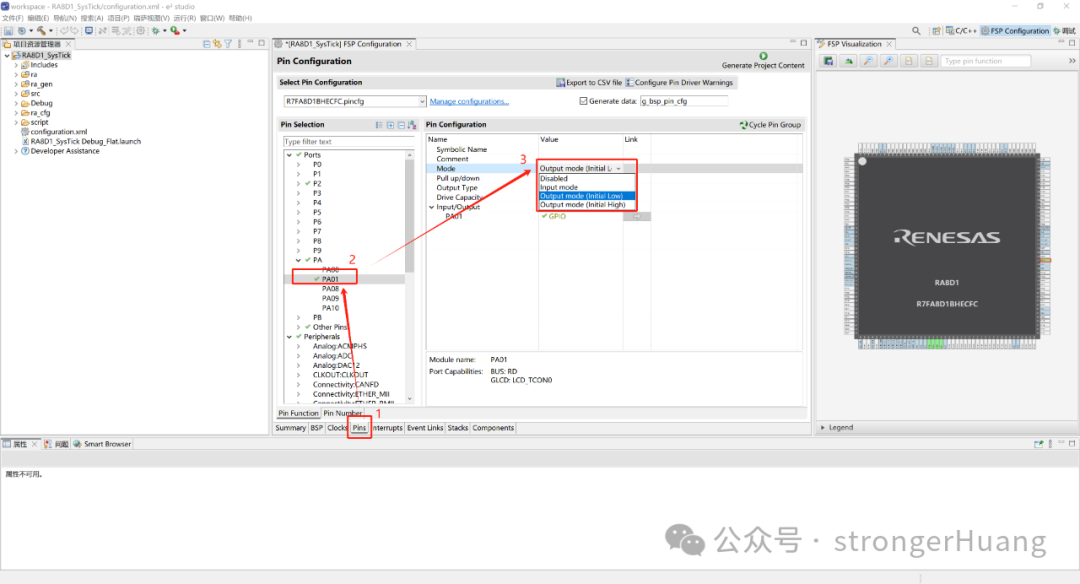

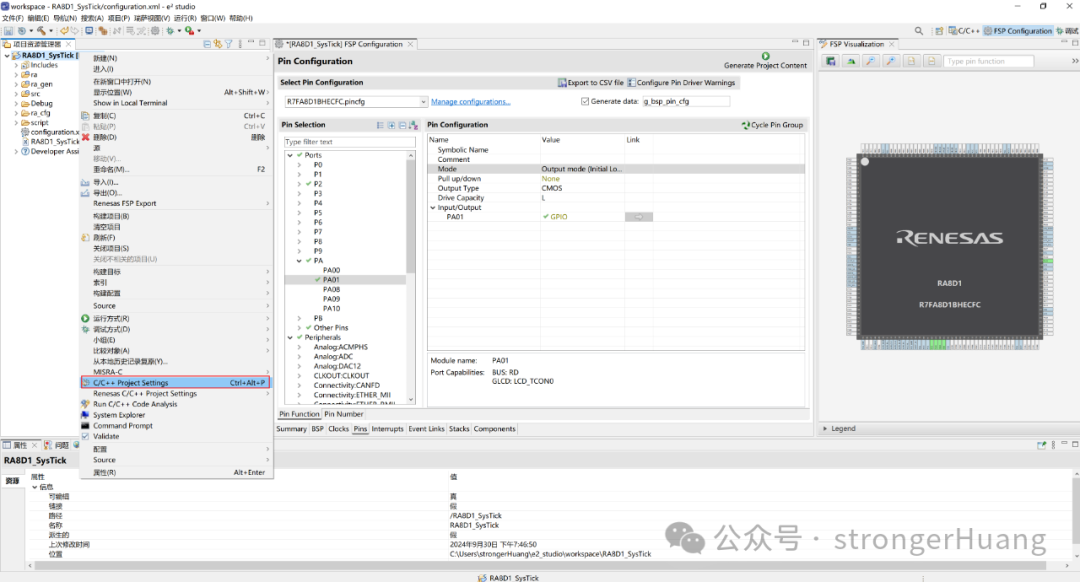

Here we configure some basic information, using an IO (PA01) to test the SysTick delay time.

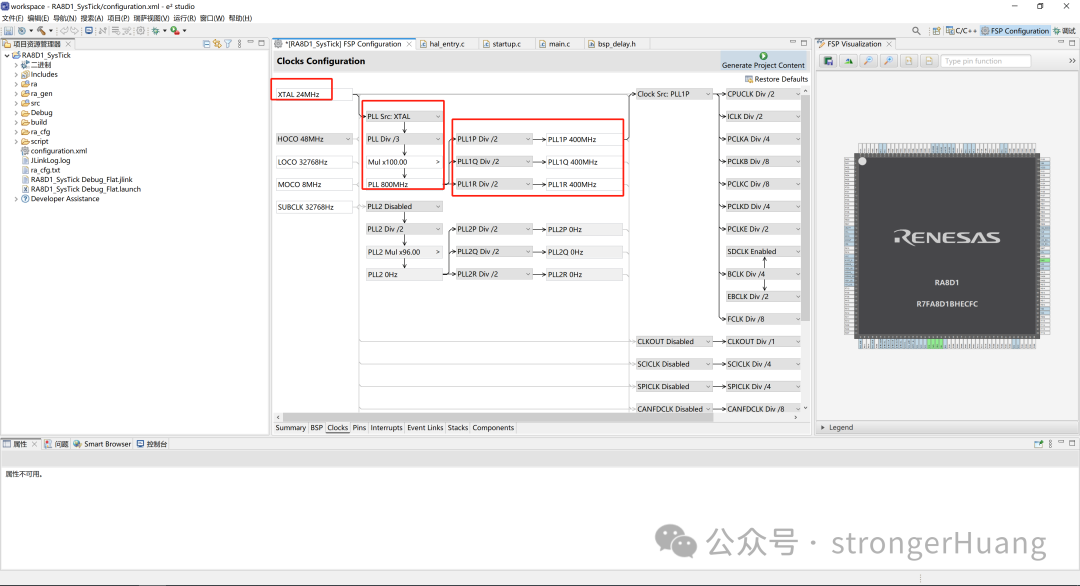

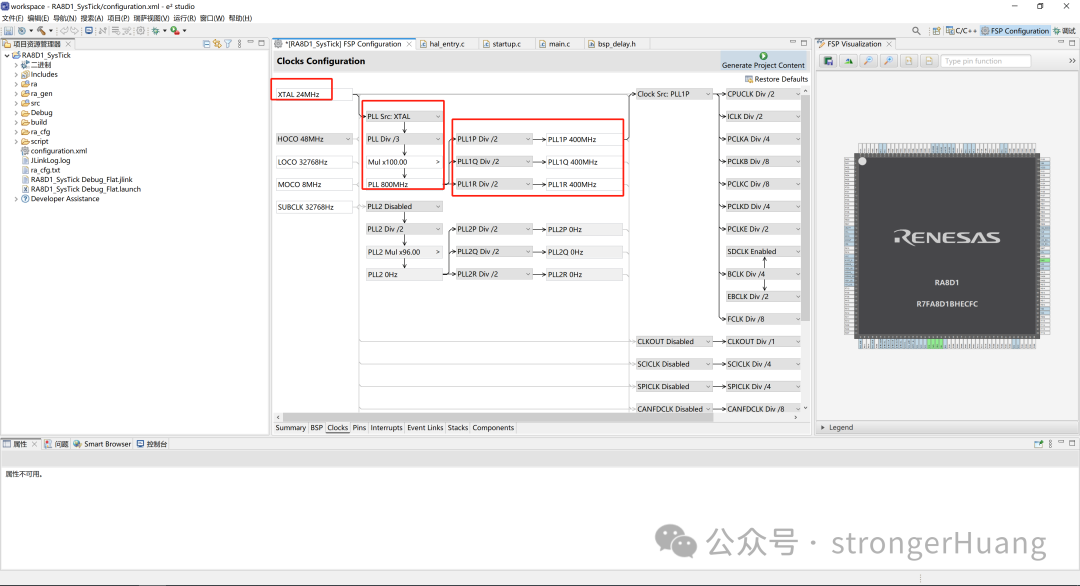

Configure the clock tree:

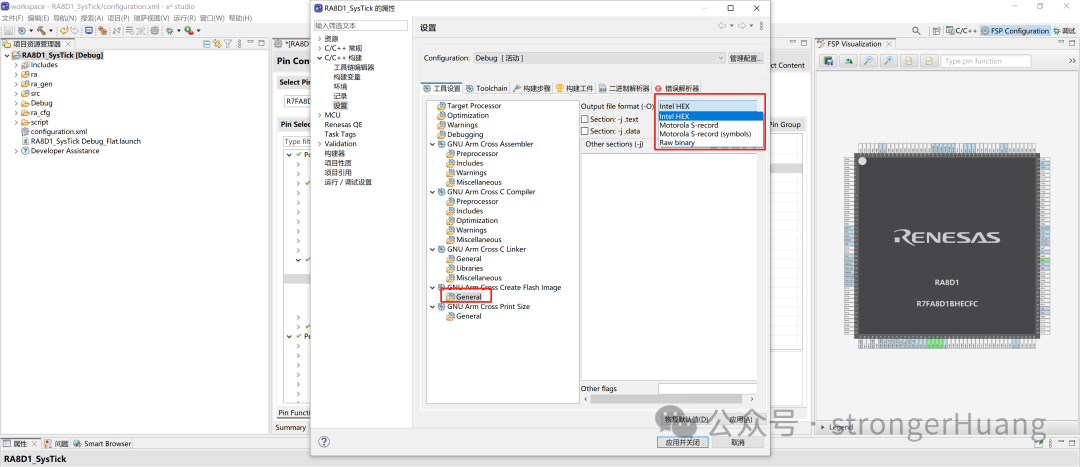

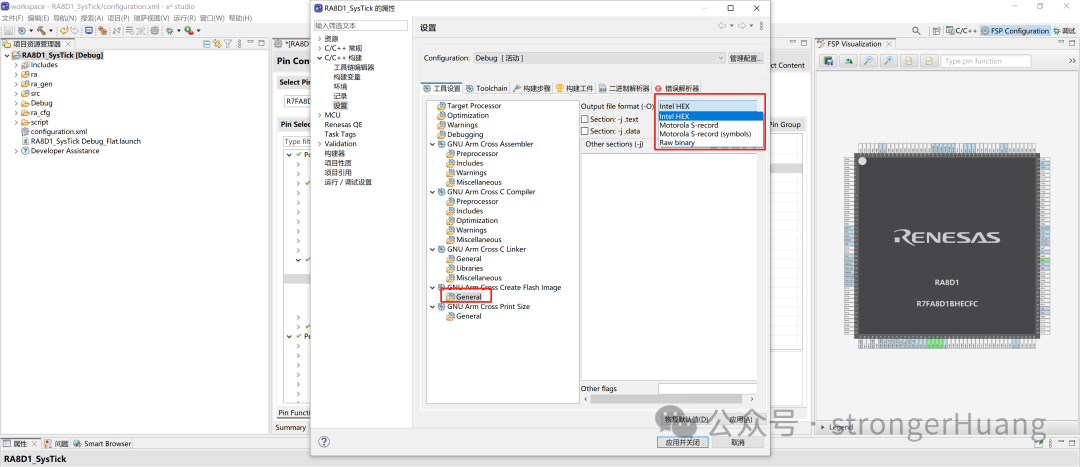

Configure the output Hex file:

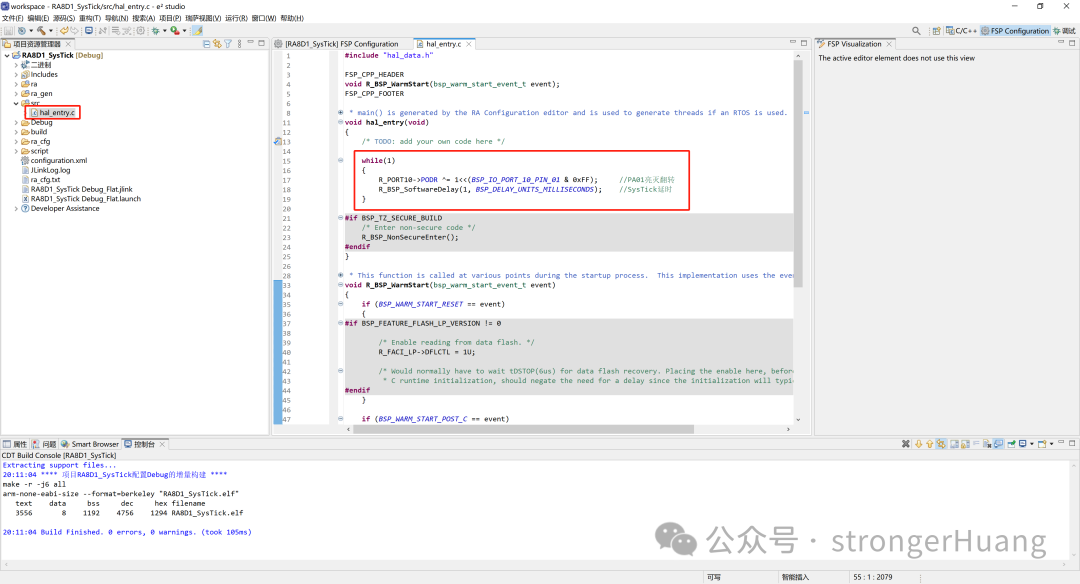

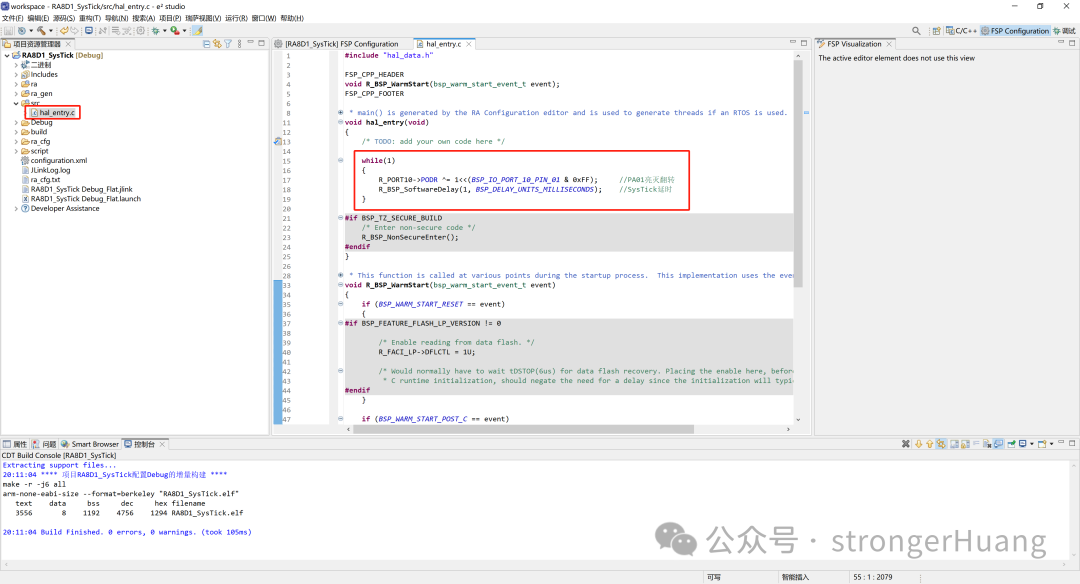

This is just a simple demonstration demo, we add an IO toggle to test the SysTick delay time.

while(1){ R_PORT10->PODR ^= 1<<(BSP_IO_PORT_10_PIN_01 & 0xFF); //PA01 toggle R_BSP_SoftwareDelay(1, BSP_DELAY_UNITS_MILLISECONDS); //SysTick delay}

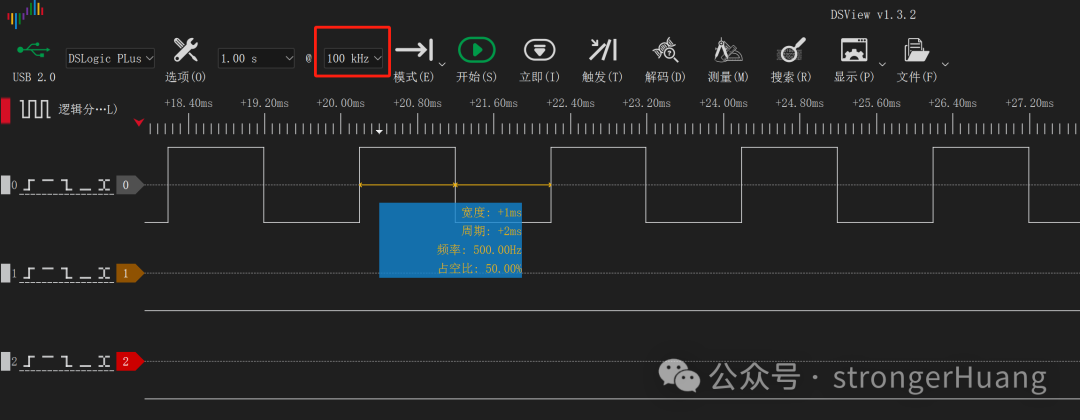

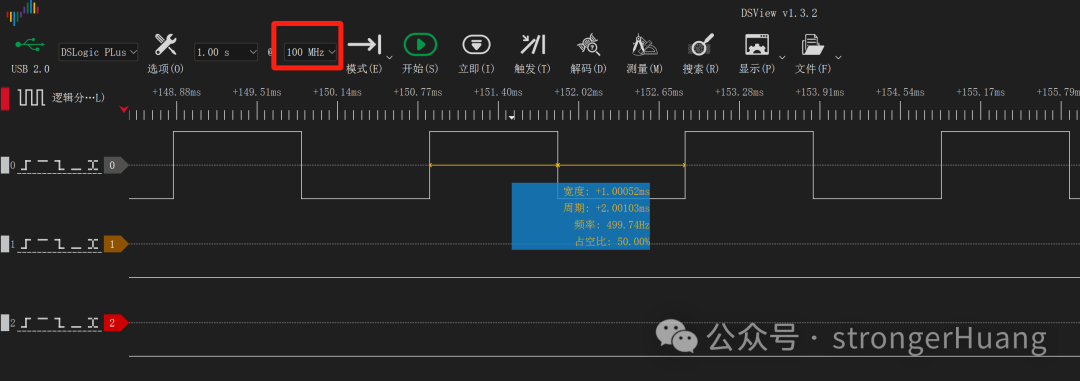

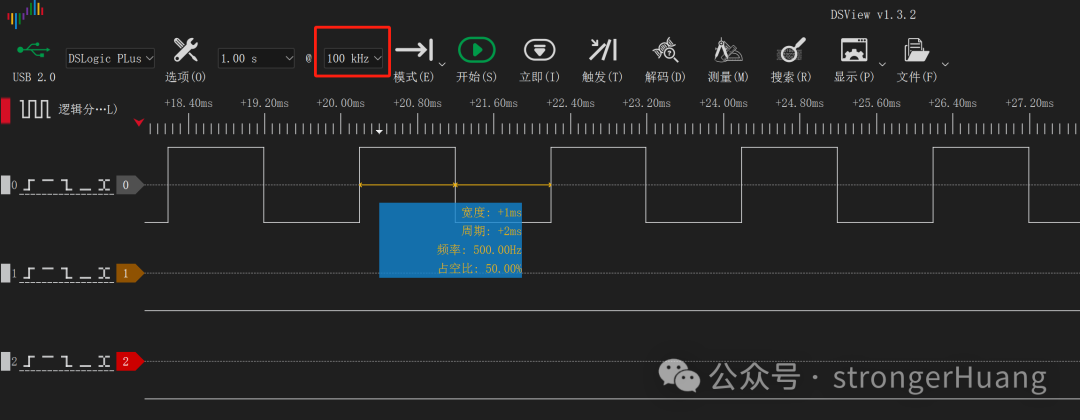

This is a 1ms toggle, and the SysTick delay error is still relatively small, which can be ignored relative to 1ms (sampling frequency 100KHz shows no error).

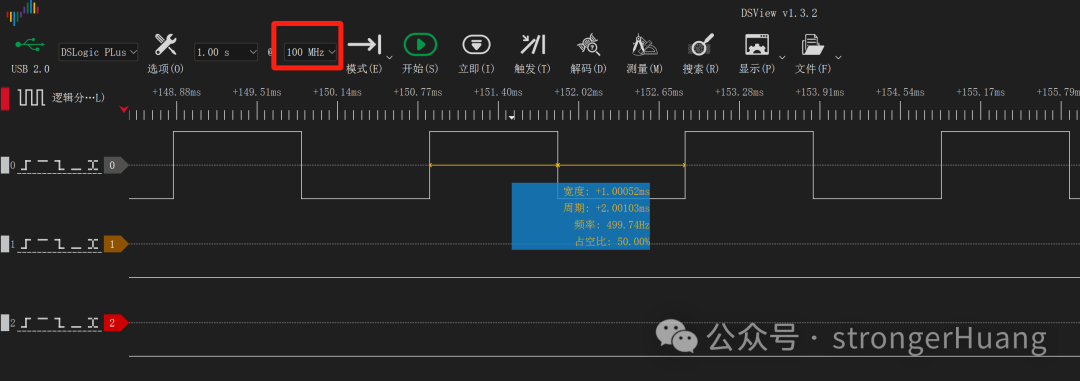

With a sampling frequency of 100MHz, some errors can still be observed. Of course, this error is influenced by various factors such as the crystal oscillator and software. Additionally, errors at the microsecond level can be ignored compared to milliseconds.

If changed to 1us toggle, the error becomes relatively obvious.

4. Source Code Description

Experienced engineers should be able to understand this. Here, I will briefly explain it for beginners.

R_PORT10->PODR ^= 1<<(BSP_IO_PORT_10_PIN_01 & 0xFF);

To reduce software-induced errors, we directly manipulate the register for IO toggling.

R_BSP_SoftwareDelay(1, BSP_DELAY_UNITS_MILLISECONDS);

R_BSP_SoftwareDelay: A blocking delay function, which is a built-in function interface of the FSP software package.

BSP_DELAY_UNITS_MILLISECONDS: Macro definition for delay units (milliseconds).

The system defines three macros:

typedef enum{ BSP_DELAY_UNITS_SECONDS = 1000000, ///< Requested delay amount is in seconds BSP_DELAY_UNITS_MILLISECONDS = 1000, ///< Requested delay amount is in milliseconds BSP_DELAY_UNITS_MICROSECONDS = 1 ///< Requested delay amount is in microseconds} bsp_delay_units_t;

R_BSP_SoftwareDelay: In fact, this is a delay using SysTick.

Further analysis of the code shows that the lower-level calls to SysTick and CM0, CM23, etc., are also the same. Therefore, you will find that there is not much difference in the usage of SysTick between Cortex-M3 and M85 microcontrollers.