Low Power Design in Digital Chips (Part 2)

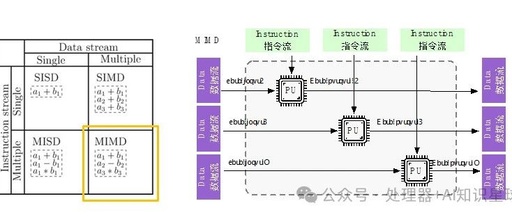

Continuing from the previous article, a typical low power design in digital chips is the addition of a clock gate. Another method is through parallel and pipelining techniques. Parallel and Pipelining The prominent advantage of hardware description languages is the parallelism in instruction execution. Multiple statements can process several signal data in parallel within the … Read more