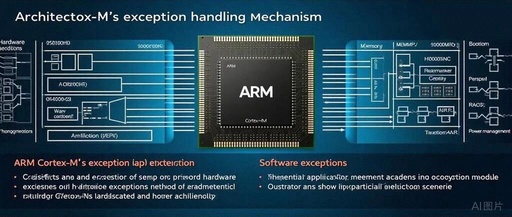

Detailed Explanation of the Cortex-M3 Embedded System Programming Model (Part 2)

This is a further refinement of the Cortex-M3 programming model, covering more specific implementation details and key operations: 1. Refinement of Register Groups 1. Detailed Explanation of Special Registers CONTROL Register (32 bits, modifiable only at privileged level) Bit 0 (`nPRIV`): 0 = Privileged mode (can access all resources) 1 = Unprivileged mode (restricted access) … Read more