Introduction

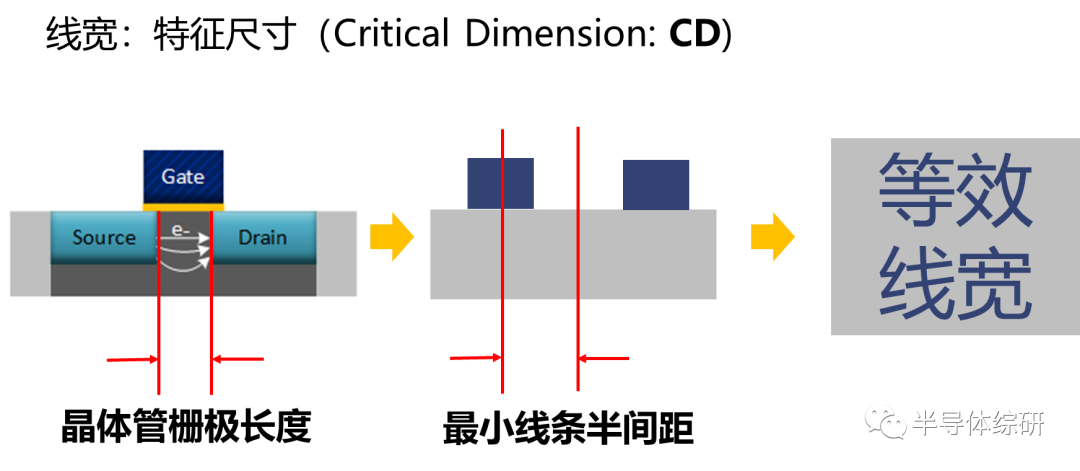

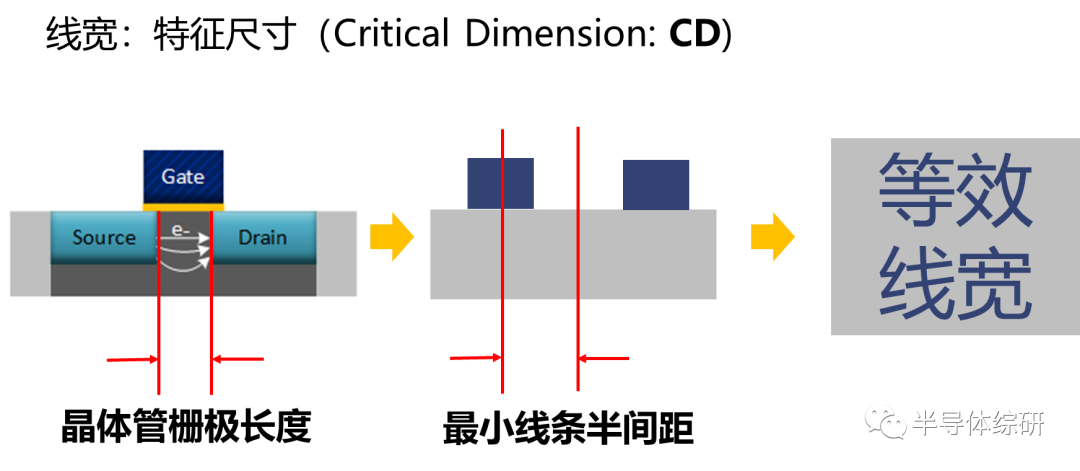

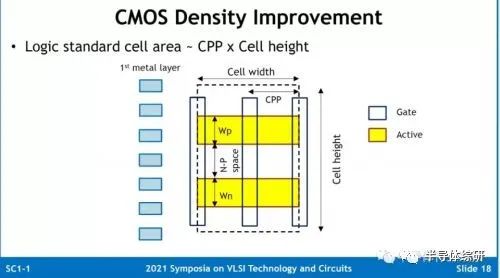

The 7nm process technology for chips is something we often hear about, but does 7nm really mean that the size of the chip is only 7nm? Let’s take a look!

Introduction

The 7nm process technology for chips is something we often hear about, but does 7nm really mean that the size of the chip is only 7nm? Let’s take a look!