When learning STM32 development, the step of DEBUG debugging is essential. This article will guide you through the knowledge related to debugging. Taking STM32F1 and Cortex-M3 as examples, the principles are similar for other series of chips or cores.01【Overview】

In STM32, there are many debugging components. Using them allows for various debugging functions, including breakpoints, data watchpoints, flash address reloading, and various tracing.

STM32F1 uses the Cortex™-M3 core, which contains a hardware debugging module, supporting complex debugging operations.

The hardware debugging module allows the core to stop during instruction fetch (instruction breakpoints) or data access (data breakpoints). When the core stops, both the internal state of the core and the external state of the system can be queried. After the query is completed, the core and peripherals can be restored, and the program will continue execution.

When the STM32F10x microcontroller is connected to a debugger and debugging begins, the debugger will use the core’s hardware debugging module for debugging operations.

02【Debugging Block Diagram】

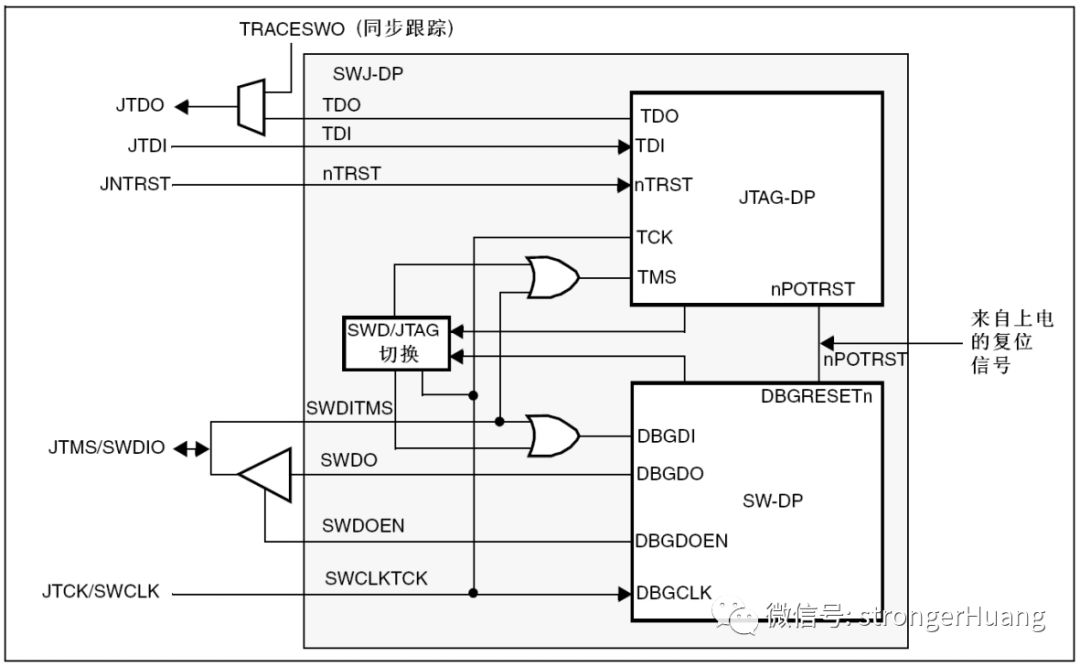

The debugging block diagram of STM32F1 and Cortex™-M3:

Note: The hardware debugging module contained in the Cortex™-M3 core is a subset of the ARM CoreSight development toolset. The ARM Cortex™-M3 core provides integrated on-chip debugging capabilities. It consists of the following parts:

- SWJ-DP: Serial/JTAG Debug Port

- AHP-AP: AHB Access Port

- ITM: Instrumentation Trace Macrocell

- FPB: Flash Patch and Breakpoint

- DWT: Data Watchpoint and Trace

- TPUI: Trace Port Interface Unit (only supported on larger package chips)

- ETM: Embedded Trace Macrocell (pins supporting this function are only available on larger packages), specifically for STM32F1 debugging features

- Flexible debugging pin assignment

- MCU Debug Box (supports low power modes, controls peripheral clocks, etc.)

03【Debugging Interfaces】

STM32 supports two debugging interfaces:

- Serial Interface

- JTAG Debug Interface

The five general I/O pins of STM32 can be used as SWJ-DP (Serial/JTAG Debug) interface pins: 04【SWJ Debug Port(serial wire and JTAG)】

04【SWJ Debug Port(serial wire and JTAG)】

The STM32 core integrates a Serial/JTAG Debug Interface (SWJ-DP). This is the standard ARM CoreSight debug interface, including the JTAG-DP interface (5 pins) and SW-DP interface (2 pins).

1. JTAG Debug Interface (JTAG-DP) provides a 5-pin standard JTAG interface for the AHP-AP module.2. Serial Debug Interface (SW-DP) provides a 2-pin (clock + data) interface for the AHP-AP module. In the SWJ-DP interface, the 2 pins of the SW-DP interface and some of the 5 pins of the JTAG interface are multiplexed.SWJ Debug Port: The above figure shows that the asynchronous trace output pin (TRACESWO) and TDO are multiplexed. Therefore, the asynchronous trace function can only be implemented on the SWDP debug interface, and cannot be implemented on the JTAG-DP debug interface.Mechanism for Switching Between JTAG-DP and SW-DPThe JTAG debug interface is the default debug interface. If the debugger wants to switch to SW-DP, it must output a specified JTAG sequence on TMS/TCK (mapped to SWDIO and SWCLK, respectively), which disables JTAG-DP and activates SW-DP. This method can activate the SW-DP interface using only the SWCLK and SWDIO two pins.The specified sequence is:1. Output TMS (SWDIO) = 1 signal for more than 50 TCK cycles2. Output 16 TMS (SWDIO) signals 0111100111100111 (MSB)3. Output TMS (SWDIO) = 1 signal for more than 50 TCK cycles05【Internal Pull-Up and Pull-Down on JTAG Pins】

The above figure shows that the asynchronous trace output pin (TRACESWO) and TDO are multiplexed. Therefore, the asynchronous trace function can only be implemented on the SWDP debug interface, and cannot be implemented on the JTAG-DP debug interface.Mechanism for Switching Between JTAG-DP and SW-DPThe JTAG debug interface is the default debug interface. If the debugger wants to switch to SW-DP, it must output a specified JTAG sequence on TMS/TCK (mapped to SWDIO and SWCLK, respectively), which disables JTAG-DP and activates SW-DP. This method can activate the SW-DP interface using only the SWCLK and SWDIO two pins.The specified sequence is:1. Output TMS (SWDIO) = 1 signal for more than 50 TCK cycles2. Output 16 TMS (SWDIO) signals 0111100111100111 (MSB)3. Output TMS (SWDIO) = 1 signal for more than 50 TCK cycles05【Internal Pull-Up and Pull-Down on JTAG Pins】

It is essential to ensure that the JTAG input pins are not floating, as they are directly connected to D flip-flops controlling the debug mode. Special attention must be paid to the SWCLK/TCK pins, as they are directly connected to the clock terminals of some D flip-flops.

To avoid any uncontrolled I/O levels, STM32 embeds internal pull-up and pull-down on the JTAG input pins.

- JINTRST: Internal Pull-Up

- JTDI: Internal Pull-Up

- JTMS/SWDIO: Internal Pull-Up

- TCK/SWCLK: Internal Pull-Down

Once the JTAG I/O is released by user code, the GPIO controller regains control. The state of these I/O pins will revert to their state at reset.

- JNTRST: Input with Pull-Up

- JTDI: Input with Pull-Up

- JTMS/SWDIO: Input with Pull-Up

- JICK/SWCLK: Input with Pull-Down

- JTDO: Floating Input

Software can use these I/O pins as regular I/O pins.06【Utilizing Serial Interface and Releasing Unused Debug Pins as General I/O Pins】

To utilize the serial debug interface to free up some general I/O pins, user software must set SWJ_CFG=010 after reset, thereby releasing PA15, PB3, and PB4 for use as general I/O pins.

During debugging, the debugger performs the following actions:

- At system reset, all SWJ pins are assigned as dedicated pins (JTAG-DP + SW-DP).

- In the system reset state, the debugger sends a specified JTAG sequence to switch from JTAG-DP to SW-DP.

- Still in the system reset state, the debugger sets breakpoints at the reset address

- Releases the reset signal, and the core stops at the reset address.

- From here, all debugging communication will use the SW-DP interface, and other JTAG pins can be repurposed by user code as general I/O pins.

Note: This is where you need to configure the relevant pins.

References:

1. Cortex™-M3 (r1p1 version) Technical Reference Manual (TRM)

2. ARM Debug Interface V5

3. ARM CoreSight Development Toolset (r1p0 version) Technical Reference Manual

Note: This article references the “STM32F1 Reference Manual” and “CM3 Technical Manual”.

Author: strongerHuang, Source: strongerHuangStatement: This article is reprinted with permission from “strongerHuang”WeChat Official Account. The reprint is for learning reference only and does not represent this account’s endorsement of its views. This account also does not bear any infringement responsibility for its content, text, or images.ENDPrevious Recommendations1.I realized that my understanding of ripple was wrong! What exactly is ripple, and what is noise?2.Can the series resistor on the G gate of the MOSFET suppress resonance? What is the principle?

3.Why should two 10uF and two 100nF capacitors be connected in parallel on the power supply? Can’t a single 22uF capacitor work?