Produced by | Automotive Electronics and Software

Currently, among the various controllers responsible for core vehicle control functions, a significant portion of the processors used are based on the ARM architecture. This architecture occupies a crucial position in the automotive electronics field due to its excellent energy efficiency, extensive ecosystem support, and high flexibility. Therefore, this article aims to briefly introduce the characteristics of ARM architecture processors for discussion and exchange.

ARM is a company based in the UK that designed the first low-power cost RISC microprocessor, known as the ARM processor (Advanced RISC Machines). After the classic ARM11 processor, ARM’s products began to adopt the Cortex naming convention, divided into A, R, and M categories, aimed at serving various markets. The Cortex series belongs to the ARMv7 architecture, which was the latest instruction set architecture from ARM at that time. Therefore, it can be said that Cortex is the name of a series of processors launched by ARM, with origins tracing back to ARM’s processor design and development history.

First, let me explain a concept: what is the instruction set of a chip processor? The instruction set mainly refers to the interface description between CPU hardware and software, essentially a segment of binary machine code. The CPU can only recognize and execute these machine code instructions, while the machine code itself is a meaningless string that is difficult for programmers to understand and use. Therefore, people invented assembly language and other high-level programming languages, which have a one-to-one correspondence with machine code, making it easier for programmers to write and debug programs.

Instruction sets can be divided into several types, among which the most famous are Complex Instruction Set (CISC) and Reduced Instruction Set (RISC).

-

Complex Instruction Set (CISC):This type of instruction set contains a large number of instructions, and each instruction has a relatively complex function. The X86 instruction set is a typical example of a CISC instruction set.

-

Reduced Instruction Set (RISC):In contrast to CISC, the RISC instruction set contains fewer instructions, and each instruction has a relatively simple function. The ARM instruction set is a representative of the RISC instruction set, widely used in mobile devices, embedded systems, and other fields.

We often hear terms like “ARM architecture chips,” which actually refer to the specific instruction set used by a processor. Currently, the mainstream chip architectures on the market include X86, ARM, RISC-V, and MIPS.

In most cases, architecture is equivalent to instruction set. For example, if a processor is based on the ARMv7 architecture, it uses the ARMv7 instruction set. The instruction set architecture is part of computer architecture, specifying the set of instructions that the processor can recognize and execute. The ARM architecture also includes versions v8 and v9, with v7 being an earlier version and one of the currently widely used ARM architecture versions, which is divided into series A (Application Processors for high-performance products), R (Real-time Processors for real-time systems), and M (Microcontroller Processors for microcontrollers); ARMv9 is the latest version of the ARM architecture, and the comparison of instruction sets among these three versions is roughly as follows:

-

It introduced a new instruction set called Thumb-2, which is a mix of 32-bit and 16-bit instructions, capable of providing high performance while saving storage space.

-

ARMv7 also supports hardware floating-point operations (VFPv3), improving the processor’s ability to handle floating-point numbers.

-

This is the first 64-bit architecture version introduced by ARM.

-

It supports both 64-bit and 32-bit applications, providing a larger address space, more registers, and enhanced security features.

-

ARMv8 introduced a new instruction set AArch64 for executing 64-bit operations.

-

This architecture also improved support for floating-point and SIMD (Single Instruction, Multiple Data), including new floating-point operation instructions and new SIMD instructions optimized for multimedia and data processing.

-

ARMv8 also introduced hardware virtualization support, improving the performance of applications running in virtual environments.

-

ARMv9 made a series of optimizations and improvements over previous versions to enhance processor performance and efficiency.

-

It introduced a new technology called SVE2 (Scalable Vector Extension 2), which is a vector operation technology that can significantly enhance the processor’s ability to handle machine learning and artificial intelligence tasks.

-

ARMv9 also strengthened security features, introducing a new Realm management architecture to more effectively prevent various network attacks and data breaches.

-

This architecture improved support for virtualization, making virtualization in cloud computing and other high-performance computing applications more efficient.

In simple terms, the instruction set is the bridge between the CPU and software, allowing software to correctly control the CPU to perform various operations. At the same time, the instruction set also determines key indicators such as CPU performance and power consumption. Different instruction sets have different characteristics and advantages, suitable for various application scenarios.

Applications of Cortex Kernel in Automotive Chips

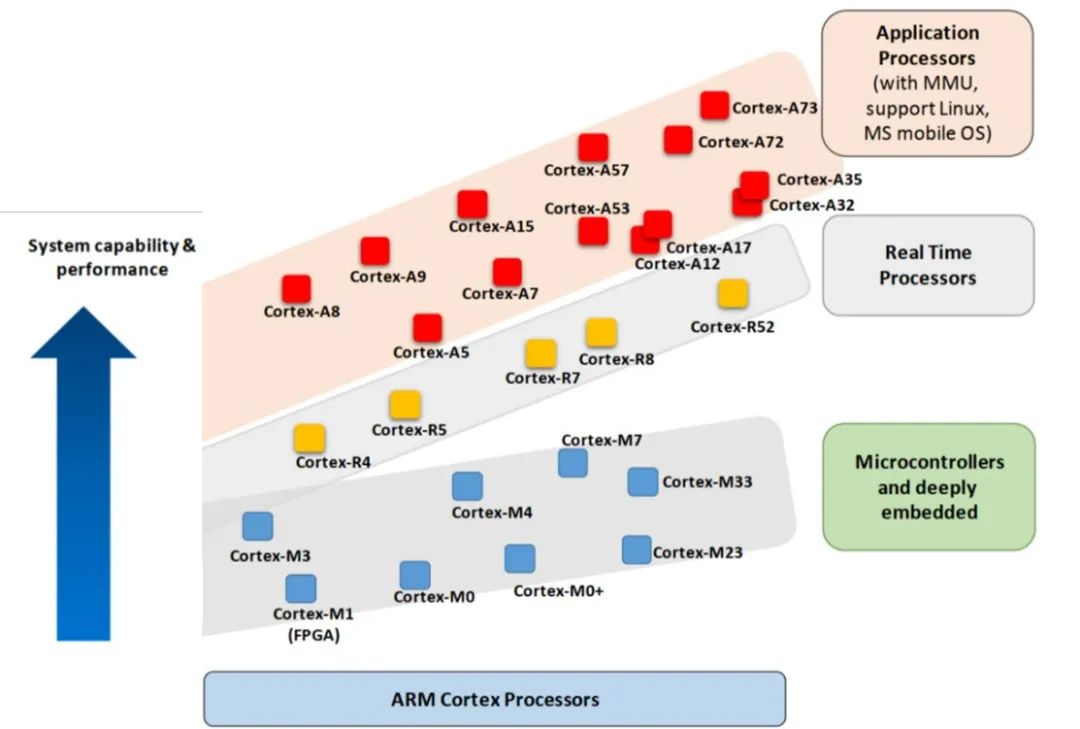

The commonly used ARM Cortex series chips in vehicle controllers are mainly based on ARMv7 and v8 architectures.

ARM Cortex series chips are divided into A, R, and M series, which is also the source of the chip A core and M core terms we often hear.

Cortex-A is a high-end processor aimed at markets such as mobile computing, smartphones, and servers, with a high operating frequency (>1GHz) and supports the memory management units required by operating systems like Linux, Android, and Windows. In the automotive field, it can be used for cockpit chips, intelligent driving chips, central computing platform chips, etc.

Cortex-R is used for real-time applications, such as body controllers, automotive chassis systems, and power system control, without supporting memory management units but possessing other storage functionalities, with high operating frequencies (200MHz to >1GHz), low response latency, and supporting real-time operating systems instead of full Linux and Windows.

Cortex-M is compact and energy-efficient, with lower clock frequencies but some exceeding 200MHz. The new Cortex-M series is easy to use and is widely popular in microcontrollers and deeply embedded systems, and can also be used for body control, although its performance is slightly inferior to that of Cortex-R.

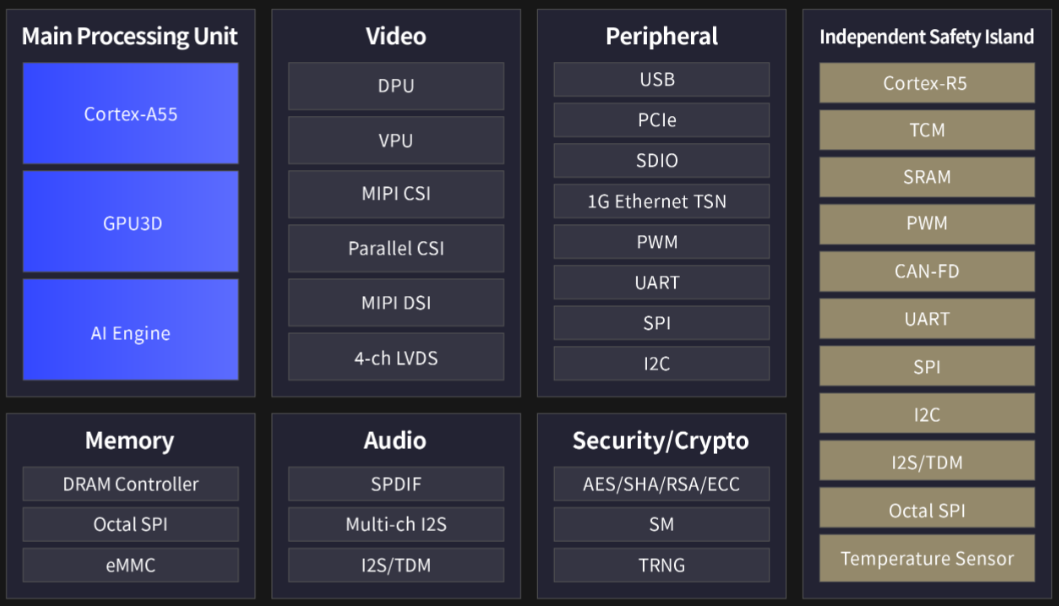

Chip architecture of Xinchih X9 series

The gateway chips G9 series, intelligent driving chips V9 series, and cockpit chips X9 series from domestic chip manufacturer Xinchih mainly use Cortex-A55+Cortex-R5 as their main processors, forming a multi-core heterogeneous chip.

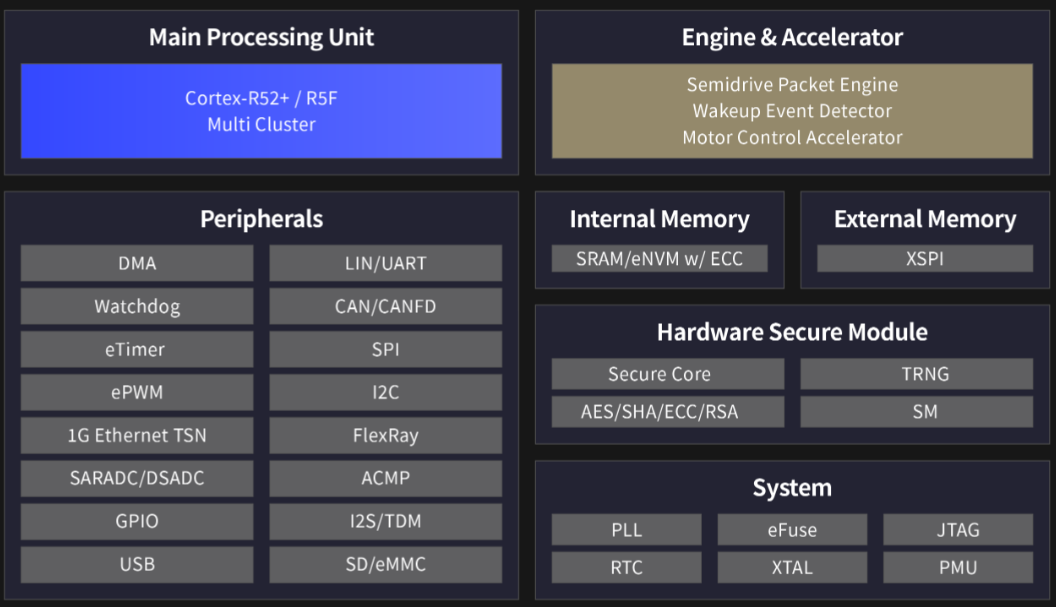

Chip architecture of Xinchih E3 series

However, the E3 series chips launched by Xinchih, primarily used for vehicle control and domain control, do not adopt Cortex-A but rather Cortex-R5 and Cortex-R52+. This is because the E3 MCU is a new generation of high-performance microcontroller products designed for automotive safety-related applications, and based on this requirement, it opted for the real-time, high-security Cortex-R series processors instead of Cortex-A.

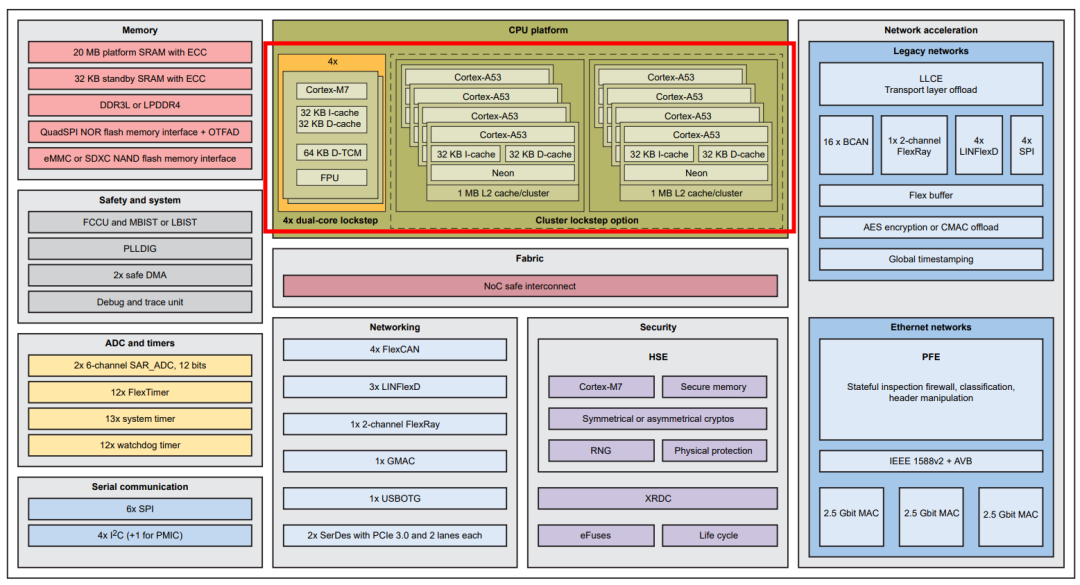

NXP S32G399A architecture diagram

For example, NXP’s domain control and gateway product series S32G series choose processor cores in the form of Cortex-M7+Cortex-A53, with the most advanced product in the S32G series, the S32G399A, having 4 Cortex-M7 and 8 Cortex-A53 cores. This heterogeneous form allows the entire SoC to have high computing power while meeting ASIL D safety standards on the Cortex-M.

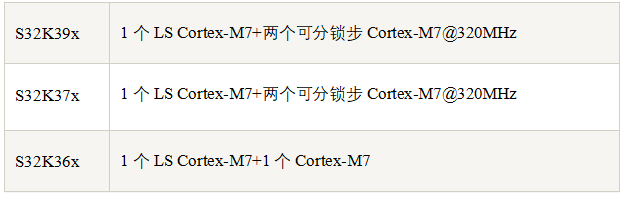

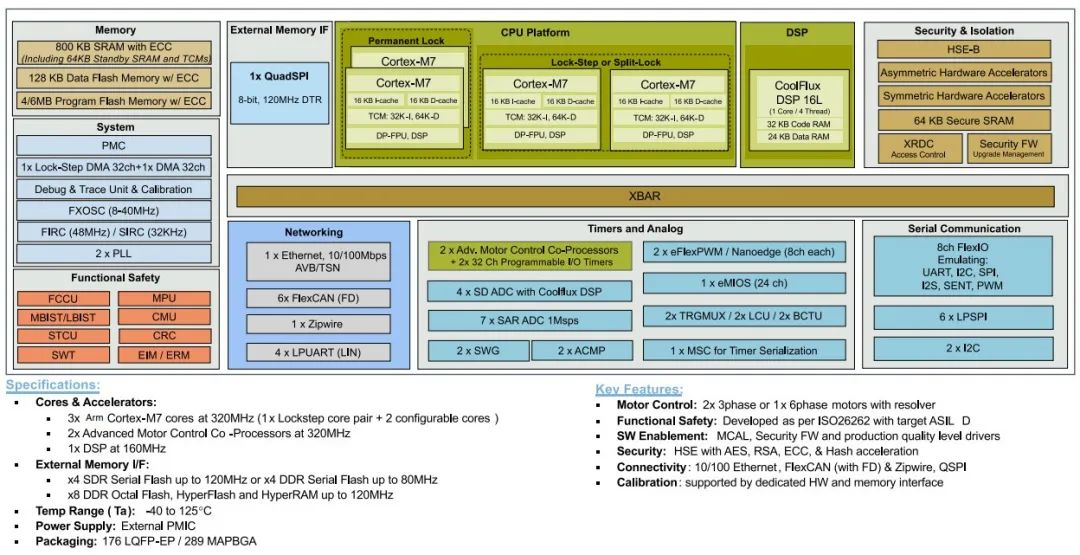

Composition of S32K3 series processors

Additionally, NXP’s S32K3 series chips have applications in power management, inverter control, body area control, and many other aspects, featuring multiple Cortex-M7 cores, some of which also have two lock-step Cortex-M7 cores. Dual Core Lock Step (DCLS) is a CPU redundancy technology that includes two identical processors within a chip. These two processors run in a master-slave relationship, executing the same code and synchronizing strictly. The key point is that DCLS can rapidly monitor and isolate processor operation errors through hardware redundancy and comparison mechanisms, preventing fault propagation.

S32K39x (x=4 or 6) chip block diagram

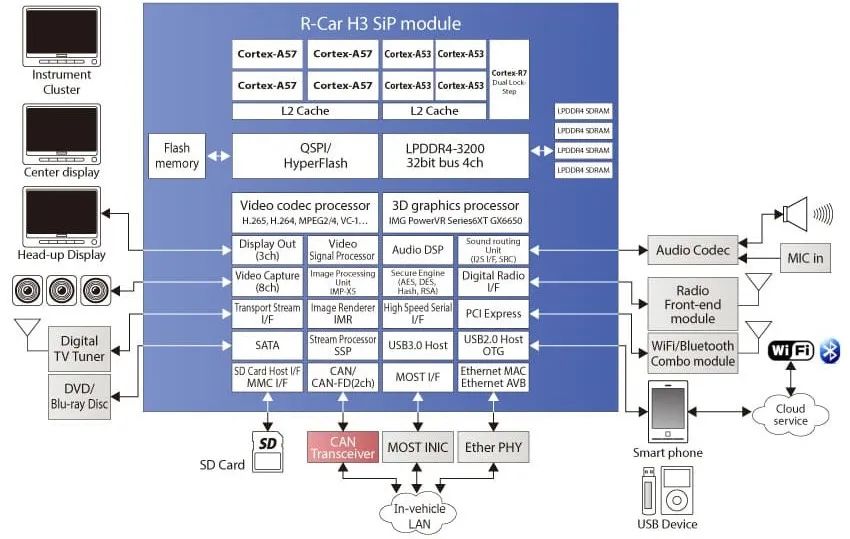

Renesas’s MCU/MPU/SoC products also widely use ARM architecture cores.

Renesas’s R-Car H3e architecture

Renesas’s R-Car H3e (-2G) is a high-end computing automotive SoC, with core processors including four Cortex-A57, four Cortex-A53, and dual-core lock-step Cortex-R7, boasting powerful computing performance capable of accurately processing large amounts of information from automotive sensors in real-time. Its applications are very diverse, such as in-car entertainment information systems and integrated cockpits. It meets the ISO 26262 (ASIL-B) automotive functional safety standards and information security requirements. The 2GHz operating speed of the (H3e-2G) improves computing capability while maintaining hardware and software compatibility.

In summary, the ARM architecture plays an important role in automotive electronics due to its low power consumption, high performance, and customizability. With continuous technological development and innovation, there is still tremendous potential for ARM architecture. By selecting suitable cores, optimizing code, using hardware acceleration, and optimizing memory access, system performance and power efficiency can be further improved to meet the needs of various application scenarios.

Welcome to scan the QR code below to join the Intelligent Transportation Technology group!

Scan to join the free “Smart City’s Smart Transportation” knowledge community to learn more industry news and materials.

Contact: WeChat ID 18515441838