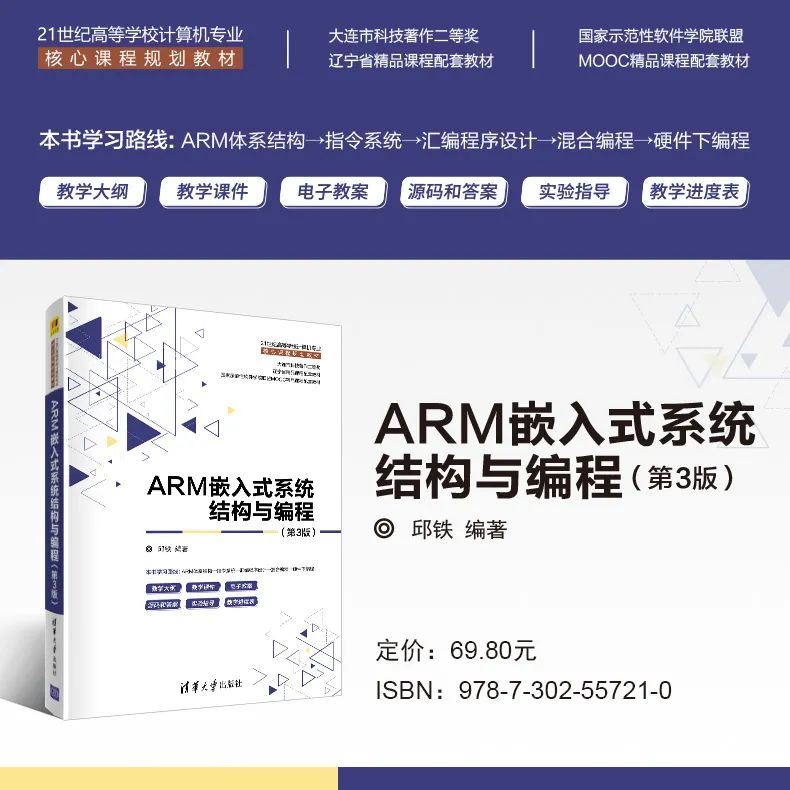

“ARM Embedded System Architecture and Programming”

Course Teaching Outline

|

Credits |

3 |

|

Class Hours |

32+24 |

01

Course Description

Through this course, students will master the ARM architecture, ARM instruction set, and embedded programming under the ARM architecture. Students will gain proficiency in hardware development platforms based on ARM technology, performing hardware programming and hardware interface experiments, laying a solid foundation for embedded system software and hardware design and development.

02.

Course Objectives

1. Understand the latest embedded products, grasp the definition and connotation of embedded systems. This definition includes IEEE and the embedded systems industry definition, and understand the development trends of embedded systems.

03

Teaching Content, Basic Requirements, and Class Hours Allocation

04

Other Teaching Activities

Experimental Teaching Content Total: 24-32 Class Hours

05

Teaching Instructions

1. Semester: Spring/Fall.

2. Teaching Unit: School of Computing/School of Software/School of Telecommunications.

3. Applicable Majors: Computer Science, Electronic Engineering, Communication, Internet of Things, Software Engineering.

4. Prerequisite Courses: Computer Organization Principles, Interfaces and Assembly, Digital Circuits and Analog Circuits, Programming Languages.

06

Textbooks and References

Catalog

Scroll down to view ↓

Chapter 1 Introduction

1.1 Definition of Embedded Systems

1.1.1 Development History of Embedded Systems

1.1.2 Definition and Characteristics of Embedded Systems

1.2 Embedded Operating Systems

1.2.1 Embedded Real-Time Operating Systems

1.2.2 Typical Applications of Real-Time Operating Systems

1.3 Applications of Embedded Technology in Engineering

1.4 Development Trends of Embedded Technology

Thoughts and Exercises

Chapter 2 ARM Technology and ARM Architecture

2.1 ARM Architecture Versions and Kernels

2.1.1 ARM Architecture Versions

2.1.2 ARM Kernel Version Naming Rules

2.1.3 Mainstream ARM Processor Kernel Series and Applications

2.2 ARM Kernel Modules

2.3 Working Modes of ARM Processors

2.4 Internal Registers

2.4.1 General Registers and Their Distribution

2.4.2 Program Status Register

2.5 ARM Exception Handling

2.6 Storage Methods and Memory Mapping Mechanisms

2.7 ARM Pipeline Technology Analysis

Thoughts and Exercises

Chapter 3 ARM Instruction Set Addressing Modes

3.1 ARM Instruction Encoding Format

3.2 Data Processing Instruction Addressing Modes

3.3 Load/Store Instruction Addressing

3.3.1 Address Calculation Methods

3.3.2 Word, Unsigned Byte Addressing

3.3.3 Half-Word, Signed Byte Addressing

3.4 Bulk Load/Store Instruction Addressing Modes

3.5 Coprocessor Instruction Addressing Modes

Thoughts and Exercises

Chapter 4 ARM Instruction Set System

4.1 Data Processing Instructions

4.1.1 Basic Data Processing Instructions

4.1.2 Multiplication Instructions

4.1.3 Miscellaneous Data Processing Instructions

4.2 ARM Branch Instructions

4.3 Load/Store Instructions

4.3.1 Load/Store Word, Unsigned Byte Instructions

4.3.2 Half-Word, Signed Byte Access Instructions

4.4 Bulk Load/Store Instructions

4.4.1 Basic Bulk Word Data Load/Store Instructions

4.4.2 Bulk Word Data Load/Store Instructions in User Mode

4.4.3 Bulk Word Data Load Instructions with PSR Operations

4.5 Swap Instructions

4.6 Program Status Register Access Instructions

4.7 Coprocessor Operation Instructions

4.7.1 Coprocessor Data Operation Instructions

4.7.2 Coprocessor Load/Store Instructions

4.7.3 Data Transfer Instructions between ARM Registers and Coprocessor Registers

4.8 Exception Generation Instructions

Thoughts and Exercises

Chapter 5 Thumb Instructions

5.1 Thumb Data Processing Instructions

5.1.1 Register Shift Instructions

5.1.2 Low Register Arithmetic Operation Instructions

5.1.3 ALU Operation Instructions

5.1.4 Thumb Instructions with High Register Operations

5.1.5 Arithmetic Operation Instructions with SP/PC

5.2 Thumb Memory Operation Instructions

5.2.1 Load/Store Instructions for Bytes, Half-Words, and Words

5.2.2 Bulk Load/Store Instructions

5.3 Thumb Branch Instructions

5.3.1 B Branch Instructions

5.3.2 Link Branch Instructions

5.3.3 Branch Instructions with State Switching

5.4 Thumb Software Interrupt Instructions

5.5 Analysis of Thumb Instruction Function Code Segments

5.5.1 Comparison of Functionality between Thumb and ARM Implementations

5.5.2 Performance Comparison between Thumb and ARM

Thoughts and Exercises

Chapter 6 ARM Assembly Pseudo-Instructions and Pseudo-Operations

6.1 Assembly Language Pseudo-Instructions

6.1.1 ARM Assembly Language Pseudo-Instructions

6.1.2 Thumb Assembly Language Pseudo-Instructions

6.2 ARM Assembly Language Pseudo-Operations

6.3 ARM Assembly Pseudo-Operations

6.3.1 Symbol Definition Pseudo-Operations

6.3.2 Data Definition Pseudo-Operations

6.3.3 Assembly Code Control Pseudo-Operations

6.3.4 Assembly Information Reporting Control Pseudo-Operations

6.3.5 Instruction Set Type Identification Pseudo-Operations

6.3.6 File Inclusion Pseudo-Operations

6.3.7 Other Types of Pseudo-Operations

6.4 GNU ARM Assembly Pseudo-Operations

6.4.1 Symbol Definition Pseudo-Operations

6.4.2 Data Definition Pseudo-Operations

6.4.3 Assembly and Disassembly Code Control Pseudo-Operations

6.4.4 Predefined Control Pseudo-Operations

Thoughts and Exercises

Chapter 7 Assembly Language Program Design

7.1 Assembly Statements in ARM Compilation Environment

7.1.1 Assembly Statement Format in ARM Compilation Environment

7.1.2 Symbol Rules in Assembly Statements of ARM Compilation Environment

7.2 Assembly Statements and Compilation Instructions in GNU Environment

7.2.1 Assembly Statement Format in GNU Environment

7.2.2 Compilation of ARM Assembly Programs in GNU Environment

7.3 ARM Assembly Language Program Design Specifications

7.4 ARM Assembly Language Program Design Example Analysis

Thoughts and Exercises

Chapter 8 ARM Assembly Language and Embedded C Mixed Programming

8.1 Embedded C Programming Specifications

8.2 Bit Operations in Embedded C Programming

8.3 Notes on Embedded C Programming

8.3.1 Volatile Qualifier

8.3.2 Address Casting and Multi-level Pointers

8.3.3 Use of Preprocessing

8.4 Embedded C Programming Format

8.5 Procedure Calling Standards ATPCS and AAPCS

8.5.1 Register Usage Rules

8.5.2 Data Stack Usage Rules

8.5.3 Parameter Passing Rules

8.6 Inter-calling between ARM Assembly Language and Embedded C Mixed Programming

8.6.1 Inline Assembly

8.6.2 Inter-calling between ARM Assembly Language and Embedded C Programs

Thoughts and Exercises

Chapter 9 S3C44B0/S3C2410/S3C2440 Hardware Structure and Key Technology Analysis

9.1 Introduction to Processors

9.2 S3C44B0/S3C2410/S3C2440 Memory Controller

9.2.1 S3C44B0 Memory Control and Address Space

9.2.2 S3C2410/S3C2440 Memory Control and Address Space

9.2.3 S3C44B0/S3C2410/S3C2440 Memory Width Control

9.2.4 S3C44B0/S3C2410/S3C2440 Memory Interface Timing Analysis

9.2.5 S3C44B0/S3C2410 Memory Control Registers

9.2.6 SDRAM Interface Circuit Design

9.2.7 S3C44B0 Memory Initialization Example

9.3 S3C2410/S3C2440 NAND Flash Controller

9.4 S3C44B0/S3C2410/S3C2440 Clock and Power Management

9.4.1 S3C44B0/S3C2410/S3C2440 Clock Management

9.4.2 S3C44B0/S3C2410/S3C2440 Power Management

9.4.3 S3C44B0/S3C2410/S3C2440 Clock and Power Management Special Registers

9.5 S3C44B0/S3C2410/S3C2440 General I/O Ports

9.5.1 Port Control Description

9.5.2 Port Registers

9.5.3 General I/O Interface Design Example

9.6 S3C44B0/S3C2410/S3C2440 Interrupt Mechanism

9.6.1 S3C44B0 Interrupt Controller

9.6.2 S3C2410/S3C2440 Interrupt Controller

9.6.3 S3C44B0/S3C2410/S3C2440 Interrupt Control Special Function Registers

9.6.4 S3C44B0/S3C2410/S3C2440 Interrupt Controller Design Example

Thoughts and Exercises

Chapter 10 S3C44B0/S3C2410/S3C2440 Communication and LCD Interface Technology

10.1 S3C44B0/S3C2410/S3C2440 UART

10.1.1 UART Principles

10.1.2 S3C44B0/S3C2410/S3C2440 UART Module

10.1.3 S3C44B0/S3C2410/S3C2440 UART Operations

10.1.4 UART Interrupt and Baud Rate Calculation

10.1.5 S3C44B0/S3C2410 UART Special Function Registers

10.1.6 S3C44B0/S3C2410 UART Design Example

10.2 S3C44B0/S3C2410/S3C2440 I2C Bus Interface

10.2.1 I2C Bus Principles

10.2.2 S3C44B0/S3C2410/S3C2440 I2C Bus Functional Module

10.2.3 S3C44B0/S3C2410/S3C2440 I2C Bus Operations

10.2.4 S3C44B0/S3C2410/S3C2440 I2C Special Function Registers

10.2.5 S3C44B0/S3C2410/S3C2440 I2C Bus Design Example

10.3 S3C44B0/S3C2410/S3C2440 LCD Controller

10.3.1 LCD Introduction

10.3.2 S3C44B0/S3C2410/S3C2440 LCD Controller Module

10.3.3 S3C44B0/S3C2410/S3C2440 LCD Controller Special Function Registers

10.3.4 S3C44B0/S3C2410/S3C2440 LCD Controller Design Example

Thoughts and Exercises

Appendix A S3C44B0/S3C2410/S3C2440 Packaging and I/O Multiplexing Information

Appendix B Link Positioning and System Boot Program

Appendix C “ARM Embedded System Architecture and Programming” Course Examination Standard Test Questions