Arm Selected Courses – Focus on ARM and TEE

1. Cortex-X925

The Cortex-X925 core is a high-performance, low-power product based on the Armv9.2-A architecture. The Armv9.2-A architecture extends the Armv8-A architecture, encompassing Armv8.7-A.

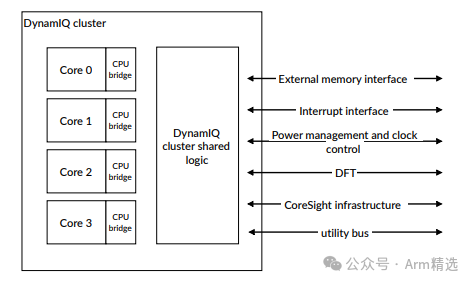

The Cortex-X925 core is integrated within the DSU-120 DynamIQ™ cluster. It connects to the DynamIQ™ Shared Unit-120, which serves as a complete interconnect system, including L3 cache and snoop control. This connection configuration is also applicable to systems containing different types of cores, where the Cortex-X925 core acts as the high-performance core.

The following diagram shows an example of configuring four Cortex-X925 cores within a DynamIQ™ cluster.

1.1 Features of the Cortex-X925 Core

The Cortex-X925 core can be used in a standalone DynamIQ™ configuration, where the DSU-120 DynamIQ™ cluster contains one or more Cortex-X925 cores. Regardless of the cluster configuration, the Cortex-X925 core always possesses the same features listed below.

Features

-

Implements the Armv9.2-A A64 instruction set

-

All exception levels (EL0 to EL3) support AArch64 execution state

-

Memory Management Unit (MMU)

-

40-bit physical address (PA) and 48-bit virtual address (VA)

-

Generic Interrupt Controller (GIC) CPU interface for connecting external interrupt distributors

-

Generic timer interface supporting 64-bit count input from external system counters

-

Implements Reliability, Availability, and Serviceability (RAS) extensions

-

Implements Scalable Vector Extension (SVE) with 128-bit vector length and Scalable Vector Extension 2 (SVE2)

-

Integrated execution units supporting advanced Single Instruction Multiple Data (SIMD) and floating-point operations

-

Activity Monitoring Unit (AMU)

-

Supports optional cryptographic extensions

Cache Features

-

Separate L1 data cache and instruction cache

-

Private, unified L2 data and instruction cache

-

Error protection for L1 instruction and data caches, L2 cache, and MMU translation cache (MMU TC), supporting parity or Error Correction Code (ECC) for Single Error Correction and Double Error Detection (SECDED)

-

Supports Memory Partitioning and Monitoring (MPAM)

Debug Features

-

Armv9.2-A debug logic

-

Performance Monitoring Unit (PMU)

-

Embedded Trace Extensions (ETE)

-

Trace Buffer Extensions (TRBE)

-

Statistical Profiling Extensions (SPE)

-

Optional Embedded Logic Analyzer (ELA), ELA-600

2 Cortex-X925 Core Configuration Options

You can choose options suitable for implementation requirements at build time. The implementation options for the Cortex-X925 core include:

Cryptographic Extensions

You can choose to include or exclude cryptographic extensions in the implementation. The selected option applies to all cores in the cluster.

L2 Data RAM ECC Unit

You can configure the L2 data RAM ECC unit as 128 bits or 256 bits.

L2 Cache Size

You can configure the L2 cache as 2048KB or 3072KB. Cores in the cluster can have different cache sizes.

PMU Event Counters

You can configure the number of PMU event counters to be 6 or 31.

CoreSight ELA

You can choose to integrate ELA-600 as a separately licensed product. This option can be configured on a per-core basis.

Size of ATB FIFO Depth in Core ELA

You can configure the size of the AMBA Trace Bus (ATB) FIFO to be 4, 8, 16, 32, or 64. This option can be configured on a per-core basis.

Arm Selected Courses – Focus on ARM and TEE

Timing Closure

You can configure the timing behavior of the L2 data cache RAM. For more information, refer to the Cortex-X925 Core Configuration and Integration Manual for Cortex-X925 configuration parameters.

NoteThe Cortex-X925 cores in the DSU-120 cluster must have the same configuration, except for L2 cache size.

For detailed configuration options and guidelines, refer to the RTL configuration process in the Arm Cortex-X925 Core Configuration and Integration Manual.

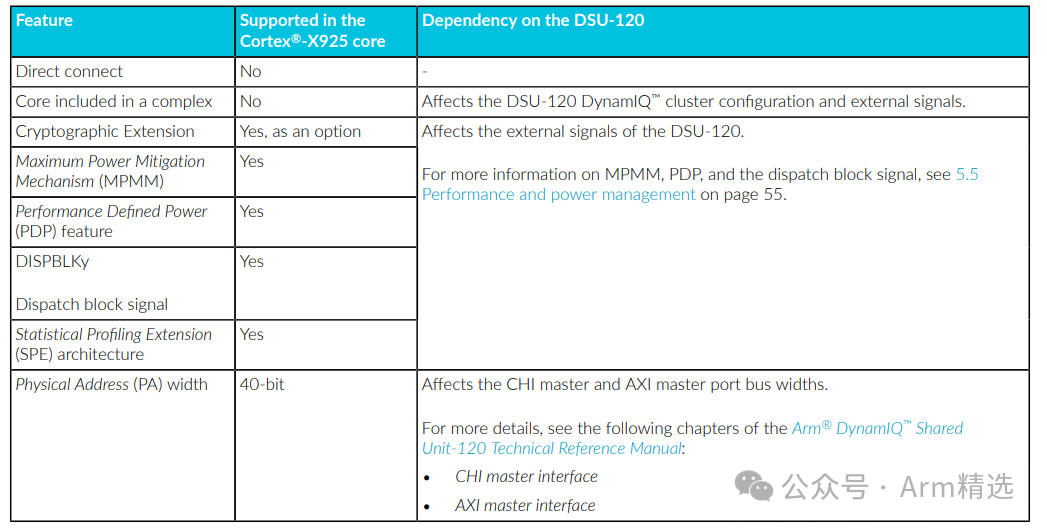

3 DSU-120 Dependent Features

Some features and behaviors of the DynamIQ™ Shared Unit-120 depend on whether your licensed core supports specific features.

The following table describes which DSU-120 dependent features your Cortex-X925 core supports.

NoteThe cryptographic extensions are provided under a separate license.

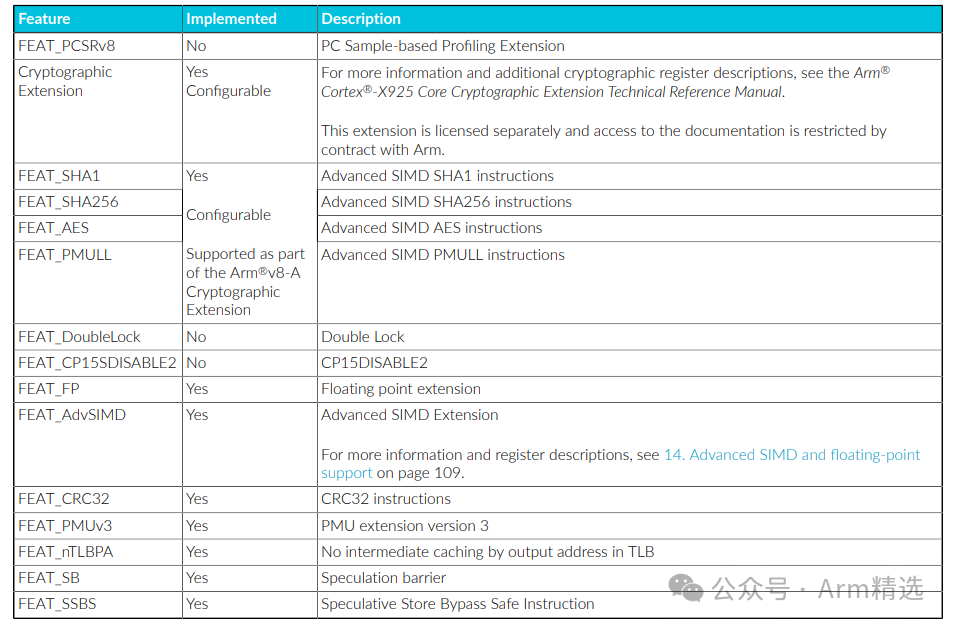

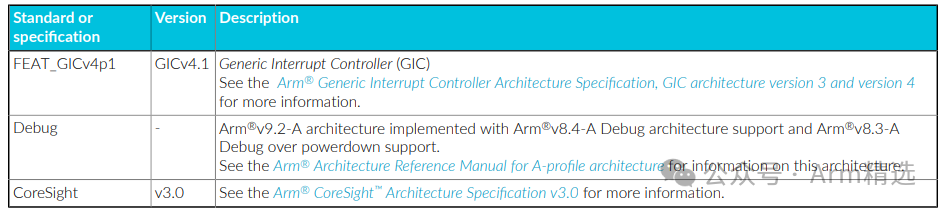

4 Supported Standards and Specifications

The Cortex-X925 core complies with the Armv9.2-A architecture. The Armv9.2-A architecture extends the Armv8-A architecture, encompassing Armv8.7-A. The Cortex-X925 core also complies with specific Armv8-A architecture extensions and supports interconnect, interrupts, timers, debugging, and tracing architectures.

The Cortex-X925 core supports AArch64 execution state from exception levels EL0 to EL3.

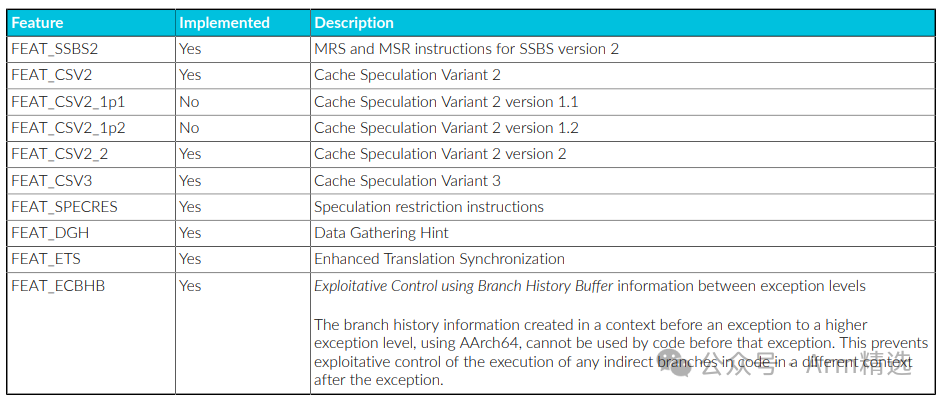

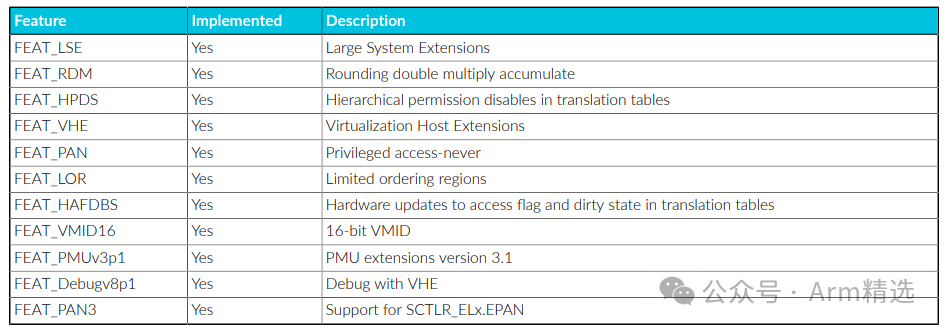

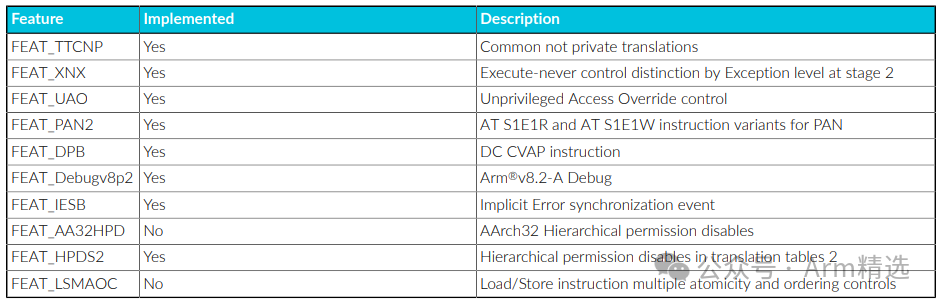

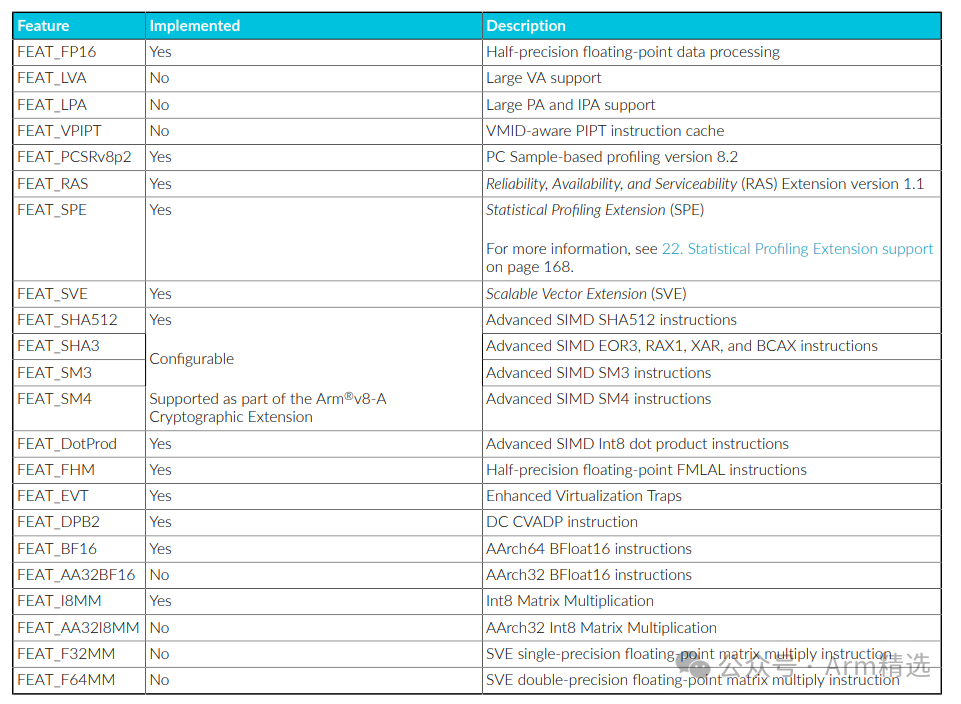

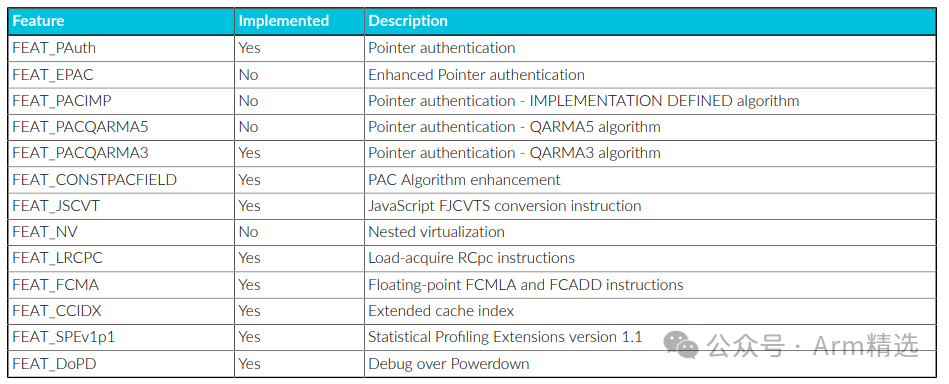

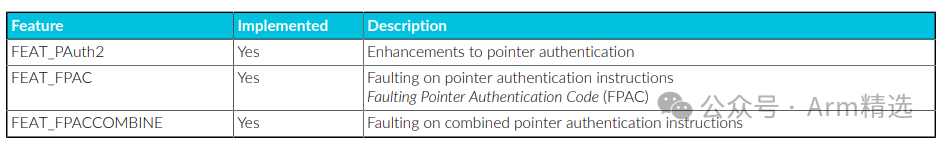

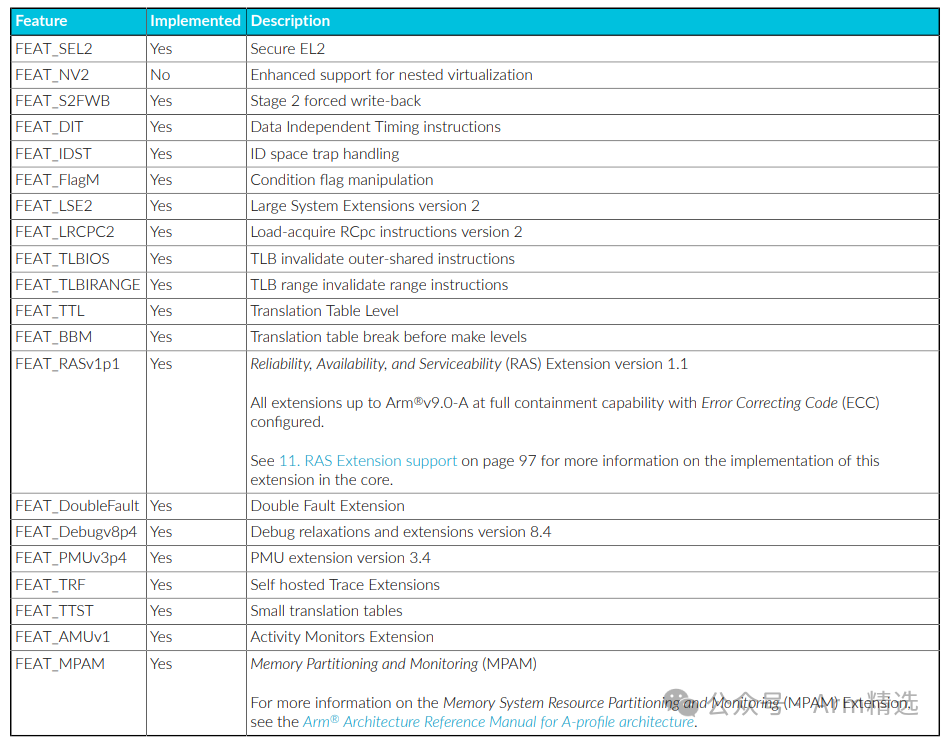

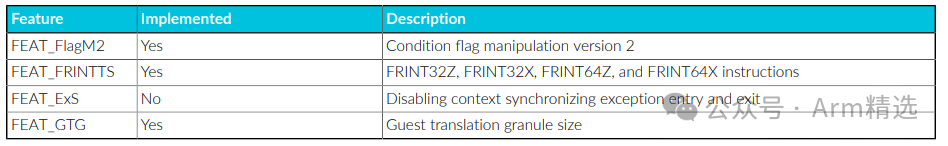

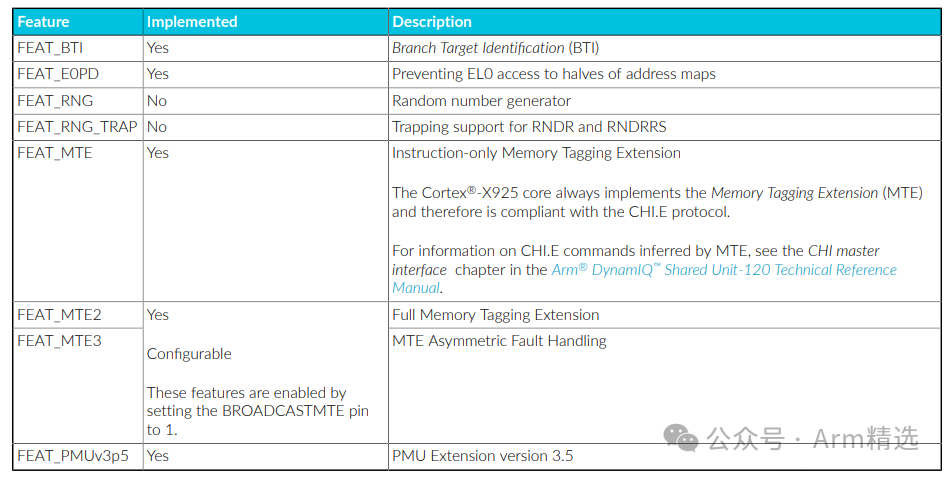

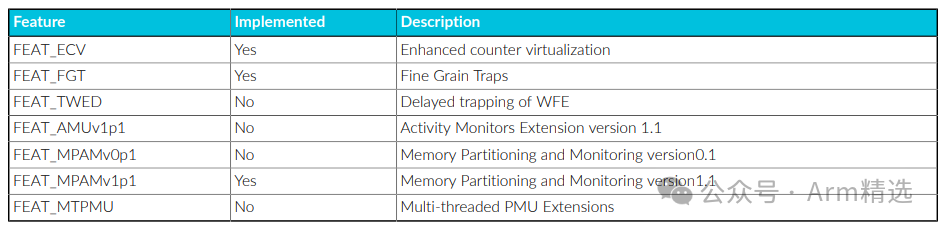

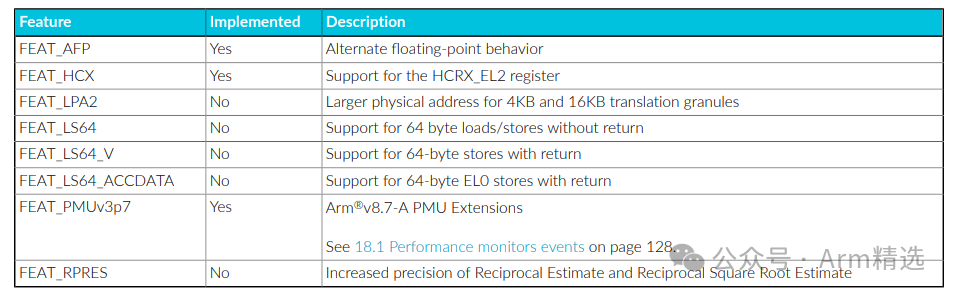

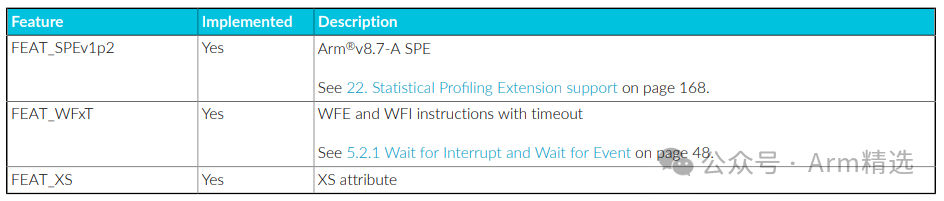

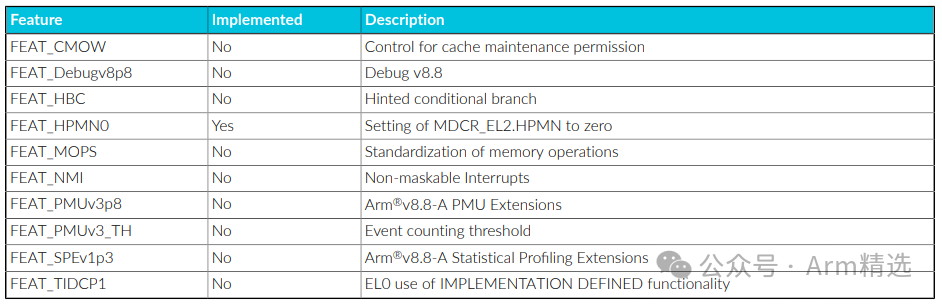

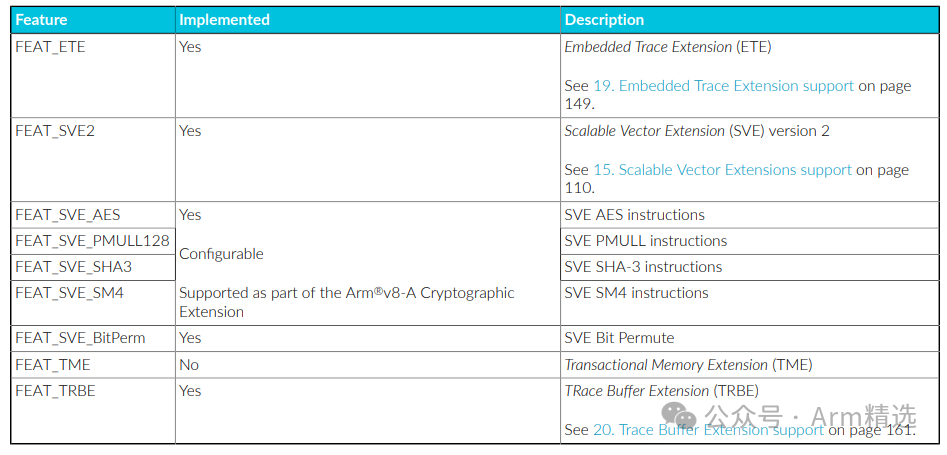

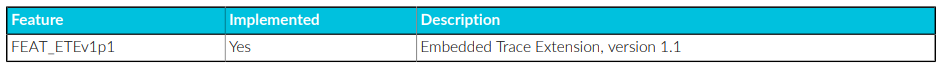

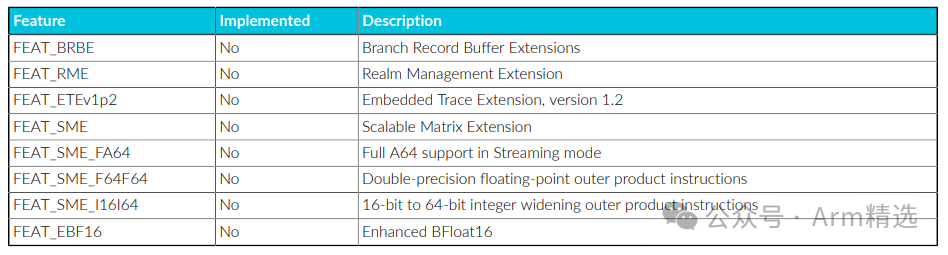

Not all architectural features are implemented in the Cortex-X925 core. The following table shows the implementation status of Armv8-A and Armv9-A features supported by the Cortex-X925 core. Each version of the Armv8-A and Armv9-A architecture has a separate table.

Note

Not all Armv8-A and Armv9-A architectural features are listed in the following table. For more information on all architectural features, refer to the Arm A-Profile Architecture Reference Manual.

The Cortex-X925 core is architecturally compatible with the DynamIQ™ Shared Unit-120. For a list of specific architectural versions and features supported by the DSU-120, refer to the “Supported Standards and Specifications” section in the Arm DynamIQ™ Shared Unit-120 Technical Reference Manual.

-

Implementation status of Armv8.0-A features in the Cortex-X925 core

-

Implementation status of Armv8.1-A features in the Cortex-X925 core

-

Implementation status of Armv8.2-A features in the Cortex-X925 core

-

Implementation status of Armv8.3-A features in the Cortex-X925 core

-

Implementation status of Armv8.4-A features in the Cortex-X925 core

-

Implementation status of Armv8.5-A features in the Cortex-X925 core

-

Implementation status of Armv8.6-A features in the Cortex-X925 core

-

Implementation status of Armv8.7-A features in the Cortex-X925 core

-

Implementation status of Armv8.8-A features in the Cortex-X925 core

-

Implementation status of Armv9.0-A features in the Cortex-X925 core

-

Implementation status of Armv9.1-A features in the Cortex-X925 core

-

Implementation status of Armv9.2-A features in the Cortex-X925 core

-

The following table shows other standards and specifications supported by the Cortex-X925 core.

5 Testing Features

The Cortex-X925 core provides test signals that enable the use of Automatic Test Pattern Generation (ATPG) and Built-In Self-Test (BIST) to test core logic and memory arrays.

The Cortex-X925 core includes an ATPG test interface that provides signals to control core Design for Test (DFT) features. Careful consideration must be given to how these signals are used to avoid DFT implementation issues.

Arm also provides a BIST interface that allows you to test RAM at operational frequencies. You can add your own BIST controller to automatically generate test patterns and perform result comparisons. Alternatively, you can choose to use EDA tools to directly test physical RAM instead of using the provided Arm interface.

For a list of test signals and their usage information, refer to the Test Design Integration Guidelines chapter in the Arm Cortex-X925 Core Configuration and Integration Manual.

For a list of external scan control signals, refer to the Test Design Integration Guidelines chapter in the Arm DynamIQ™ Shared Unit-120 Configuration and Integration Manual.

NoteThe Arm Cortex-X925 Core Configuration and Integration Manual and the Arm DynamIQ™ Shared Unit-120 Configuration and Integration Manual are confidential documents provided only after obtaining the appropriate product license.

6 Design Tasks

The Cortex-X925 core is delivered in a synthesizable RTL description form in SystemVerilog. Before using the Cortex-X925 core, it must be implemented, integrated, and programmed.

The following tasks can be performed by different teams:

Implementation

Implementers configure RTL, add vendor cells/memory, and transform the design into hard macro cells through synthesis, place and route (P&R) steps. Implementers choose options that affect the rendering of RTL source files. These options may impact the final macro cell’s area, maximum frequency, power consumption, and characteristics. Other components, such as DFT structures and power switches if necessary, can also be added to the implementation process.

Integration

Integrators connect macro cells to the SoC. This task includes connecting them to the memory system and peripherals. Integrators configure some features of the core by binding inputs to specific values. These configuration settings affect the startup behavior before software configuration and may limit the options available to software.

| Recommended Courses | “Mastering Armv8/Armv9 Architecture” Series |

| “Introduction to Trustzone/TEE/Security” Standard Edition | |

| Arm Selected – Platinum VIP Courses | |

| 🌍Consult vx: sami01_2023 |