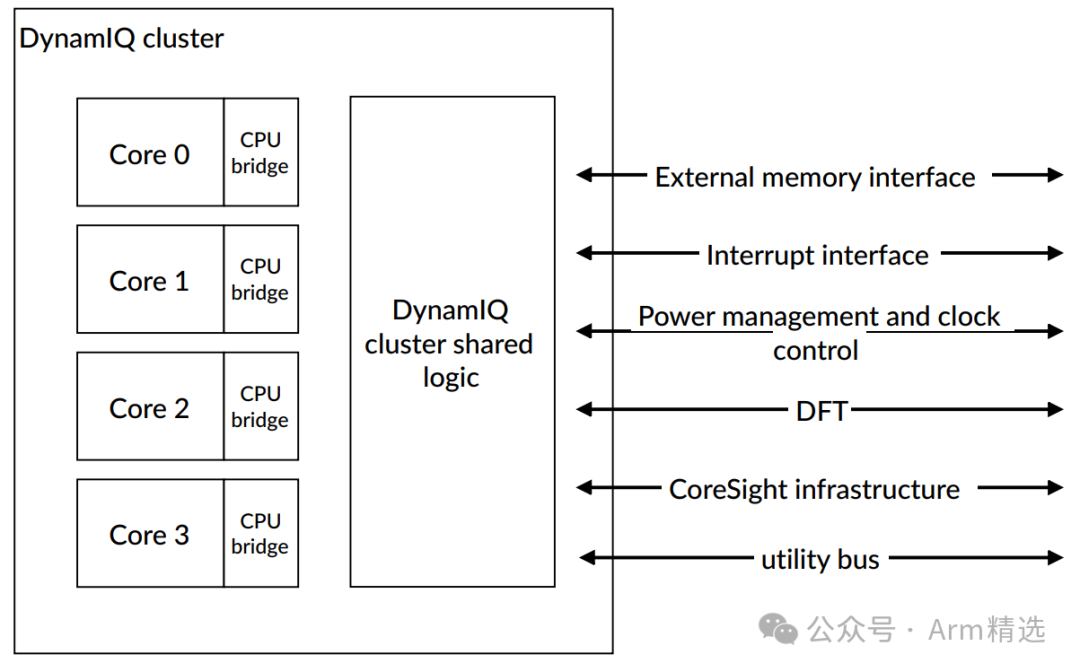

The Cortex-X925 core is a high-performance and low-power product that implements the Armv9.2-A architecture. The Armv9.2-A architecture extends the Armv8-A architecture and fully supports the Armv8.7-A version.The Cortex-X925 core is implemented within the DSU-120 DynamIQ cluster. It connects to the DynamIQ DSU120, which serves as a complete interconnect system with L3 cache and snoop control capabilities. This connection configuration is also used in systems with different types of cores, where the Cortex-X925 core acts as a high-performance core.The following diagram shows an example configuration containing four Cortex-X925 cores within a DynamIQ cluster. You can use the Cortex-X925 core in a standalone DynamIQ configuration, where a homogeneous DSU-120 DynamIQ cluster includes one or more Cortex-X925 cores. You can also use the Cortex-X925 core as a high-performance core in a heterogeneous cluster.Regardless of the cluster configuration, the Cortex-X925 core always possesses the same features as described below.

You can use the Cortex-X925 core in a standalone DynamIQ configuration, where a homogeneous DSU-120 DynamIQ cluster includes one or more Cortex-X925 cores. You can also use the Cortex-X925 core as a high-performance core in a heterogeneous cluster.Regardless of the cluster configuration, the Cortex-X925 core always possesses the same features as described below.

Core Features

Implements the Armv9.2-A A64 instruction setSupports AArch64 execution state at all exception levels (EL0 to EL3)Memory Management Unit (MMU)40-bit physical address (PA) and 48-bit virtual address (VA)Generic Interrupt Controller (GIC) CPU interface, connectable to external interrupt distributorsGeneric timer interface, supporting 64-bit count input from external system countersImplements Reliability, Availability, and Serviceability (RAS) extensionsImplements Scalable Vector Extension (SVE) and Scalable Vector Extension 2 (SVE2) with 128-bit vector lengthIntegrated execution units supporting advanced Single Instruction Multiple Data (SIMD) and floating-point operationsActivity Monitoring Unit (AMU)Supports optional cryptographic extensions

Cache

Separate L1 data and instruction cachesPrivate, unified L2 data and instruction cacheError protection on L1 instruction and data caches, L2 cache, and MMU translation cache (MMU TC) using parity or error-correcting code (ECC), supporting single-bit error correction and double-bit error detection (SECDED)Supports Memory Partitioning and Monitoring (MPAM)

Debug

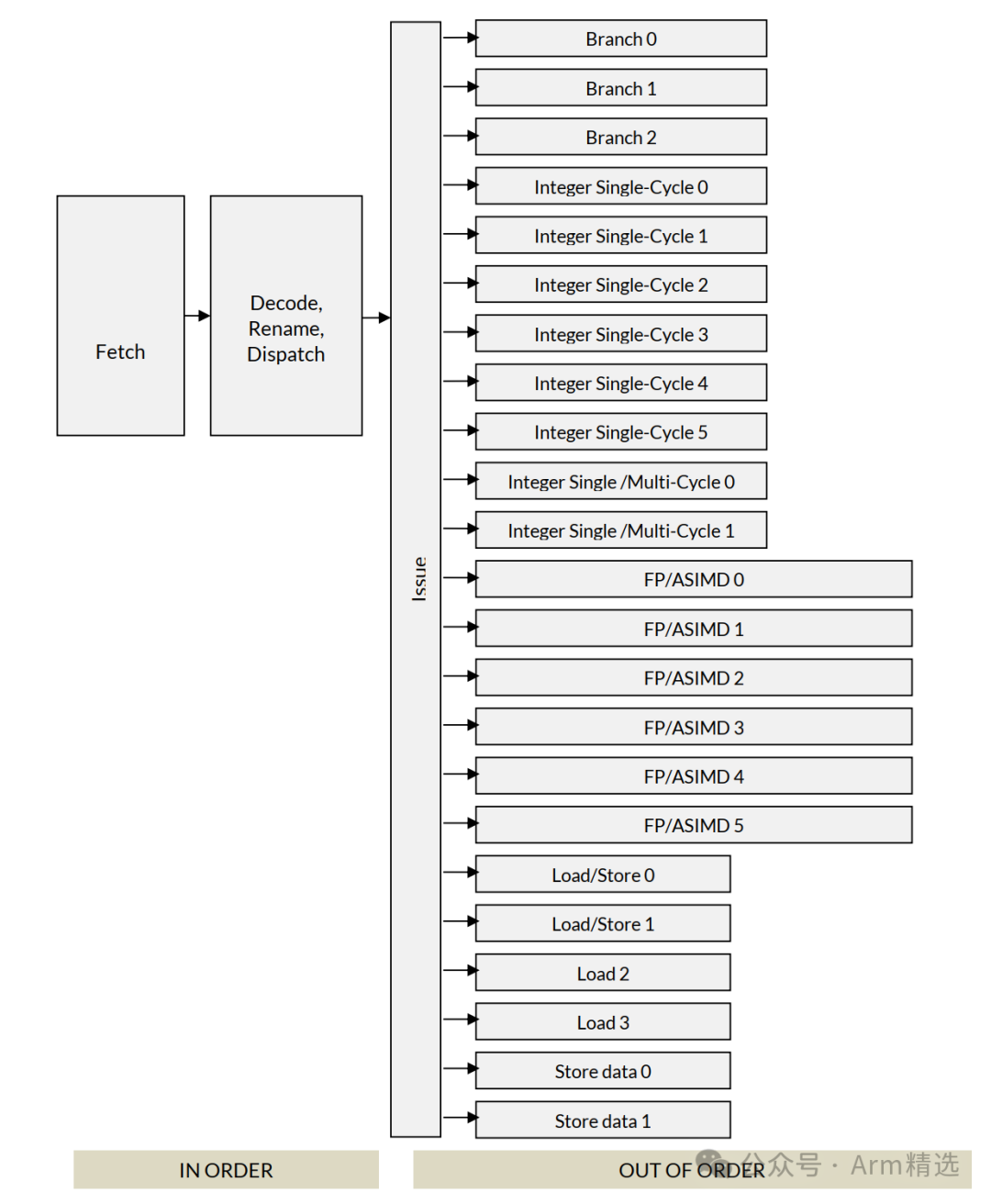

Arm®v9.2-A debug logicPerformance Monitoring Unit (PMU)Embedded Trace Extension (ETE)Trace Buffer Extension (TRBE)Statistical Profiling Extension (SPE)Optional Embedded Logic Analyzer (ELA), ELA-600Note that the Cryptographic Extension and ELA-600 require separate licensing.The following diagram describes the advanced instruction processing pipeline of the Cortex-X925. It features a three-level pipeline with 23 pipelines.Instructions are first fetched, then decoded into internal macro-operations (MOPs). Next, MOPs go through register renaming and dispatch stages. After the decoding stage, MOPs can be further split into two micro-operations (µOPs). Once dispatched, µOPs wait for their operands and are sent to one of the 23 issue pipelines in an out-of-order manner. Each issue pipeline can accept one µOP per cycle.

| Recommended Courses | “From Beginner to Mastering Armv8/Armv9 Architecture” – Three Sessions |

| “Trustzone/TEE/Security from Beginner to Master” – Standard Edition | |

| Arm Selected – Platinum VIP Courses💋 All Courses | |

| 🌍Consult via WeChat: sami01_2023 |