According to reports from Electronic Enthusiasts (by Zhou Kaiyang), for any major chip manufacturer, the choice of Instruction Set Architecture (ISA) is made with great caution. The ISA not only determines the ease of chip development but also dictates the software and development ecosystem tied to it, potentially impacting market competition. However, in this crucial decision, we find that many large manufacturers are beginning to invest in RISC-V.

Renesas: From Licensing to In-House Development

As one of the leading MCU manufacturers, especially in the automotive sector, Renesas has accumulated and developed multiple MCU product lines over the years. In the 32-bit MCU segment, there are products based on their proprietary CISC core, the RX series, as well as those based on the Arm Cortex-M architecture, the RA series. Nevertheless, Renesas is determined to expand into a third product line based on the RISC-V architecture.In fact, Renesas began its RISC-V initiatives quite early. For instance, the automotive control domain management MCU RH850/U2B, launched in 2021, integrated the MIMD accelerator core developed by NSI-TEXE, based on the RISC-V architecture, the DR1000C.The DR1000C has not only achieved ISO 26262 ASIL D certification but, due to its parallel processing capabilities, can help offload heavy computational tasks from the MCU, such as model predictive control, AI inference, and sensor data processing. This makes it suitable for industrial automation devices and also for automotive MCUs to assist in radar or other sensor fusion computations.Additionally, Renesas has partnered with Andes Technology to continue launching RISC-V products for specific markets, including ASSP and MPU products that integrate RISC-V cores, such as RISC-V-based motor control ASSP MCUs and the 64-bit RZ/Five. The former is mainly used in industrial control and human-machine interaction scenarios, while the latter is primarily for gateway control.In the RISC-V domain, Renesas has not only opted to license third-party cores but also harbors ambitions for in-house core development, thereby opening up a new optional product line for its general-purpose MCUs. On November 30, 2023, Renesas announced the launch of its first-generation 32-bit RISC-V CPU core, aimed at creating a new open and flexible platform for IoT, consumer electronics, healthcare, and industrial systems, complementing its existing RX and RA series.

Renesas’ self-developed RISC-V core / RenesasAs its first self-developed RISC-V core, its CoreMark/MHz reached 3.27, which is lower than the previously used Andes Technology N22 core and its self-developed RXv1 core. This indicates that the scale of its first self-developed RISC-V core is not high, primarily aimed at ultra-low power MCU designs.Recently, Renesas also released its first general-purpose 32-bit RISC-V MCU based on this self-developed core, the R9A02G021, which is an ultra-low power 48MHz MCU product. The R9A02G021 integrates 128KB of code flash memory, 4KB of data flash memory, and 16KB of SRAM along with rich I/O. In terms of development tools, Renesas’ e² studio continues to provide IDE support for the R9A02G021, and IAR and SEGGER have also quickly followed up with development support for this MCU.Even with the new RISC-V core, it does not mean that Renesas will abandon the subsequent development of other product lines. From its roadmap, it is evident that Renesas has plans for product expansion and enhancement across the RL78, RX, and RA series to achieve higher performance and integration, while also incorporating certain AI/ML functionalities. Meanwhile, Renesas may also develop higher-spec RISC-V cores in the future for higher-performance RISC-V MCU designs.

Qualcomm: Leading the Charge in Wearables and Automotive

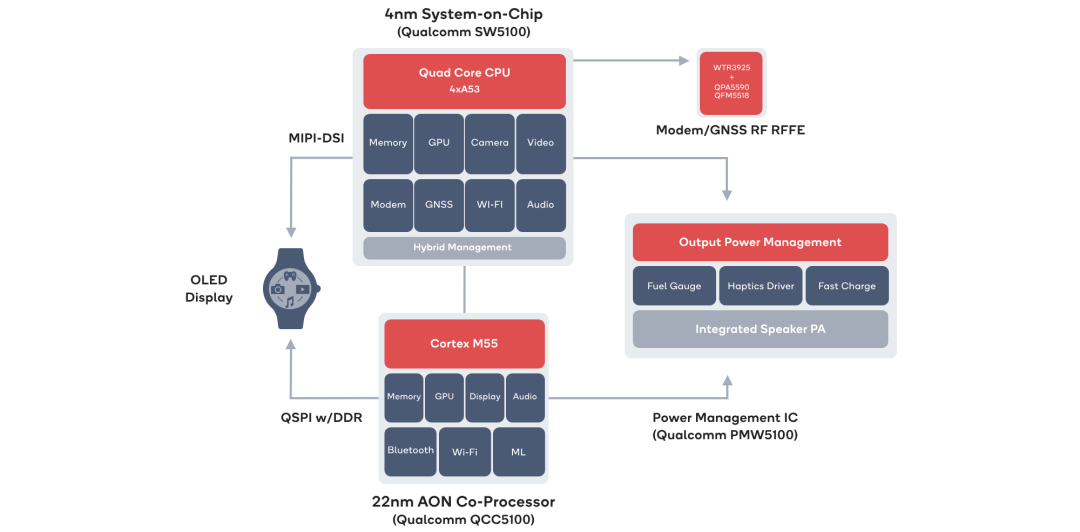

As a staunch supporter of the Arm camp, Qualcomm has gradually begun to shift some of its development resources towards RISC-V. At the 2022 RISC-V Global Summit, Qualcomm executives announced that RISC-V had already been utilized in the microcontroller design of the Snapdragon 865 SoC released in 2019, with over a hundred million RISC-V cores shipped. Although Qualcomm did not disclose whether subsequent Snapdragon mobile SoCs would continue to use this design, it is sufficient to demonstrate the importance Qualcomm places on RISC-V.Last year, many people likely saw the news related to RISC-V, where Qualcomm, along with Bosch, Infineon, NXP, and Nordic, jointly established a RISC-V startup named Quintauris. The company’s goal is to promote the global adoption of RISC-V by supporting the development of next-generation hardware, thereby accelerating the commercialization of RISC-V architecture products and providing reference architectures. According to its official website, the initial focus of this company is on automotive applications, indicating that Qualcomm may likely launch corresponding RISC-V automotive chip products based on this reference architecture in the future.Shortly after the announcement of the joint establishment of the RISC-V company, Qualcomm and Google jointly announced that they would strengthen their collaboration to develop the next-generation Snapdragon Wear platform based on the RISC-V architecture, thereby supporting Google’s next-generation Wear OS solutions. Qualcomm explicitly stated that they would promote RISC-V wearable solutions globally. However, it remains unclear how RISC-V will be positioned in this new Snapdragon Wear wearable hardware platform.From past wearable chips, Qualcomm primarily used mid-range Arm cores to create related SoCs. For instance, from Wear1100 to Wear3100, they were all designed based on the Arm Cortex-A7 for the CPU portion. It wasn’t until the Wear4100+ launched in 2020 that a quad-core A53 CPU with a co-processor design was introduced.

Snapdragon W5+ Gen1 Wearable Hardware Platform / QualcommIn the latest W5+ Gen1 platform, Qualcomm continues to use the quad-core A53 with a co-processor design, but the main CPU process has changed from 12nm to 4nm, and the co-processor has also shifted from QCC1110 (Cortex-M0) to QCC5100 (Cortex-M55). According to Qualcomm, the co-processor is primarily used to support Google Wear OS, ASOP, and RTOS, and it only requires a mature 22nm process.In the joint announcement between Qualcomm and Google, it was also clearly stated that the new platform is mainly used to support Wear OS. This suggests that Qualcomm’s new RISC-V hardware could serve as either the main CPU or the co-processor. Regardless, both companies have joined the RISC-V software ecosystem (RISE), and whichever design solution is adopted will bring new breakthroughs in software development for RISC-V in the wearable domain.

MIPS: Focusing on High-Performance Processors

Once upon a time, MIPS was also a mainstream RISC processor architecture, even poised to rival Arm and x86. Even the domestic Longxin used the MIPS architecture before developing the LoongArch architecture. MIPS is known for designing processors with multiple pipelines, supporting virtualization, and even many ADAS systems still run on MIPS processors.However, after successfully launching several generations of 32-bit and 64-bit RISC processors, MIPS did not surpass x86 but was overshadowed by the rising Arm. During this period, MIPS even attempted an open-source solution but still fell into obscurity. Therefore, in March 2021, MIPS announced the termination of MIPS architecture development and shifted the entire company towards RISC-V architecture.Despite experiencing various twists and turns during its acquisition and transition, MIPS still retains some microarchitecture patents and has rich experience in processor design and development, which provides a significant advantage for RISC-V.In 2022, MIPS launched its newly developed RISC-V processor series, eVocore, which currently includes the P8700 and I8500 multi-processor IP cores. The P8700 is designed for high-performance computing scenarios in data centers, featuring a rare 16-stage pipeline design, along with out-of-order execution and multi-threading capabilities, and its scalability allows it to support up to 512 cores. MIPS claims that its single-thread performance far exceeds that of existing RISC-V CPU IPs on the market, although specific benchmark parameters have not been provided.In addition to high-performance general-purpose CPU cores like the P8700, MIPS’s recent movements indicate that it is also focusing on AI computing. For instance, MIPS welcomed its new chief architect, Brad Burgess, who previously participated in the design of the out-of-order vector unit for the P870 processor at SiFive. Furthermore, they have opened a new R&D center in the United States, planning to collaborate with local universities to develop innovative AI computing solutions for the automotive, data center, and embedded markets.

Final Thoughts

It is evident that for the vast majority of major manufacturers, RISC-V is becoming an increasingly viable product design direction. This fully demonstrates the openness of RISC-V, as well as a more mature software and hardware development environment and lower design risks. Although most manufacturers currently maintain a trial-and-error mindset, with the continuous growth of the RISC-V ecosystem, it is believed that more major manufacturers will embrace RISC-V.

Disclaimer: This article is originally from Electronic Enthusiasts, please indicate the source above when reprinting. For group discussions, please add WeChat elecfans999,for submission and interview requests, please email [email protected].

More Hot Articles to Read

-

Range exceeds 1000 kilometers, nearly 900V ultra-fast charging, this year marks the beginning of solid-state battery era

-

Server power supplies heading towards 10kW, third-generation half may be the only way out

-

AI computing power GPUs are taking off, supported by continuous power management

-

Xiaomi SU7 car starts at 215,900 yuan! 50,000 units sold in 27 minutes, core suppliers exposed!

-

The ultimate form of AI PCs? Copilot replaces the Windows key, NPU becomes standard

Click to Follow and Bookmark Us

Set us as a bookmark to not miss any updates!