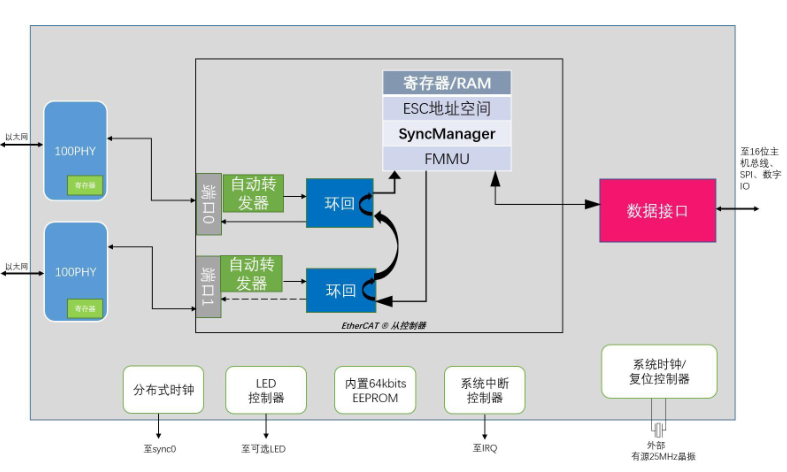

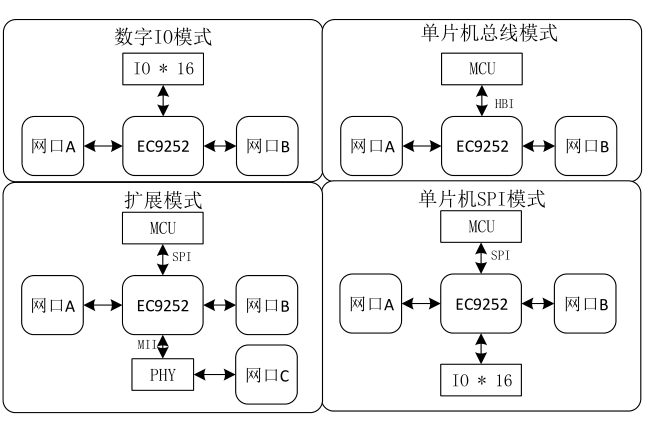

Currently, the EtherCAT slave solutions available on the market mainly include the following types. The traditional ones are chips like the Beckhoff ET1100, which require a master control + ESC + PHY, resulting in higher costs, making them unsuitable for the competitive pace of domestic general-purpose products. The second type integrates PHY with the ESC, such as LAN925 and AX58100, which reduces costs relatively. The third type includes solutions like Renesas n2l and Infineon, where the master control integrates the ESC, steadily improving performance. Another approach is to implement EtherCAT slaves using IP cores integrated in FPGAs; some advanced players even skip the IP cores and directly use FPGAs to implement EtherCAT.

From a cost perspective, the higher the chip integration, the better the cost-performance ratio. However, aside from cost-performance, there is also the issue of performance and user design. Integrating PHY and ESC together can reduce the density of circuit board connections, improve anti-interference capability, and enhance reliability.

Integrating the master control with the ESC significantly improves performance, as there is an SPI communication between the ET1100 master control chip and the ESC, which is limited to a few megabits at best. Even if EtherCAT can reach gigabit speeds, it is still constrained; however, parallel communication can also be used.

The domestic EtherCAT chip technology is also developing rapidly. I remember that in 2020, domestic EC chips were quite rare. Just three years later, there are many solutions that compete with the ET1100, but there are still few that integrate PHY, like the Renesas n2l. The Huichuan 660N uses Renesas’s solution. However, today we are discussing domestic chip solutions that compete with the LAN9252.

Feel free to add WeChat “EtherCAT18” to discuss EtherCAT technology and solutions.