Introduction

The author has been involved in embedded software development for nearly five years, primarily using ARM Cortex M core series microcontrollers. During these five years, thanks to the existence of C language compilers, I was able to develop without touching assembly language; however, it seems that I have missed some scenery and have not appreciated the beauty of compilers and CPUs. Therefore, I decided to explore the wonderful ARM CPU architecture and the mysteries of C language compilers during my boring weekend breaks by seeking information, conducting experiments, and drawing conclusions. (Because I personally do not agree with the teaching methods of microcomputer principle courses in schools).

1. ARM CPU Architecture

The ARM CPU architecture[1] is a family of Reduced Instruction Set Computing (RISC) architectures for computer processors. It is the most widely used processor architecture in the world, with billions of ARM-based devices shipped each year, ranging from sensors, wearable devices, smartphones, to supercomputers.

The ARM CPU architecture is based on a RISC instruction set and includes:

-

A unified register file, where instructions are not limited to specific registers; -

A load/store architecture, where data processing operates only on register contents rather than directly on memory contents; -

Simple addressing modes, where all load or store modes are determined solely by register contents and instruction fields.

Depending on different application scenarios, the ARM CPU architecture is divided into:

| Architecture Definition | Use Cases | Implementation (Processor Cores) |

|---|---|---|

| A Series | Complex computer applications (servers, networking devices, smartphones, TVs) | Cortex-A, Neoverse |

| R Series | For scenarios requiring real-time response (strict security applications, applications requiring deterministic responses, autonomous driving) | Cortex-R |

| M Series | Devices where power consumption and size are relatively important, especially embedded devices and IoT devices, such as small sensors, communication modules, smart home products, etc. | Cortex-M |

In this series of articles, we will primarily explore the Cortex M core without considering the Cortex A series and Cortex R series.

2. Cortex M Core

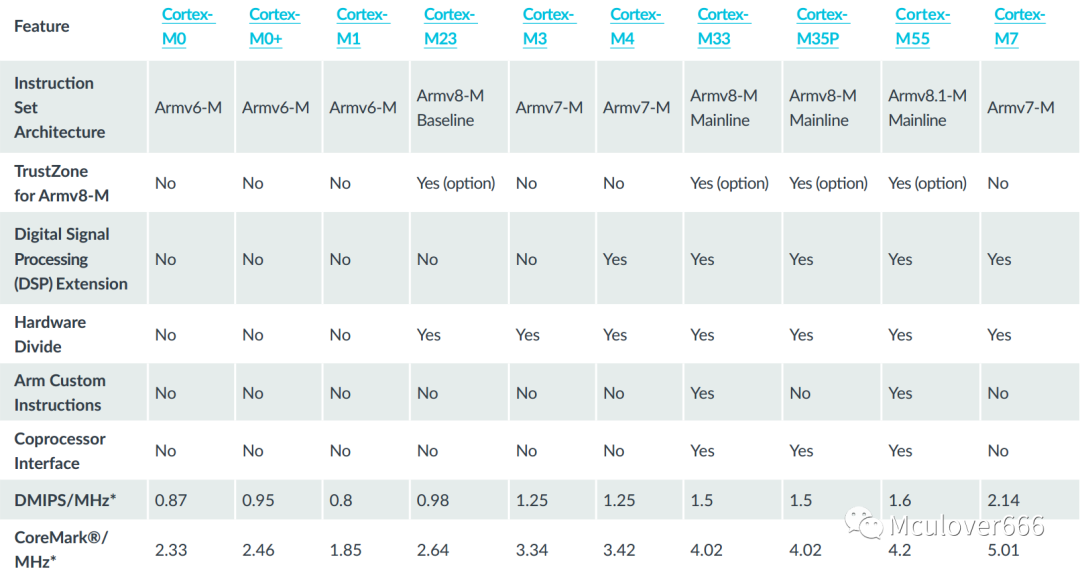

The Cortex-M processor family is based on the ARM M architecture definition, providing low latency and highly deterministic operation for embedded systems. The main Cortex-M series cores are shown in the figure below:

From the figure, it can be roughly seen:

1. The Cortex-M0, Cortex-M0+, and Cortex-M1 series cores use the Armv6-M architecture, while the commonly used Cortex-M3, Cortex M4, and Cortex M7 series cores use the Armv7-M architecture. The Cortex-M23 series uses the Armv8-M Baseline architecture, and the Cortex-M33, Cortex-M33P, and Cortex-M55 series use the Armv8-M Mainline architecture.

2. Starting from the Cortex-M23 series, the Cortex-M cores begin to have TrustZone features.

3. Only the Cortex-M4, Cortex-M7, Cortex-M33, Cortex-M35P, and Cortex-M55 series have Digital Signal Processing extensions (DSP).

4. The Cortex-M33 and Cortex-M55 series have ARM Custom Instructions.

5. The Cortex-M33, Cortex-M35P, and Cortex-M55 series have Co-Processor Interfaces.

Next, let’s learn about them one by one.

1. Cortex M0

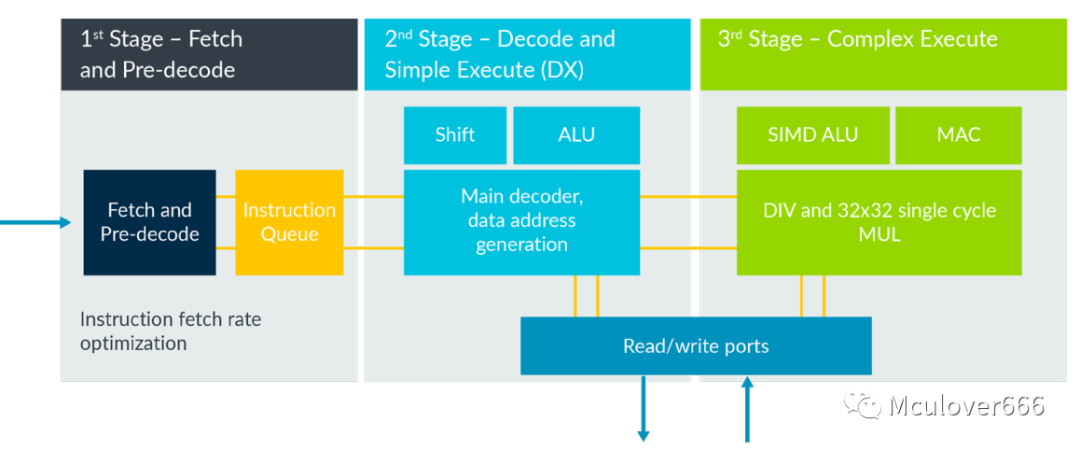

The Cortex M0[2] processor is one of the smallest processors from ARM, characterized by its small size, designed to enable developers to achieve 32-bit performance at an 8-bit price point. The Cortex M0 processor uses the AHB-Lite bus, has a three-stage pipeline, and supports part of the Thumb/Thumb-2 instruction set.

The Cortex M0 processor uses the AHB-Lite bus, has a three-stage pipeline, and supports part of the Thumb/Thumb-2 instruction set.

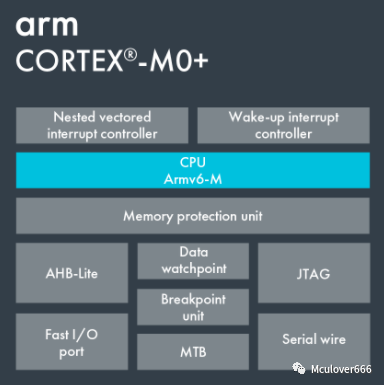

2. Cortex M0+

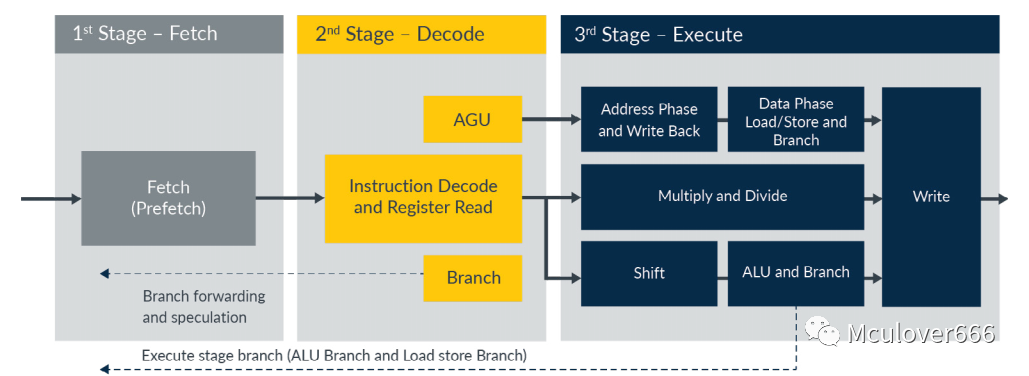

The Cortex M0+[3] processor further reduces power consumption and improves performance based on the Cortex M0 processor. The Cortex M0+ processor uses the AMBA AHB-Lite bus, reduces the pipeline to two stages, and supports part of the Thumb/Thumb-2 instruction set.

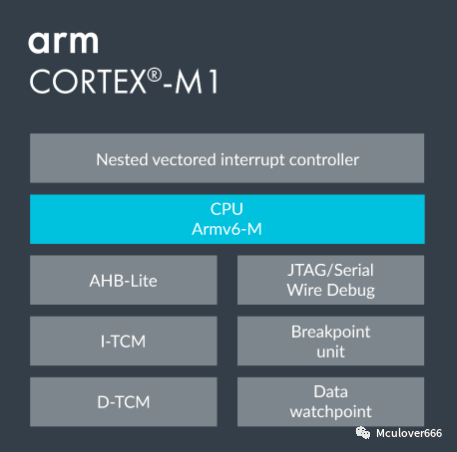

3. Cortex M1

The Cortex M1[4] is the first processor designed specifically for implementation on FPGA. It uses the AMBA AHB-Lite bus, has a three-stage pipeline, and supports part of the Thumb/Thumb-2 instruction set.

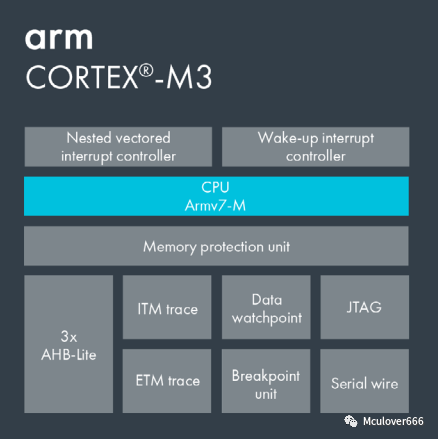

4. Cortex M3

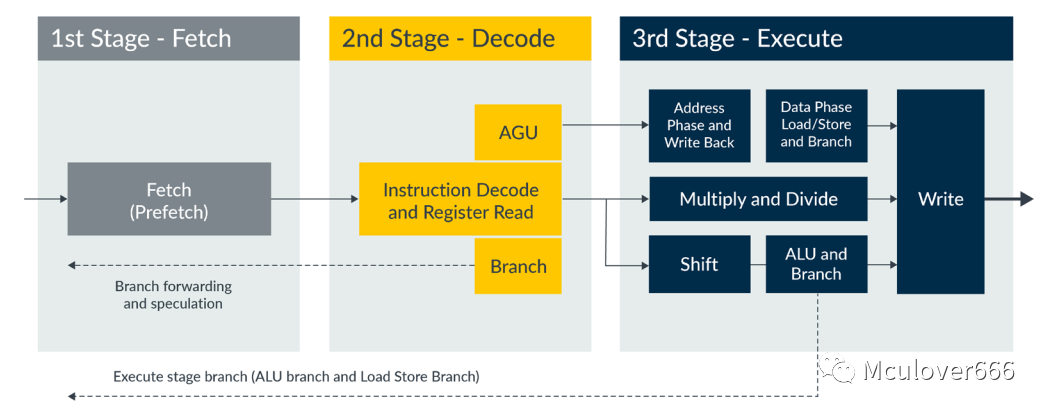

The Cortex-M3[5] processor is designed for high-performance, low-cost platforms, including automotive body systems, industrial control systems, wireless networks, sensors, etc. It uses three AMBA AHB-Lite buses (Harvard bus architecture), has a three-stage pipeline, supports part of the Thumb/Thumb-2 instruction set, and supports 8 to 256 priority levels.

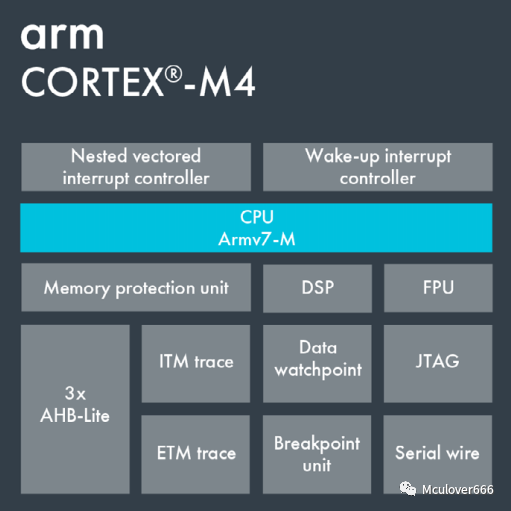

5. Cortex M4

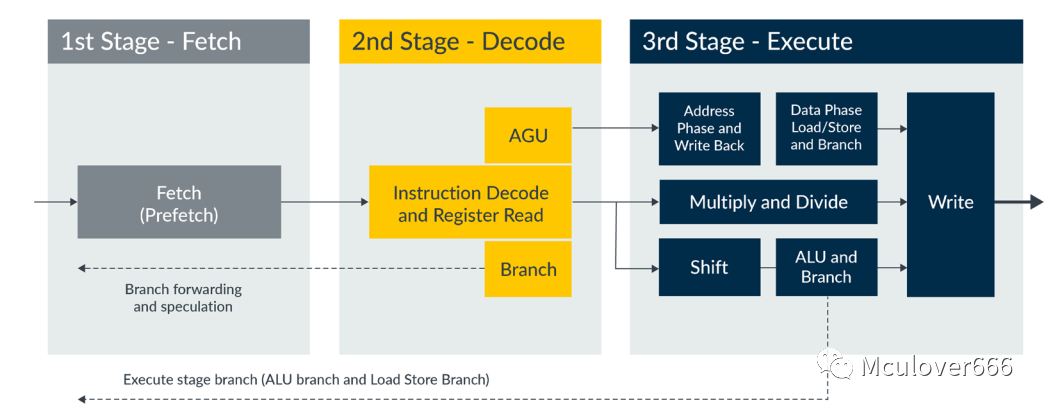

The Cortex-M4[6] processor is an efficient embedded processor, using three AMBA AHB-Lite buses (Harvard bus architecture), has a three-stage pipeline, supports part of the Thumb/Thumb-2 instruction set, and supports 8 to 256 priority levels. Compared to the Cortex-M3, it adds DSP extensions and an optional single-precision floating-point unit.

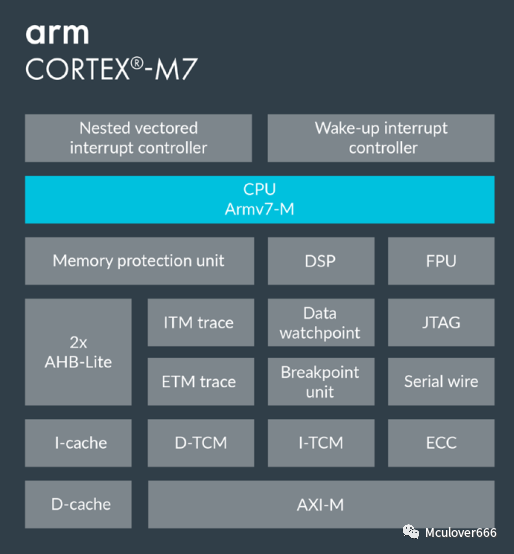

6. Cortex M7

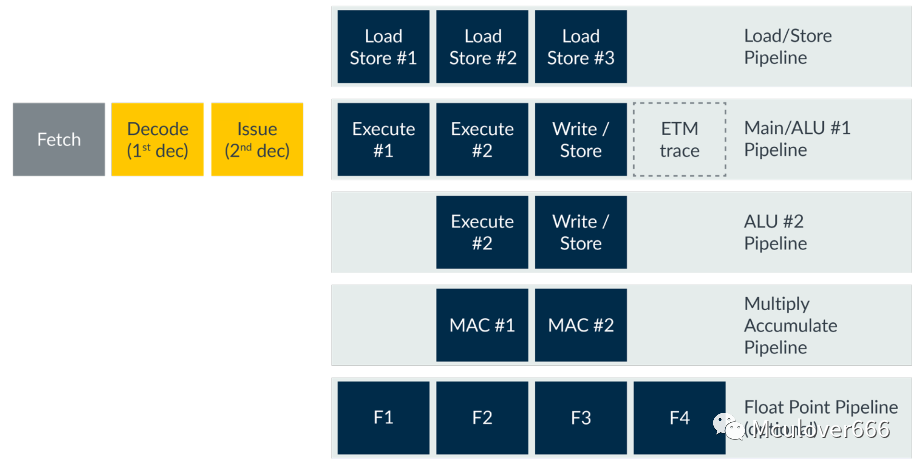

The Cortex M7[7] processor is a high-performance, energy-efficient processor with a 6-stage superscalar pipeline, supports the Thumb/Thumb-2 instruction set, supports 8 to 256 priority levels, and supports DSP extensions and an optional single-precision floating-point unit. It uses one 64-bit AMBA4 AXI bus, one 32-bit AHB peripheral interface, and one 32-bit AMBA AHB slave interface for external host access to TCM memory, featuring instruction cache, data cache, instruction TCM, and data TCM.

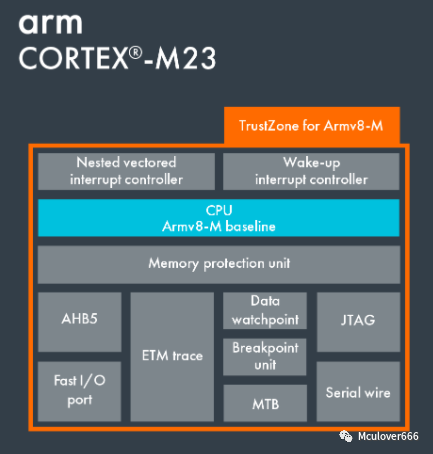

7. Cortex M23

The Cortex M23[8] processor is a very simple processor, ideal for most IoT and embedded applications requiring security, featuring Cortex-M23 with TrustZone.

The Cortex-M23 uses the Armv8-M baseline architecture, has a 2-stage pipeline, uses the AMBA 5 AHB bus, supports part of the Thumb/Thumb-2 instruction set, and supports 4 priority levels. It also adds instruction support for hardware single-cycle multiplication (32×32) and fast division (32/32).

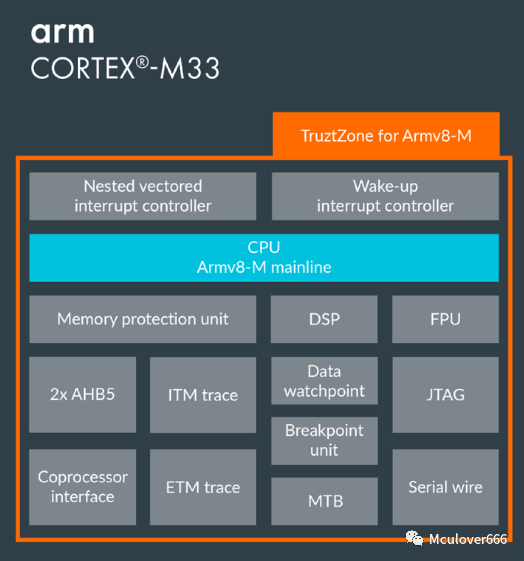

8. Cortex M33

The Cortex-M33[9] is suitable for embedded and IoT application scenarios requiring effective security or digital signal control. The Cortex-M33 has many optional features, including DSP extensions, TrustZone security features for hardware-enforced isolation, a co-processor interface, and a memory protection unit.

The Cortex-M33 uses the Armv8-M Mainline architecture, has a 3-stage pipeline, uses two AMBA5 AHB buses (Harvard architecture), supports the Thumb/Thumb-2 instruction set, supports 8 to 256 interrupt priority levels, has optional TrustZone for Armv8-M support, and supports optional DSP/SIMD instructions in DSP extensions, with optional co-processor interface support.

Recommended is an article by a prominent author: In-depth analysis, straightforward, detailing the features of Cortex-M23/33[10].

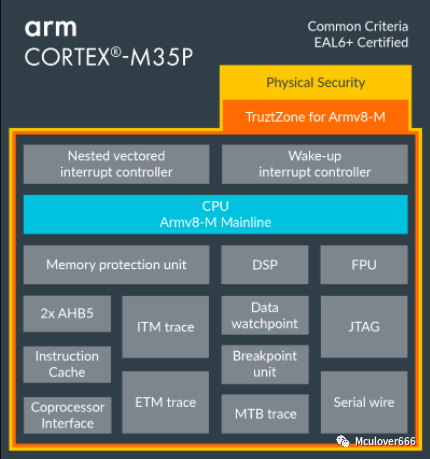

9. Cortex M35P

The Cortex-M35P[11] processor uses TrustZone for Armv8-M, with hardware security and optional software isolation features. For embedded developers looking to prevent physical tampering and seeking higher-level security certification, ARM offers the Cortex-M35P processor.

The Cortex-M35P uses the Armv8-M Mainline architecture, has a 3-stage pipeline, uses two AMBA5 AHB buses (Harvard architecture), supports the Thumb/Thumb-2 instruction set, supports 8 to 256 interrupt priority levels, has optional co-processor interface support, TrustZone for Armv8-M support, DSP support, and features physical security with built-in protections against invasive and non-invasive attacks.

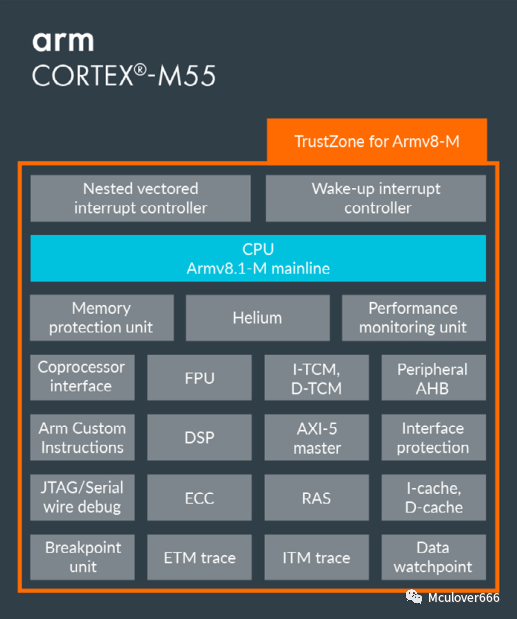

10. Cortex M55

The latest generation of Cortex M series processors is the Cortex M55.

The Cortex-M55[12] is the first processor based on the Armv8.1-M architecture, utilizing ARM Helium technology (MVE, M-series vector extension), bringing enhanced machine learning levels and signal processing performance to the next generation of small embedded devices, including wearable devices and smart voice devices.

The Cortex-M55 has a 4-stage pipeline, uses the AMBA 5 AXI5 64-bit host bus, has optional 64-bit co-processor interface support, optional TrustZone support, and optional Helium technology support, and supports 32-bit DSP/SIMD instruction extensions in DSP extensions.

Conclusion

After getting to know the members of the Cortex-M family, it can be seen that ARM Cortex-M is increasingly focusing on security and AI performance, which gives us a direction for development. The future of IoT development is no longer just about connecting to the cloud platform to report data; it is more about enhancing the security capabilities and AI capabilities of IoT devices. After all, hardware devices being compromised is more frightening than a computer virus. If the AI processing capability at the edge is greatly improved, data processing can be completed directly on the terminal without consuming unnecessary cloud computing power~

Thus, the first stop of the ARM exploration journey ends here! See you next time!

Note: All images in this article are sourced from ARM.

References

ARM CPU Architecture: https://developer.arm.com/architectures/cpu-architecture