Recently, NVIDIA released the "Grace" CPU based on the Arm architecture, attracting considerable attention from peers in the hard technology field. This CPU and server architecture, designed specifically for accelerated computing, can provide up to 10 times the performance compared to the latest NVIDIA DGX systems based on x86 CPUs when combined with NVIDIA's GPUs.

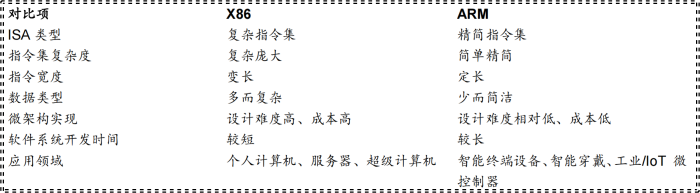

What are the similarities and differences between Arm and x86 architectures? What impact does choosing different instruction set architectures have on CPUs? What is the development situation in China and abroad? With these questions in mind, let’s explore CPU architecture.

What is a CPU?

The Central Processing Unit (CPU) is the core of a computer system. The main functions of the CPU include processing instructions, executing operations, controlling timing, and handling data. The central processor mainly includes components such as the arithmetic logic unit, controller, and registers. Additionally, the CPU includes cache memory and buses for data and control connections.

The arithmetic logic unit is a multifunctional operation unit that primarily performs related logical operations, such as executing shift operations and logical operations. In addition, the arithmetic logic unit can perform fixed-point or floating-point arithmetic operations, as well as address calculations and conversions. The controller is mainly used to analyze instructions and issue corresponding control signals. Registers are used to temporarily store instructions, data, and address information.

On November 15, 1971, Intel Corporation (INTC US, unrated) launched the world’s first commercially available microprocessor, the Intel 4004, which is regarded as the beginning of CPU development history. As a 4-bit processor, the Intel 4004 was manufactured using a 10um process on a 2-inch wafer, integrating 2,300 transistors, with a main frequency of 740kHz.

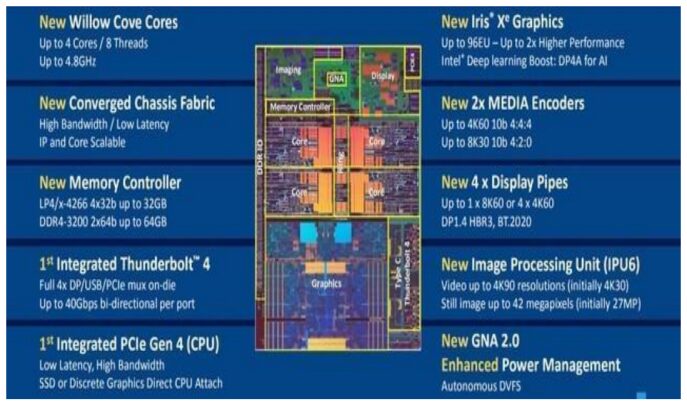

Fast forward 49 years to 2020, the eleventh generation Core processor chip, built on Intel’s 10nm process, integrates over 10 billion transistors and can reach a maximum frequency of up to 4.8GHz. This CPU chip is no longer a single CPU but integrates various components, including the traditional CPU core, Willow Cove, Iris X graphics processor, memory controller, image processor, media decoder, power management, neural accelerators, and various high-speed interface controllers. The Willow Cove core is the traditional CPU integrated into this CPU chip.

Chart: Intel’s Eleventh Generation Core Processor Chip

Instruction sets are a collection of commands that “give orders to computer hardware”.

Computer instructions are commands that can be directly recognized by computer hardware. An instruction is composed of a string of binary numbers. An instruction typically consists of two parts: the opcode and the address code. The opcode indicates the type or nature of the operation the instruction is to perform, such as fetching data, performing addition, or outputting data; the address code specifies the content of the target object or the address of the storage unit. A computer program is executed on hardware through thousands of instructions. A program is compiled into assembly language and then translated into machine code line by line by an assembler. These machine codes are represented by machine language consisting of 0s and 1s, which are computer instructions.

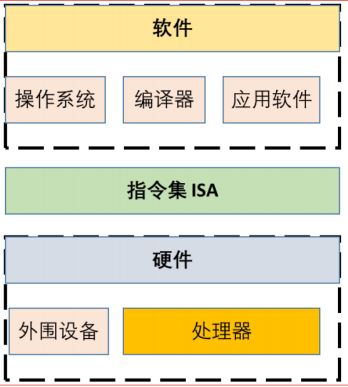

The Instruction Set Architecture (ISA) refers to a set of instructions used in a type of CPU to compute and control the computer system. The ISA mainly specifies instruction formats, addressing modes (addressing range, addressing mode, addressing granularity, memory access methods, address alignment, etc.), data types, and registers. The instruction set typically includes three main types of instructions: operation instructions, branch instructions, and memory access instructions.

In addition, it also includes architecture-related instructions, complex operation instructions, and other special-purpose instructions. Therefore, the instruction set architecture executed by a CPU not only determines the capabilities required by the CPU but also dictates the instruction format and the structure of the CPU. X86 architecture and ARMv8 architecture fall within the realm of instruction set architecture.

Complex Instruction Set Computer (CISC) vs. Reduced Instruction Set Computer (RISC)

Instruction set architectures can be classified based on their complexity into Complex Instruction Set Computer (CISC) and Reduced Instruction Set Computer (RISC).

CISC and RISC instruction set architectures emerged successively in the optimization development of computer instruction systems. In the early days of computer development, the optimization direction was to set some complex instructions, transforming commonly used functions originally implemented by software into a hardware instruction system to improve the execution speed of computers. Such a computer system is referred to as a complex instruction system computer.

In the 1980s, the basic idea of simplifying computer instruction functions was proposed, retaining simple instructions that could be executed in one clock cycle while implementing more complex functions through a subroutine. This type of computer system is known as a Reduced Instruction Set Computer.

Chart: The instruction set is the standard specification for interaction between hardware and software in computer systems.

X86 architecture is currently the only mainstream complex instruction set (CISC) that dominates the personal computer and server processor market. The X86 architecture was released by Intel in 1978. Over the past four decades, the X86 family has continuously expanded, moving from desktops to laptops, servers, and supercomputers.

Currently, the X86 architecture is licensed to three companies: Intel, Advanced Micro Devices (AMD US, unrated), and VIA Technologies of Taiwan. Among them, Intel and AMD’s X86 processors dominate the desktop and laptop markets. According to a report by IDC in 2017, X86 processors hold a remarkable 96% market share in the server market. According to statistics from Mercury Research, in 2019, VIA Technologies only held a 0.1% market share of X86 desktop processors.

The ARM instruction set architecture, as the most successful RISC architecture, dominates the smartphone and Internet of Things (IoT) chip processor markets. According to NVIDIA’s announcement, chips based on ARM architecture have shipped a cumulative total of 18 billion units. ARM architecture processors account for over 90% of the market share in areas such as smartphone chips, automotive information chips, wearable devices, and IoT microcontrollers.

In the 1990s, MIPS and Alpha, as well-known RISC architectures, failed in the competition against X86 in the computer market and weakened by missing the rapid development opportunities in smart terminals. The RISC-V architecture, released in 2010, has attracted significant attention from the global academic and industrial community due to its open-source characteristics since its inception. Top global universities, research institutions, and chip giants have participated, and various governments have introduced policies to support the development and commercialization of RISC-V. RISC-V is expected to become the third pole of ISA (instruction set architecture) after X86 and ARM.

Processor Microarchitecture: The Physical Circuit Implementing the Instruction Set Architecture

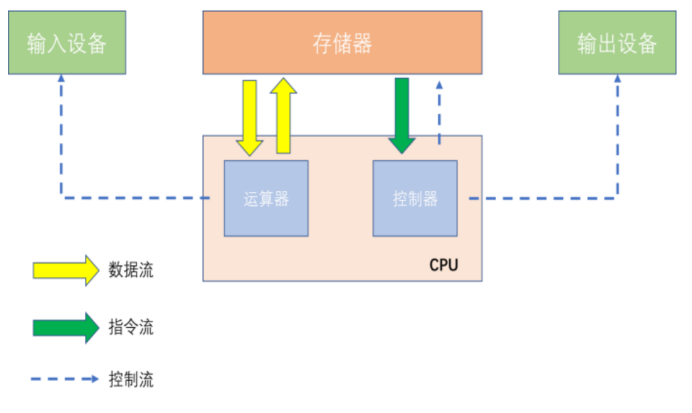

The Von Neumann architecture is the foundation of modern computers. In 1946, Hungarian-American scientist John von Neumann proposed the stored-program concept, treating the program itself as data, storing the program and the data it processes in the same way, and determining the five main components and basic working methods of stored-program computers.

The Von Neumann architecture mainly consists of the CPU, memory, and input/output devices. In this architecture, instructions and data need to be accessed from the same storage space and transmitted through the same bus, preventing overlapping execution. The CPU operation in the Von Neumann architecture is divided into five stages: instruction fetch, instruction decode, execute, read memory, and write back.

The Harvard architecture is another major computer architecture system. Compared to Von Neumann processors, the Harvard architecture has two independent memory modules for instructions and data, using two separate buses to connect the CPU and memory modules. In the modified Harvard architecture, instructions and data exist in two independent memory modules but share address and data buses. In modern complex chips, pure Von Neumann or Harvard architectures can be found, while most systems are a fusion or coexistence of both.

Chart: Basic structure of Von Neumann computer architecture

The physical circuit that implements the instruction set architecture is referred to as the processor’s microarchitecture. Thus, colloquially, processor architecture refers to the processor circuit. Typically, companies with independent design capabilities for processor microarchitecture are considered to have processor R&D capabilities. In most cases, the microarchitecture of a processor is physically implemented for a specific instruction set architecture. A small number of processor architectures are designed to implement multiple instruction set architectures for better compatibility.

Although the instruction set architecture can be licensed to multiple companies, the design details of the microarchitecture, which is the physical implementation of the instructions, are kept strictly confidential by each manufacturer. Due to differences in functional requirements, usage scenarios, and design technologies, even processors based on the same instruction set architecture will have different processor architectures.

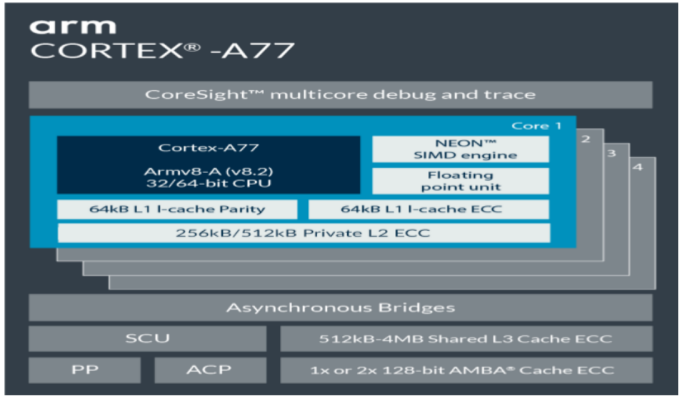

Chart: ARM Cortex-A77 Processor Architecture Diagram

IP Licensing = Selling the “Copyright” of Processor Microarchitecture

In the computer era, major processor manufacturers like Intel and AMD develop processor architectures only for their own processor chips.

As part of the X86 architecture camp that monopolizes personal computers and servers, Intel and AMD continue the model of designing processor cores solely for their own chips. In 2016, AMD collaborated with Chinese server company Haiguang, licensing the Zen architecture to Haiguang, which is essentially the processor microarchitecture. This licensed product is the processor circuit designed by AMD based on the X86 architecture, not the X86 instruction set architecture. Even in this IP licensing collaboration, such cases are rare within the X86 camp.

In the past 20 years, with the rise of smart mobile devices, the IP licensing model of core microarchitecture represented by ARM has emerged. After developing core microarchitectures, ARM sells them as IP, allowing chip manufacturers to design chips based on ARM-licensed cores for use or external sales. The ARM RISC instruction set architecture’s IP licensing offers diverse choices, reliable design, and excellent performance in low-power domains, achieving widespread success in mobile intelligent fields represented by smartphones, tablets, set-top boxes, video surveillance, and other media application chips. ARM has thus become the dominant IP licensor in the mobile internet era.

Chart: Comparison of Advanced Processor Chip Architectures

The refined division of labor in the semiconductor industry has made ARM the king of processor IP licensing. The vertical division of labor in the semiconductor industry has spawned the chip IP industry. Starting in the 1990s, the core of the information industry transitioned from personal computers to mobile phones, and the information era shifted from an internet-centric phase to a mobile internet phase. Smart mobile terminals and smart multimedia products have become increasingly complex and diverse, which has increased the complexity of design due to differentiated demands for chip functions and performance. On the other hand, with the advancement of Moore’s Law, the resources and costs for designing advanced process chips continue to rise.

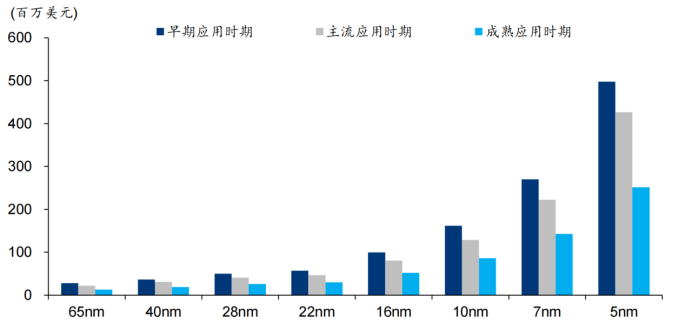

According to a 2020 IBS report, the design cost for a first-generation 5nm process chip is expected to reach $497 million, which is a five-fold increase compared to 16nm; even if 5nm becomes a mature process in the future, the design cost for a single chip will reach $250 million, close to the first-generation chip design cost of 7nm. The global semiconductor industry continues to refine its division of labor under the trend of fabless + foundry + OSAT (fabless design + wafer foundry + packaging testing), further splitting the chip design industry into the chip IP (Intellectual Property) industry.

Chart: Forecast of Design Costs for Different Process Technologies

Semiconductor IP (Intellectual Property) refers to validated, reusable integrated circuit modules with a specific function. IP suppliers focus on developing IP microarchitectures and profit by charging IP architecture licensing fees and royalties. Design companies integrate the licensed IP directly into their chips to achieve functionality, avoiding the need for redevelopment.

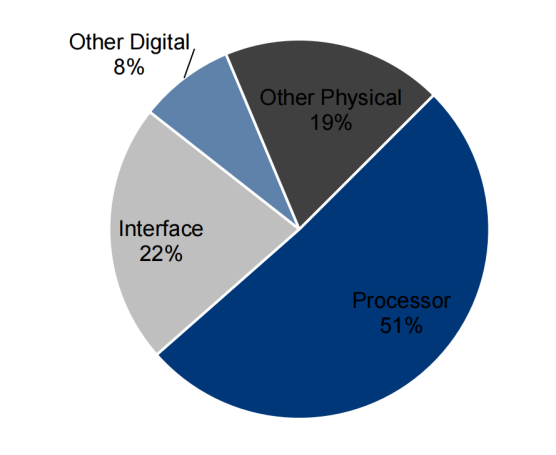

According to Markets and Markets, the semiconductor IP market is expected to reach $6.5 billion by 2024, driven by the continuous advancement of multi-core technology in the consumer electronics sector and the increasing demand in the modern SoC design field. According to the functional breakdown of IP, processor IP occupies the largest share of the IP market. According to IPnest statistics, in 2019, processor IP, including CPU, GPU, NPU, VPU, DSP, and ISP, accounted for 51% of the entire market share.

Chart: 2019 Semiconductor IP Market Share by Function

IP licensing has fostered the thriving ecosystem of the RISC (ARM architecture)

ARM, short for Advanced RISC Machines, is headquartered in Cambridge, UK. Established in November 1990, it is a joint venture of Apple Computer, Acorn Computer Group, and VLSI Technology. ARM does not manufacture chips or sell actual chips to end customers; instead, it licenses its RISC ISA and processor design solutions, allowing partners to produce chips with unique characteristics.

Through its architecture licensing model, ARM has achieved a win-win situation with its partners, rapidly becoming the creator of the global standard for reduced instruction set microprocessors. In July 2016, Japan’s SoftBank announced a £24.3 billion acquisition of ARM, but the company continues to operate independently.

With its monopolistic advantage in the general-purpose processor IP field, ARM remains the top supplier of IP revenue globally. ARM processor cores developed based on the ARM instruction set are widely used in smartphones, televisions, automobiles, smart homes, smart cities, and wearable devices. According to ARM’s market share disclosed at the SoftBank World Conference in 2017, more than 99% of smartphones, over 95% of automotive information devices, and over 90% of wearable devices are equipped with ARM architecture processors.

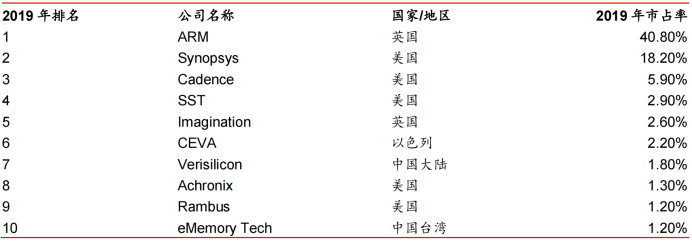

Chart: Top Ten Semiconductor IP Suppliers Worldwide in 2019

ARM licenses the ARM architecture, pioneering the business model in the semiconductor industry

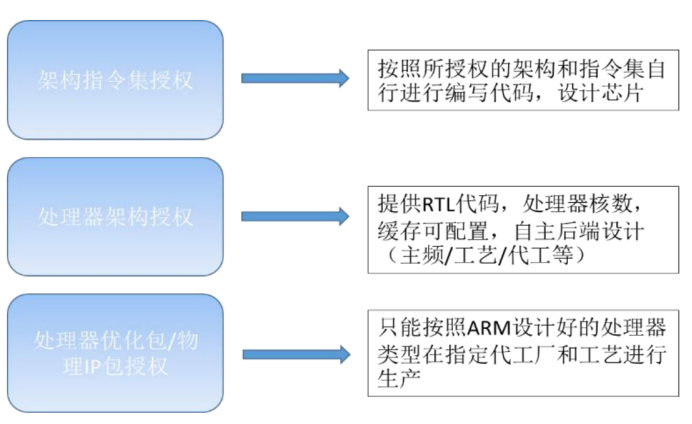

As a semiconductor company, ARM’s unique business model is not to design and manufacture entire chips but to focus on licensing processor core architectures. ARM has consistently maintained a neutral position as an IP supplier for processors. This neutrality has helped ARM widely promote the ecosystem based on its architecture licensing. ARM processor architecture licensing is mainly divided into two levels: one is the ARM instruction set architecture licensing, and the other is the ARM processor architecture licensing.

The company’s revenue sources include: 1) licensing fees from semiconductor companies, which are one-time fees within a certain time frame; 2) royalty fees from semiconductor companies for selling chips to other customers, where ARM receives a certain percentage of royalties for each chip produced; 3) fees for providing technical consulting services to semiconductor companies and users.

Chart: ARM Licensing System

The ARM instruction set architecture licensing allows ARM to grant the ARM RISC reduced instruction set to the assignee. The assignee can make significant modifications to the ARM instruction set, even extending or reducing it. Subsequently, the assignee develops processor architecture based on their modified instruction set, achieving differentiated design of the processor architecture at its source, maintaining control over their self-developed chips, and achieving unique competitiveness while still being compatible with ARM’s comprehensive ecosystem. In this cooperative model, ARM forms a closely-knit technical partnership with its collaborators.

Chart: Comparison of Complex and Reduced Instruction Sets

Apple’s A-series processors are a successful example of self-developed cores based on ARM instruction set architecture licensing. In September 2012, Apple launched the A6 processor SoC with the release of the iPhone 5, marking the beginning of Apple’s self-developed processor core based on the ARM architecture.

In September 2013, Apple was the first to release the A7 processor with a dual-core Cyclone architecture developed based on the ARMv8 architecture. The A7, as the world’s first 64-bit smartphone processor, outperformed the competing Android camp, which was still using 32-bit quad-core solutions. The A-series processor core’s performance advantage over all Android competitors has continued to this day. In 2020, Apple claimed that the newly released A14 Bionic chip’s performance is comparable to that of some laptop processors.

At WWDC 2020, Apple announced that it would transition its Mac computers to use self-developed ARM-based processors. We believe that Apple’s decision to end its 15-year collaboration with Intel and switch to self-developed ARM processors is primarily to further close its hardware and software ecosystem. Apple aims to achieve full autonomy in hardware, creating a differentiated competitive advantage as it did with the success of the iPhone. From ARM’s perspective, if Apple succeeds, it will also help ARM realize its long-held ambition to break the X86 monopoly in the personal computer market.

ARM processor architecture licensing allows ARM to license its self-designed processor core IP to customers. Customers can directly integrate the core RTL (Register Transfer Level) code into the chip design during the frontend design phase. Customers can also configure processor caches, core counts, and frequencies. By connecting with other functional modules, peripheral interfaces, and main memory interface modules through the system bus, a complete chip is generated.

ARM provides a diverse family of processor IP solutions for various application scenarios, covering high-performance computing, high-performance real-time, low-power embedded, cloud computing, hardware security, and high-performance machine learning. ARM’s processor IP licensing model offers reliable processors to partners while reducing chip development costs and promoting innovation in applications. A wide range of partners enriches ARM’s ecosystem, establishing ARM’s dominant position in processor technology for smartphones, IoT, and other fields in the intelligent era.

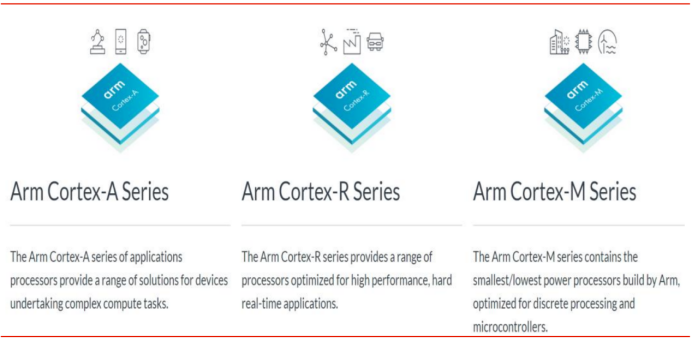

ARM Cortex Series Processors: Cortex-A, Cortex-M, Cortex-R

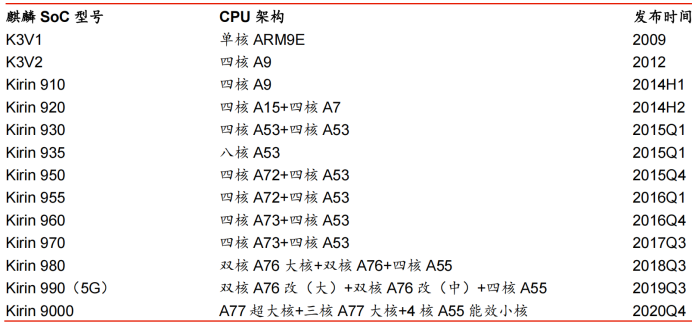

The ARM Cortex series processor cores are the core series occupying the processor IP market within the ARM family. Among them, the Cortex-A series targets high-performance computing needs, running rich operating systems and application tasks, such as smartphones, tablets, set-top boxes, digital TVs, routers, and monitoring SoC chips. The Cortex-A series currently includes the A7x series for performance cores and the A5x series for low-power cores.

Modern multi-core SoCs often integrate a certain number of big cores and small cores to balance peak performance and low power consumption. Big cores handle short bursts of high-performance tasks, while small cores handle low-performance tasks or support background tasks during standby. Currently, except for Apple’s self-developed processor cores, Android smartphone SoC chip design companies led by Qualcomm, HiSilicon, and MediaTek use Cortex-A7x and A5x combinations as core clusters. Among them, Qualcomm and Huawei make different degrees of optimizations in their architectures.

Compared to the Cortex-A processor cores, the Cortex-M processor cores are designed to be smaller in area and have higher energy efficiency. Typically, these processors have short pipelines, simple designs, low maximum clock frequencies, and excellent power performance.

The Cortex-M series has a very broad application prospect in the current intelligent interconnected era, covering smart measurement, human-machine interface devices, automotive and industrial control systems, large household appliances, consumer products, and medical devices. The Cortex-M currently dominates the global 32-bit MCU market. The Cortex-R processor series is a high-performance processor series aimed at real-time applications, operating at relatively high clock frequencies with very low response latencies. It is mainly used in hard disk controllers, automotive transmission systems, and wireless communication baseband control.

Chart: ARM Cortex Series Processor IP

Development of ARM-based Chips in China

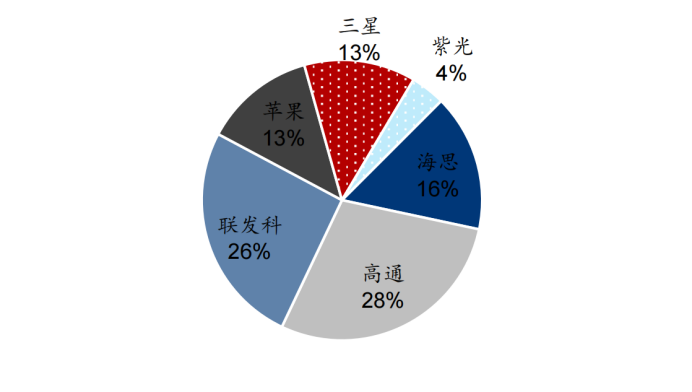

According to the latest data released by CINNO Research, in the first half of 2020, approximately 140 million smartphones were sold in the domestic market, with Huawei (including Honor) achieving a market share of 40.2%. Additionally, a report published by market research firm Counterpoint shows that in Q2 2020, HiSilicon’s Kirin chips accounted for 41% of the domestic smartphone chip market share, becoming the number one in the country.

At the same time, HiSilicon’s Kirin chips have increased their global market share to 16%, surpassing Apple and Samsung. In recent years, Huawei’s smartphones have achieved both quality and quantity, especially its flagship models, which have gained wide recognition in the global market. Excluding the occasional factors of the global pandemic and the consumer trend towards domestic products due to US sanctions, we believe the underlying reason is the enhancement of user experience gained through hardware innovation and the establishment of differentiated competition. The Kirin chips, self-developed by Huawei’s HiSilicon and equipped with ARM processors, are at the core of a series of hardware innovations.

Chart: Global Smartphone Processor Market Share in Q2 2020

The fabless + foundry + OSAT division system in the semiconductor industry has engineered the success of HiSilicon chips, including the Kirin series. Huawei’s continuous substantial investment in HiSilicon has enhanced its chip design capabilities, successfully aligning with the world’s most advanced process and packaging technologies. In the field of chip design, ARM’s processor IP licensing model has become one of the key factors behind the success of the Kirin chips.

The positive impacts of ARM’s licensing model on Kirin chips are as follows: First, in the early stages of development, ARM’s licensing model allowed HiSilicon, as a latecomer, to directly match the performance of processor cores with its Android competitors. Second, ARM’s dominant position in the smartphone sector enabled HiSilicon to leverage ARM’s robust ecosystem, facilitating Huawei’s rapid entry into the mainstream smartphone market. Third, given the characteristics of the consumer electronics market, ARM’s processor licensing effectively shortened the development cycles and costs for companies, including HiSilicon.

Chart: Generations of Huawei HiSilicon Flagship Smartphone Chips

In addition to developing chips based on ARM’s public core architecture, Huawei has also developed the capability to design processor cores based on the ARM instruction set architecture. HiSilicon has officially declared the Kirin 990 as using the “A76 Based” core, indicating that HiSilicon has a deep understanding of ARM’s processor cores and instruction sets, mastering the ability to modify architectures independently.

In January 2019, Huawei further released its self-developed server chip, the Kunpeng 920. This server chip is equipped with 64 HiSilicon self-developed Taishan cores based on the ARMv8 architecture. The overall server performance has improved by 20% compared to existing competitors in the market. In May 2019, Huawei announced that it had obtained permanent licensing for the ARMv8 architecture, emphasizing that HiSilicon has the capability to continuously develop and design processors based on ARM licensed architectures.

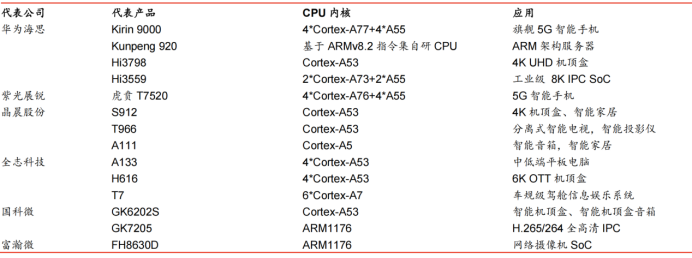

In recent years, domestic smart terminal SoC chips beyond smartphones have gradually achieved domestic substitution, leveraging the Cortex-A series processor IP. Domestic SoCs equipped with ARM architecture processors cover smart HD set-top boxes, IPCs, network cameras, automotive infotainment devices, etc.

According to data from the Glen Research Institute, in 2018, Huawei HiSilicon and Amlogic (688099, unrated) accounted for 60.7% and 32.6% of the domestic IPTV/OTT set-top box chip market, respectively. In 2013, European chip giant STMicroelectronics held over 30% of the domestic set-top box chip market.

In the security field, domestic manufacturers represented by HiSilicon have achieved a full-range layout from low-end substitution to high-end IPC chips.

Chart: Domestic ARM Processor-Based SoC Products

The demand for MCUs in the IoT era is rising, and domestic manufacturers are leveraging ARM Cortex-M to position themselves in the high-end market.

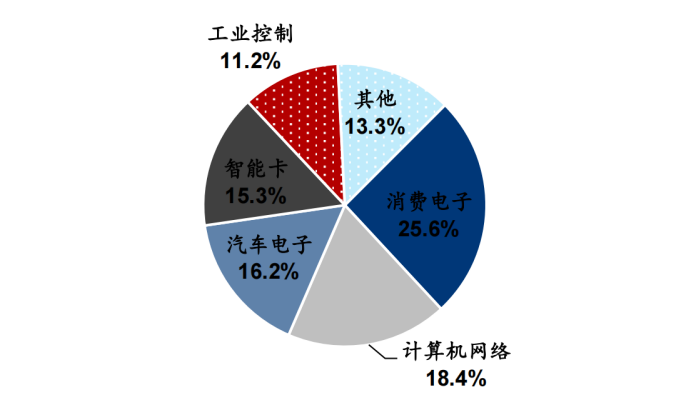

According to IC Insights, global MCU sales reached $16.4 billion in 2019. Products are primarily used in automotive electronics, industrial control/medical, computer networking, and consumer electronics, accounting for 33%, 25%, 23%, and 11% respectively. IC Insights also predicts that after experiencing a decline in 2019 and 2020, MCU sales will show mild recovery in 2021, with a growth of 5% to $15.7 billion, followed by an 8% year-on-year growth in 2022 and an 11% growth in 2023.

By then, MCU revenue is expected to reach a new high of $18.8 billion. The global MCU market is primarily dominated by Renesas Electronics (Japan), NXP Semiconductors (Netherlands), Infineon (Germany), Microchip Technology (USA), Samsung Electronics (South Korea), STMicroelectronics (ST), and Cypress Semiconductor (USA). According to HIS and ASPENCORE data, the scale of China’s MCU market reached 25.6 billion RMB in 2019.

The application market for China’s MCUs is mainly concentrated in household appliances/consumer electronics, computer networking, automotive electronics, smart cards, and industrial control, with market shares of 25.6%, 18.4%, 16.2%, 15.3%, and 11.2% respectively. Benefiting from the growth of the domestic IoT and new energy vehicle industries, China’s MCU market scale has grown at a CAGR of 7.2% from 2008 to 2018, leading globally.

At the same time, HIS predicts that by 2022, China’s MCU market scale will reach 31.9 billion RMB, with growth continuing to surpass the global average. It is expected that in 2020, domestic MCU manufacturers’ sales will reach 14.8 billion RMB, accounting for 55% of the entire Chinese MCU market.

Chart: Composition of China’s MCU Application Market in 2019

ARM Cortex-M processors help domestic manufacturers position themselves in the upstream value chain of the MCU market. Currently, domestic MCU manufacturers have achieved domestic substitution in mid to low-end application fields such as consumer electronics, smart cards, and water, electricity, and gas meters. As the demand for IoT terminals advances, the complexity of tasks in the IoT era will require MCUs to move towards 16 or 32-bit designs. The 32-bit MCU is the market development direction based on the future IoT.

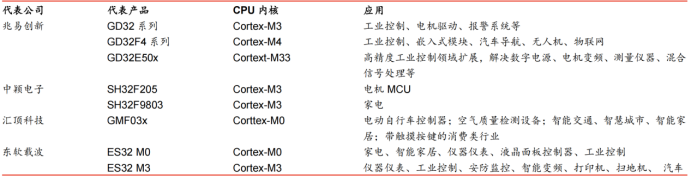

With the goal of meeting the above demands and having abundant ecosystem resources, ARM Cortex-M series processor cores have become the dominant cores in the 32-bit MCU market. Domestic MCU manufacturers like GigaDevice and Zhongying Electronics are actively laying out the domestic mid-to-high-end market using 32-bit MCUs based on the ARM Cortex-M series processors, positioning themselves upstream in the industry value chain. Domestic 32-bit MCUs have begun to enter the high-end MCU market traditionally dominated by foreign manufacturers.

As a leading domestic IC design enterprise, GigaDevice primarily provides 32-bit general-purpose MCUs based on the ARM Cortex-M series, with its GD32 series being the mainstream 32-bit general-purpose MCU product in China, widely used in industrial automation, human-machine interaction, motor control, security home appliances, smart home appliances, and IoT.

According to the company’s 2020 mid-term report, GigaDevice’s MCU products include over 330 product models, 23 product series, and 11 different packaging types, with cumulative shipments exceeding 400 million units. In July 2020, GigaDevice launched the GD32E5 series high-performance microcontrollers based on the new Arm Cortex-M33 core, focusing on product routes in wireless connectivity, battery-powered devices, portable and wearable devices, and automotive-grade MCUs.

Chart: Some Domestic 32-bit MCU Suppliers and Representative Products

RISC-V Open Source Model Gives Domestic Processors a Chance to Overtake

RISC-V is an emerging reduced instruction set architecture that has attracted attention due to its open-source model.

In 2011, the emergence of the open-source architecture RISC-V attracted global attention in the processor industry, academia, and research. RISC-V is a simple, open, and free new reduced instruction set architecture, characterized by its openness. Its openness allows it to be freely used for any purpose, permitting anyone to design, manufacture, and sell chips or software based on RISC-V. This level of openness is unprecedented in the processor field.

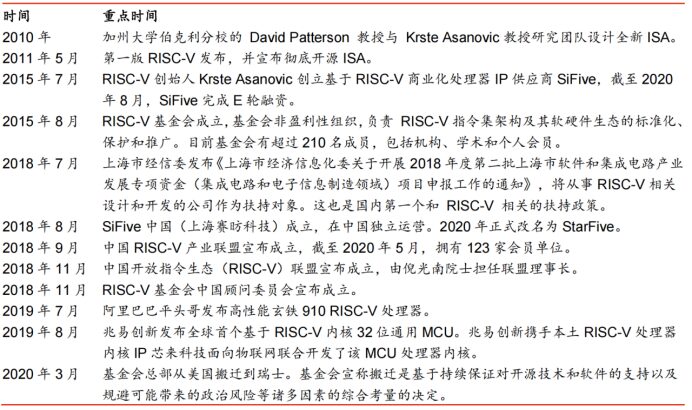

RISC-V originated from a project initiated by Professor David Patterson and Professor Krste Asanovic at the University of California, Berkeley, in 2010. The project needed to select a processor instruction set. Given the increasing complexity and intellectual property issues with existing instruction sets like ARM, MIPS, SPARC, and X86, they began to redesign a new instruction set.

The Berkeley team decided to make the RISC-V instruction set completely open when it was released, using the BSD License to design the open-source processor core, Rocket Core. The Berkeley research team believed that the instruction set, as a specification for the interface between hardware and software, should not require paid licensing for use, unlike ARM, PowerPC, and X86, but should be open and free.

The RISC-V Foundation was established in 2015 by relevant companies in Silicon Valley, and the commercialization of RISC-V entered the fast lane. The foundation, as a non-profit organization, is responsible for the standardization, protection, and promotion of the RISC-V instruction set architecture and its software and hardware ecosystem. The board of the RISC-V Foundation consists of representatives from Bluespec, Google, Microsemi, NVIDIA, NXP Semiconductors, the University of California, Berkeley, and Western Digital.

According to the RISC-V Foundation, over 210 institutions, academia, and individuals from 25 countries have joined. Chinese enterprises and research institutions are actively participating in the foundation, with Alibaba, Huawei, ZTE, and SiFive being top members.

Chart: Summary of Major Events in RISC-V

Due to long-term development, X86 and ARM have formed a strong ecosystem, making it difficult for RISC-V to replace X86 and ARM in the computer and mobile internet fields in the short term. However, in the emerging AIoT era, RISC-V will face opportunities. The CPU architectures, including ARM, have become extremely complex and cumbersome after decades of development and evolution. Even the ARM architecture, as a reduced instruction set, has documentation spanning thousands of pages. The number of instructions has become increasingly complex, with many versions that are neither compatible nor support modularization.

Furthermore, existing mainstream instruction sets face high patent and architectural licensing issues. As a fully open-source architecture from the outset, RISC-V avoids the pitfalls of decades of development in computer systems. The architecture documentation is only a couple of hundred pages, with basic instruction counts of just over 40. Modularization allows users to customize their needs freely, configuring different subsets of instructions.

Simplification and flexibility give the emerging RISC-V architecture an opportunity to break into the smart IoT market. The low-latency, high-capacity trillion-device interconnectivity brought by the AIoT era, with rich scenarios, interconnectivity, and intelligence, will create new chip market demands. However, the diverse applications have also led to fragmentation and diversity in the AIoT market, with extremely varied demands for CPUs. Existing processor designs cannot effectively respond.

The extreme simplification and flexible architecture of the RISC-V architecture, along with its modular characteristics, allow for flexible modification of instruction sets and chip architecture designs for different applications. In contrast, using ARM often means adhering to standardized designs, making differentiation difficult. Additionally, many smart devices are cost-sensitive, making RISC-V’s free licensing features particularly important for chip manufacturers.

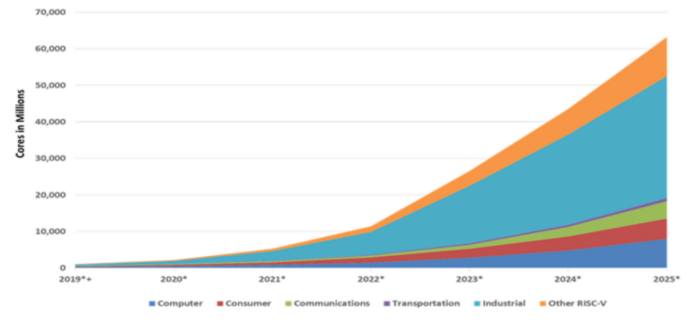

Market research firm Semico Research reports that by 2025, the number of chips using RISC-V architecture is expected to reach 62.4 billion. In various sub-markets, including computing, consumer, communications, transportation, and industrial markets, the compound annual growth rate from 2018 to 2025 is as high as 146%.

The Semico Research and RISC-V Foundation have identified 34 sub-markets and studied the total available market for CPU IP cores and the serviceable available market for RISC-V IP cores in each market, ultimately predicting data for 2025. The study identifies four high-value opportunities for the use of RISC-V cores: high-performance multi-core SoCs, cost-effective multi-core SoCs, basic SoCs, and FPGAs.

Chart: Expected Composition of RISC-V Core Demand

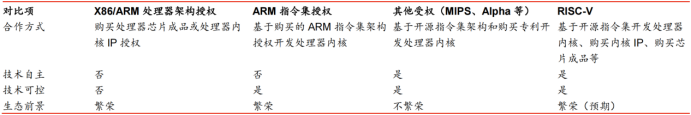

Openness and collaboration give RISC-V the potential to become the choice of instruction set architecture for autonomous and controllable processors in China. The open-source model of RISC-V architecture allows it to avoid being controlled by a few companies like X86 and ARM, achieving autonomy and control at the source of the architecture.

The broad application prospects and future potential market size have attracted global renowned companies, research institutions, and universities to actively cooperate. Multi-party investment and collaboration are expected to promote the maturity of the RISC-V industry chain and the improvement of its ecosystem. A prosperous ecosystem is conducive to the continuous profitability of participating enterprises, enhancing their willingness to invest further, and entering a virtuous development cycle. Optimistic market expectations, a mature industry chain, and a complete development ecosystem are essential conditions for RISC-V to become a mainstream instruction set architecture, potentially becoming the third pole of instruction set architectures after X86 and ARM.

Chart: Comparison of RISC-V and Other Architecture Licensing Models

Comprehensive layout of instruction set architecture optimization, processor core development, and terminal chip design is an objective requirement for achieving autonomous and controllable processors. RISC-V emphasizes a fully open design, allowing users to freely add proprietary instruction sets and choose whether to keep the architecture open or close it. Therefore, even though the instruction set architecture is open and free, the patents and microarchitecture derived from the instruction set are not open and free. Currently, RISC-V instruction set and microarchitecture have developed three knowledge property rights models: open and free, licensed, and closed.

Currently, companies for RISC-V core IP licensing, similar to ARM’s business model, have emerged. SiFive, founded by RISC-V founder Krste Asanovic, is the world’s largest commercial processor IP licensing company based on RISC-V. SiFive has completed its E-round financing, with shareholders including not only professional VCs but also semiconductor giants like Qualcomm, Western Digital, and SK Hynix.

SiFive’s products cover MCU, edge computing, artificial intelligence, IoT, memory, AR/VR, machine learning, and other fields. Taiwan’s Andes Technology is another well-known RISC-V core IP provider. In October 2020, Renesas Electronics announced that it would begin using Andes’ AndesCore IP 32-bit RISC-V CPU core to develop new standard products for specific applications.

Learning from the US-China trade friction, the Android-style open-source trap must be avoided: Google uses the open-source and free framework of Android to attract smartphone manufacturers to use Android, then makes GMS (Google Mobile Service) closed-source and turns it into a licensing model, making it a profitable model. When the US imposed sanctions on Huawei by placing it on the “Entity List,” Google unhesitatingly stopped GMS licensing, leaving Huawei smartphones unable to download, update, or use widely popular applications like Gmail, YouTube, Google Maps, etc., putting them at a disadvantage in overseas markets.

From the history of processor development, the success of an instruction architecture lies not only in successful chip design but also in a complete software and hardware ecosystem.

The x86 architecture, promoted by Intel, dominates a vast market, with processors based on the x86 architecture being used in traditional PCs and data center-scale servers, alongside applications and services that have been optimized for over 40 years.

ARM’s IP licensing model has become increasingly refined, giving rise to a massive market application scale for mobile and smart devices. Coupled with support from EDA companies, wafer foundries, and software companies within the ARM ecosystem, despite the high licensing fees, major chip manufacturers are still willing to cooperate.

Currently, the RISC-V ecosystem is just beginning to take shape, with operating systems, compilers, development tools, and EDA tools gradually improving. Promoting the deep development of the ecosystem is conducive to attracting more enterprises to use the RISC-V architecture, making RISC-V a mainstream architecture.

The fragmentation of the AIoT market and the inherent open and flexible characteristics of the RISC-V architecture necessitate both domestic and international cooperation to promote the standardization of the RISC-V architecture. Maintaining RISC-V’s openness and collaboration is more conducive to its healthy development, allowing Chinese enterprises to enhance their technological capabilities and assert their influence in the processor field; actively promoting cooperation among domestic ecosystem enterprises to effectively integrate resources, forming a complete industrial chain that connects autonomous and controllable processors with a rich array of smart IoT applications.

AIoT Explosion Imminent, Domestic Efforts to Promote RISC-V Development

Policies are being introduced to promote industrial development

Shanghai was the first in the country to introduce support policies related to RISC-V. In July 2018, the Shanghai Municipal Economic and Information Commission issued a notice regarding the application for the second batch of special funds for the development of the software and integrated circuit industry in 2018, targeting companies engaged in RISC-V-related design and development for support. In October 2018, the Esp32-Marlin IoT chip project from Espressif was selected as a supported project. In February 2020, the Guangdong Provincial Government Office’s document on accelerating the development of the semiconductor and integrated circuit industry explicitly listed RISC-V (open-source instruction set architecture based on reduced instruction set principles) chip design as a key development direction.

Industry, academia, and research are all taking the stage, actively engaging in domestic and international cooperation

In addition to participating in the RISC-V Foundation, Chinese enterprises and research institutions are also engaging in various forms of cooperative participation through technical sharing platforms, forums, and industry alliances. On October 17, 2018, the China RISC-V Industry Alliance was established, initiated by key enterprises, research institutions, and industry associations in the RISC-V field. The alliance adheres to the principles of openness, cooperation, equality, and mutual benefit, aiming to address key issues faced by the Chinese RISC-V field, establishing a domestically produced, controllable, and secure RISC-V heterogeneous computing platform, and promoting a complete RISC-V industry ecosystem that spans IP cores, chips, software, systems, and applications.

On November 8, 2018, the China Open Instruction Ecology (RISC-V) Alliance was announced at the fifth World Internet Conference in Wuzhen, with Academician Ni Guangnan serving as the chairman. The CRVA aims to gather enterprises and institutions involved in RISC-V instruction set, architecture, chips, software, and complete machine applications across the industry chain to voluntarily form a national, comprehensive, united, and non-profit social organization. This alliance will integrate various resources around the RISC-V instruction set, seeking to promote the rapid development of the RISC-V ecosystem in China through deep integration of production, academia, research, and application. On the same day, at the World Internet of Things Conference, the RISC-V Foundation announced the establishment of a China Advisory Committee to provide guidance on the education and application promotion strategy of the RISC-V Foundation.

In 2019, a new non-profit global organization, the OpenHW Group, was established to create a focal point for ecosystem development and promote the adoption of open-source processors, providing open-source RISC-V architecture-based Core-V IP for processor cores. Leading domestic and foreign enterprises and institutions, including Alibaba, Huawei, NXP, NVIDIA, Silicon Labs, and ETH Zurich, have become members of the OpenHW Group.

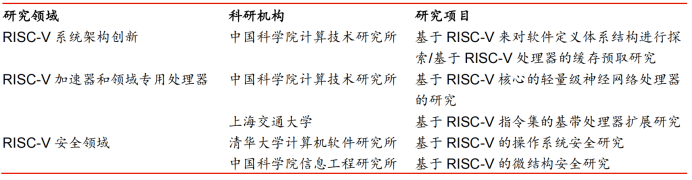

Research institutions are making strides in various fields

Leveraging domestic universities and research institutions, research based on the RISC-V architecture is unfolding in multiple fields. Prior to 2015, most microarchitecture and chip-related research was hindered by licensing issues related to instruction sets. With the popularity of the RISC-V open-source concept, an increasing number of research projects have benefited from RISC-V and have been able to proceed.

According to incomplete statistics from the China Open Instruction Ecology (RISC-V) Alliance, as of February 2019, the research institutions involved in scientific research or ecosystem surveys related to RISC-V include but are not limited to: Peking University, Nanjing University, Nankai University, Ningbo Institute of Industrial Technology, Pengcheng Laboratory, Tsinghua University, Shanghai Jiao Tong University, Shanghai University of Science and Technology, Tianjin University, Zhejiang University, China Electronics Technology Group Corporation, University of Science and Technology of China, Institute of Computing Technology of the Chinese Academy of Sciences, Shanghai Institute of Microsystem and Information Technology, Institute of Microelectronics of the Chinese Academy of Sciences, and Institute of Information Engineering of the Chinese Academy of Sciences. It is expected that research based on RISC-V will continue to flourish in China.

Chart: Some Domestic Research Institutions Based on RISC-V Research Projects

According to statistics from the China Open Instruction Ecology (RISC-V) Alliance, as of the end of 2018, nearly 100 Chinese companies (including foreign companies’ China branches) related to RISC-V chips, hardware, software, investment, intellectual property, and ecosystems can be identified.

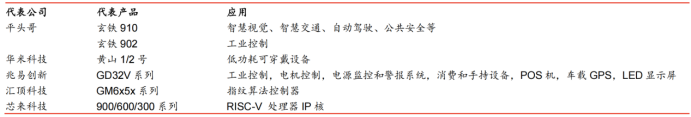

In recent years, domestic RISC-V commercial products have been continuously launched, with many highlights. Alibaba’s T-head Semiconductor launched the Xuantie 910 AI vector acceleration engine, a 64-bit 16-core processor that outperforms the ARM Cortex-A73 in performance; the Xuantie 902/903 has been applied in IoT and industrial control MCUs.

In September 2018, Huami Technology (HMI.US) officially released the “Huangshan 1”, becoming the first AI chip in the global wearable field. As a follow-up product, the Huangshan 2 RISC-V intelligent wearable chip is set to go into mass production in Q4 2020. Huami claims that Huangshan 2’s overall computing efficiency has improved by 38% compared to the commonly used ARM Cortex-M4 architecture processors in wearable devices.

Domestic examples of collaboration between local RISC-V processor IP core suppliers and local design companies have emerged. On August 22, 2019, GigaDevice launched the world’s first MCU based on the RISC-V core, the GD32VF103 series. This MCU, using the Bumblebee processor core, was jointly developed by GigaDevice and RISC-V processor core IP and solutions provider Chipone Technology (unlisted) for the IoT market. This cooperation marks a significant collaboration between local processor IP suppliers and domestic chip design companies.

Chart: Some Domestic Design Enterprises and Their RISC-V Architecture-Based Chip Products

*Statement:This article is organized from the internet, and the copyright belongs to the original author. If the source information is incorrect or infringes rights, please contact us for deletion or authorization matters.