The Core Concepts of Real-Time Scheduling (RTS) in Semiconductor Manufacturing

The Necessity of Advanced Scheduling

Semiconductor manufacturing is one of the most complex and capital-intensive industries globally. Its production process involves hundreds or even thousands of steps, characterized by significant re-entrant flow, where wafers need to return multiple times to the same equipment group for processing at different levels. The entire production cycle typically lasts from 30 to 90 days or even longer, and the process is filled with various sources of variability, such as equipment failures, process fluctuations, and changes in demand. In such a highly complex, high-cost, and long-cycle environment, efficient production scheduling is crucial for improving capacity utilization, shortening cycle time (CT), reducing work-in-process (WIP) levels, meeting customer delivery dates, and controlling production costs. Traditional scheduling methods based on simple rules or manual experience have struggled to meet the challenges of modern wafer fabs and cannot achieve global optimization. Therefore, advanced real-time scheduling (RTS) systems have emerged, aiming to achieve smarter and more efficient production control through an integrated approach and scientific theories.

Theoretical Foundations

The described RTS solution is not built from scratch but is based on mature operational management theories, integrating these theories into the specific scenarios of semiconductor manufacturing.

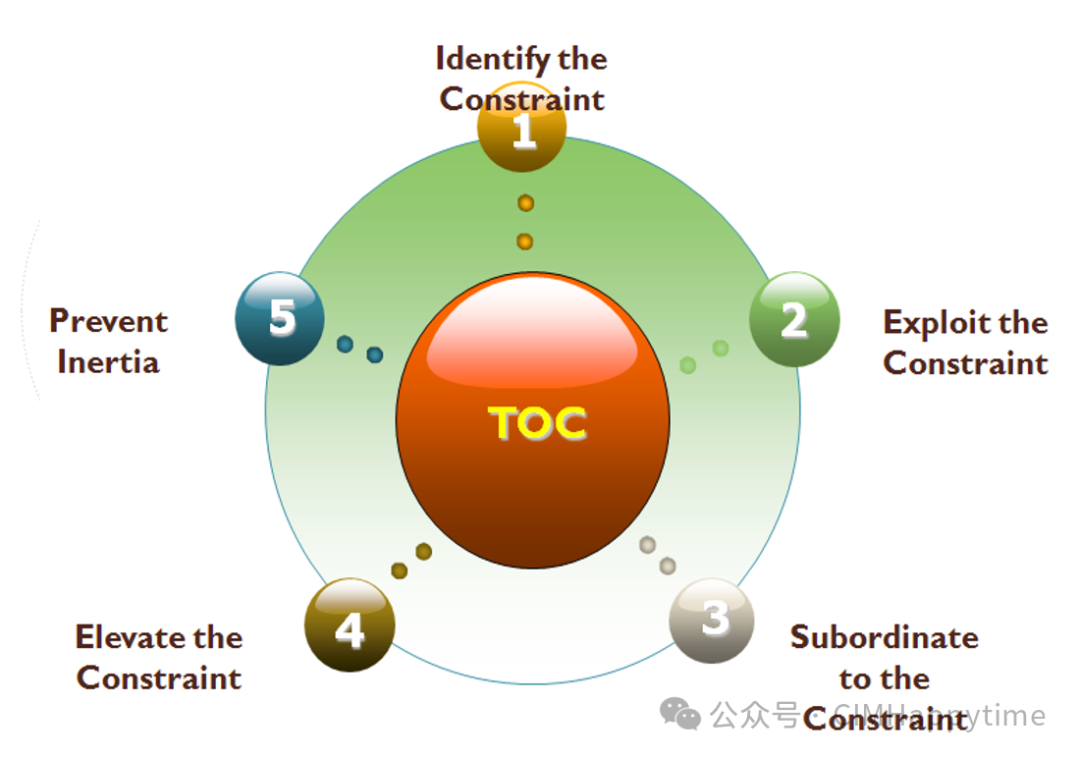

Theory of Constraints (TOC)

TOC is a management philosophy that posits that the overall performance of any complex system (such as a wafer fab) is limited by a few (or even one) constraints or bottlenecks. TOC emphasizes that to enhance the output of the entire system, these bottlenecks must first be identified and effectively managed. It views the manufacturing system as a chain, with its strength determined by the weakest link.

In the RTS solution, the application of TOC is reflected in the identification and focused management of bottleneck machines. The system does not pursue balanced utilization rates for all equipment but intentionally allows bottleneck equipment to operate close to full capacity while ensuring that non-bottleneck resources comply with the demands of the bottleneck, providing support to avoid starvation or blockage. TOC’s five focusing steps (Identify, Exploit, Subordinate, Elevate, Repeat) provide a methodological framework for the continuous optimization of bottleneck management in the RTS system, allowing for ongoing attention and improvement of the true constraints even as system states change dynamically. Although the user queries do not explicitly mention the “Drum-Buffer-Rope (DBR)” implementation method of TOC, the mechanisms in the RTS solution, such as bottleneck determining the drum, setting buffers, and controlling production based on standard WIP levels, are essentially highly consistent with the principles of DBR.

Little’s Law

Little’s Law is a fundamental theorem in queueing theory that reveals the relationship among average work-in-process (WIP), average throughput (TH), and average cycle time (CT) in a stable system: WIP = TH × CT (or L = λW).

This law provides the foundation for understanding and managing the macro dynamics of production lines in the RTS system. It clearly states that, at a given output rate, WIP levels and cycle times are directly proportional. Therefore, the RTS system directly influences and manages cycle times by controlling WIP levels (for example, through the “standard WIP level” mechanism). The flow timetable (Step’s WT+RPT) is used to track the progress of batches relative to their target cycle times in real-time, which is a manifestation of Little’s Law in dynamic monitoring and adjustment—judging whether a batch is ahead or behind by comparing the current state with the target CT. This law is also used to assess the impact of inventory levels on delivery times.

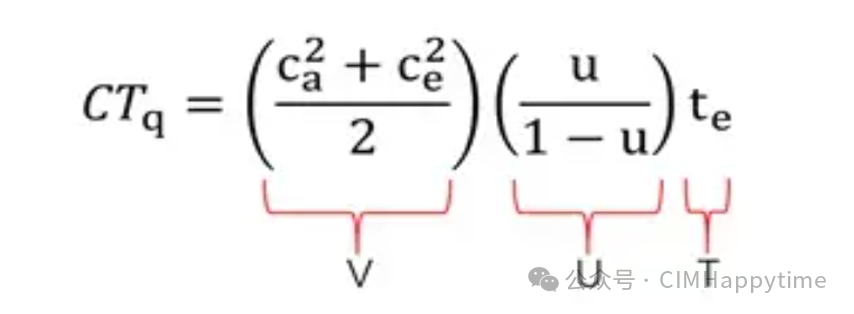

Kingman’s Formula (VUT Equation)

The VUT equation, also known as Kingman’s formula, is an important approximation in factory physics used to describe the average queue time (Cycle Time in Queue) of a single workstation in relation to its variability (V), utilization (U), and average effective processing time (T): .

The VUT equation profoundly explains why bottleneck management and variability control are so critical in RTS. It indicates that queue times and overall cycle times do not increase linearly with utilization but exhibit exponential growth in high utilization areas, with the severity of this growth depending on the system’s variability. The higher the variability (V), the more pronounced the amplification effect of high utilization (U) on queue times. This directly supports the key strategy in the RTS solution: reserving small buffer capacities (e.g., 5-10%) at bottleneck machines (which typically have high utilization) while reserving larger buffer capacities (e.g., 30%) at non-bottleneck machines. This approach aims to reduce the actual utilization of bottleneck machines, thereby significantly lowering their sensitivity to inherent variability and ensuring output stability and predictability. The VUT equation reveals the inherent trade-offs between time buffers (queue time), capacity buffers (idle capacity), and inventory buffers (WIP), guiding the RTS system on how to achieve desired cycle time performance by adjusting utilization and WIP levels in the presence of variability.

These three theories (TOC, Little’s Law, VUT equation) are not applied in isolation within the RTS solution but form an interrelated and mutually supportive theoretical framework. TOC indicates the focus of optimization (bottlenecks); Little’s Law describes the macro balance relationship among WIP, CT, and TH; while the VUT equation explains how variability and utilization drive queue times (a major component of CT) and the micro dynamics of WIP at the workstation level. The RTS system achieves system-level optimization by identifying bottlenecks (TOC), utilizing VUT principles to formulate buffer strategies to protect bottlenecks from variability shocks, and managing overall flow and cycle times by controlling WIP (Little’s Law).

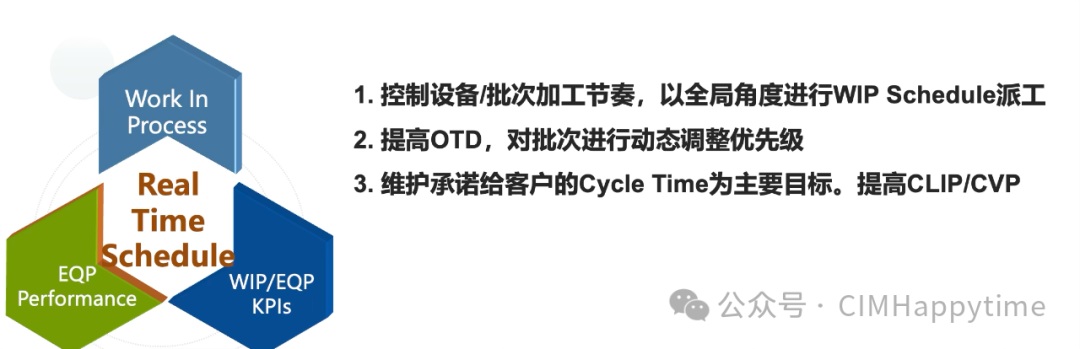

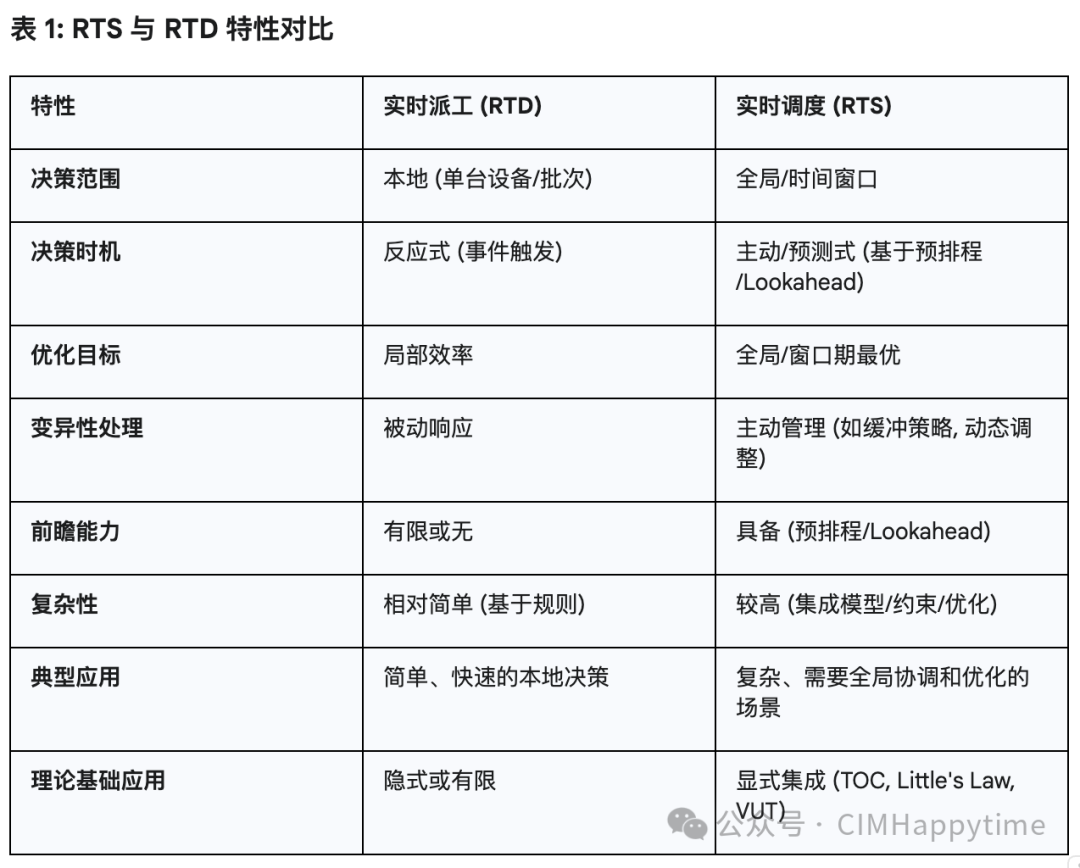

Comparison of RTS and Traditional Real-Time Dispatching (RTD)

Real-time scheduling (RTS) and real-time dispatching (RTD) are two related but distinct concepts in semiconductor manufacturing shop floor control.

Traditional RTD typically focuses on local and immediate decision-making. Its core functions often revolve around answering two fundamental questions: “What’s next?” (When a piece of equipment is idle, which batch should be processed?) and “Where’s next?” (When a batch has completed processing, where should it be sent next?). RTD decisions are usually based on the current state of equipment and WIP, employing relatively simple dispatching rules (Dispatching Rules) such as first-in-first-out (FIFO), earliest due date (EDD), and critical ratio (CR). Although RTD responds quickly (usually in seconds), its limitation lies in its narrow perspective and lack of foresight (Look-ahead). It may lead to local optimization and struggle to effectively address global disturbances or coordinate complex interdependencies across areas.

In contrast, RTS adopts a broader perspective and a more proactive approach. It is not merely reactive to current events but possesses a certain degree of pre-scheduling or foresight capability, planning within a defined time window (Time Horizon). The goal of RTS is to seek a global (or near-global) optimal solution within this time window, considering various constraints across the entire production line or critical production segments, such as bottleneck status, Q-Time limitations, batch due dates, and cross-area interactions. It is no longer limited to simple rule selection but may employ more complex models, composite rules, or even optimization algorithms for decision-making.

RTS is not merely a replacement for RTD; it can be seen as an evolution in the automation and intelligence development of semiconductor manufacturing. As wafer fabs expand in scale (e.g., Giga-fab), process complexity increases (more process steps, re-entrant flows, stricter process windows like Q-Time), and market competition demands higher efficiency and delivery times, simple, localized RTD is no longer sufficient to effectively manage production operations. RTS attempts to overcome the limitations of RTD by introducing a broader perspective, stronger predictive capabilities, deep integration of factory physics principles, and explicit handling of complex constraints, aiming for higher levels of system-level optimization and control.

Key Mechanisms of the Described RTS Solution

The RTS solution manages the complex semiconductor production process through a series of carefully designed mechanisms, aiming to maximize efficiency and meet delivery dates.

Bottleneck Management Strategy

Following the principles of TOC, bottleneck management is at the core of the RTS solution. Bottlenecks determine the final output of the entire factory. To ensure that bottleneck resources are fully utilized and do not become an excessive constraint on system performance, RTS employs the following strategies:

- Reserved Buffer Capacity: Based on the principle revealed by the VUT equation—that high utilization dramatically amplifies the impact of variability on queue times—RTS intentionally reserves a portion of capacity (typically 5-10%) at bottleneck machines, while reserving more buffer capacity (e.g., 30%) at non-bottleneck machines. This differentiated buffer setting reflects TOC’s principles of “Exploitation” and “Subordination.” Reserving a small buffer for bottleneck machines is intended to absorb normal fluctuations in production (such as short downtimes, uneven arrival times) without sacrificing too much theoretical capacity, preventing a dramatic increase in queue times and output instability due to the pursuit of extreme utilization. The large buffer at non-bottleneck machines (30%) is not aimed at maximizing their own output but ensuring they have sufficient capacity to cope with their own variability (such as maintenance, failures) and fluctuations in upstream material supply, thereby stably supplying bottleneck resources and preventing bottlenecks from halting due to material shortages. This strategy helps reduce overall system variability and maintain line balance. Determining the optimal buffer size is a complex issue that requires balancing buffer costs with system performance (such as throughput, cycle time). Under certain specific conditions (such as low variability or high concurrency), smaller buffers may also be sufficient.

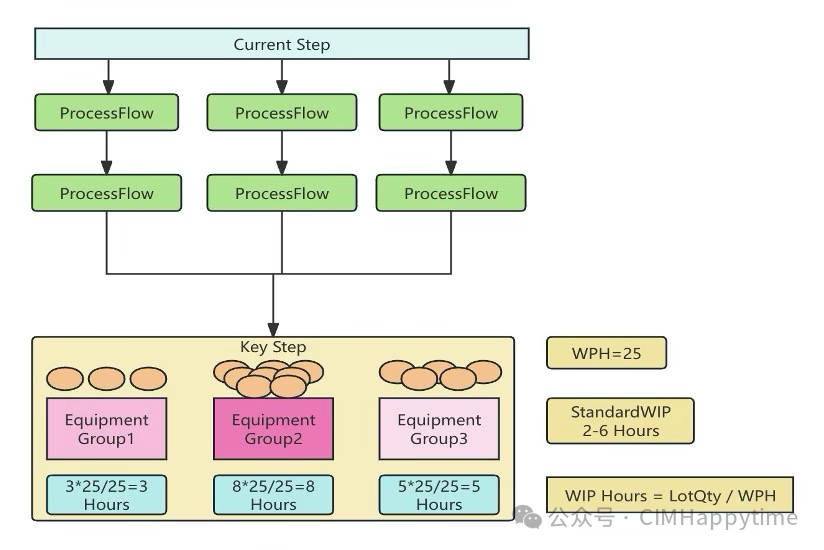

- Standard WIP Level: The RTS system dynamically adjusts the production or processing quantities at upstream stations based on the preset standard WIP levels for bottleneck areas. This is similar to the “rope” mechanism in DBR systems, aiming to precisely control the number of WIP entering the bottleneck area, ensuring that bottleneck machines always have sufficient batches to process (avoiding starvation) while preventing excessive WIP accumulation that could overload the bottleneck and extend queue times. This directly applies Little’s Law (controlling WIP to manage CT) and VUT principles (avoiding high WIP leading to queue explosions under high utilization). By maintaining WIP in the bottleneck area at a reasonable and stable level, it helps achieve smooth flow and balance in the production line. Determining the optimal WIP level may require the use of saturation curves and other analytical tools to find the best balance point between WIP, output, and cycle time. Related concepts include the CONWIP (Constant WIP) production control strategy, which maintains a constant total WIP across the entire production line or specific areas.

Dynamic Batch Priority Adjustment Based on Flow Timetable and Due Dates

To ensure that batches can be completed on time and meet final due dates, the RTS system employs a dynamic priority adjustment mechanism based on the flow timetable.

-

<span>Flow Timetable:</span>This is a time benchmark for batches to pass through the remaining process steps in an ideal or target state, calculated as the sum of waiting time (WT) and run process time (RPT) for the remaining steps. This timetable sets a dynamic time target for each batch at every stage in the process. DPML (Days Per Mask Layer) is a commonly used metric in the semiconductor industry to measure cycle time progress, which can be used to standardize the progress of different products or layers for comparison and tracking. -

<span>Dynamic Adjustment Logic:</span>The system compares the actual position of the batch (which steps have been completed and how much time has been spent) with its flow timetable in real-time.

- If the batch progress is behind the timetable, the system will elevate its priority in an attempt to accelerate its subsequent processes.

- If the batch progress is ahead of the timetable, the system may lower its priority at discretion to make way for other more urgent batches.

- This continuous feedback and adjustment mechanism aims to proactively guide all batches toward their target cycle times (CT), ultimately meeting customer delivery requirements.

<span>Priority Type Distinction:</span>

- Key Priority: This high priority may be assigned to batches critical to factory goals, such as batches close to Q-Time limits, customer urgent “hot lots,” high-value product batches, or key batches defined by specific business rules. Their priority calculation in the timetable may differ from ordinary batches, potentially receiving greater priority boosts or more favorable resource allocation.

- Normal Priority: Assigned to standard priority levels for regular production batches.

<span><span>Relationship with Traditional Rules:</span></span>This timetable-based dynamic adjustment logic is more complex and refined than traditional static priority rules (such as fixed priority FIFO) or rules based solely on a single attribute (such as EDD or CR). It utilizes more detailed process information (WT and RPT) and real-time progress feedback. However, its core idea shares commonalities with CR and other rules based on remaining time and available time, all attempting to assess the urgency of batches. Modern scheduling systems often employ composite rules, combining multiple factors (such as waiting time, processing time, due dates, downstream queue conditions, etc.) to calculate comprehensive priorities.

The flow timetable here is not merely a tracking tool; it plays the role of an active control mechanism. By comparing the real-time progress of batches with this dynamic benchmark, the RTS system can continuously identify and correct deviations. The inherent variability in semiconductor manufacturing inevitably leads to batches deviating from the planned schedule. Static priority rules may not respond quickly or effectively to this. In contrast, the dynamic priority adjustment based on the timetable provides a more refined control means, attempting to proactively offset the negative effects of variability by adjusting priorities in real-time, striving to bring batches back on track and ensure the achievement of overall cycle times and final due dates. This is more adaptive and forward-looking than traditional CR or EDD rules.

Q-Time Management (Q-Time Ratio)

Q-Time (also known as Queue Time constraint, Qualification Time, or allowable dwell time) is a strict process constraint unique to semiconductor manufacturing, referring to the maximum allowable interval between two (or more) consecutive process steps. Exceeding this time limit may lead to oxidation, contamination, or other chemical changes on the wafer surface, resulting in yield loss or even batch scrapping or rework. Q-Time management is crucial for ensuring product quality and reducing losses, especially at advanced process nodes.

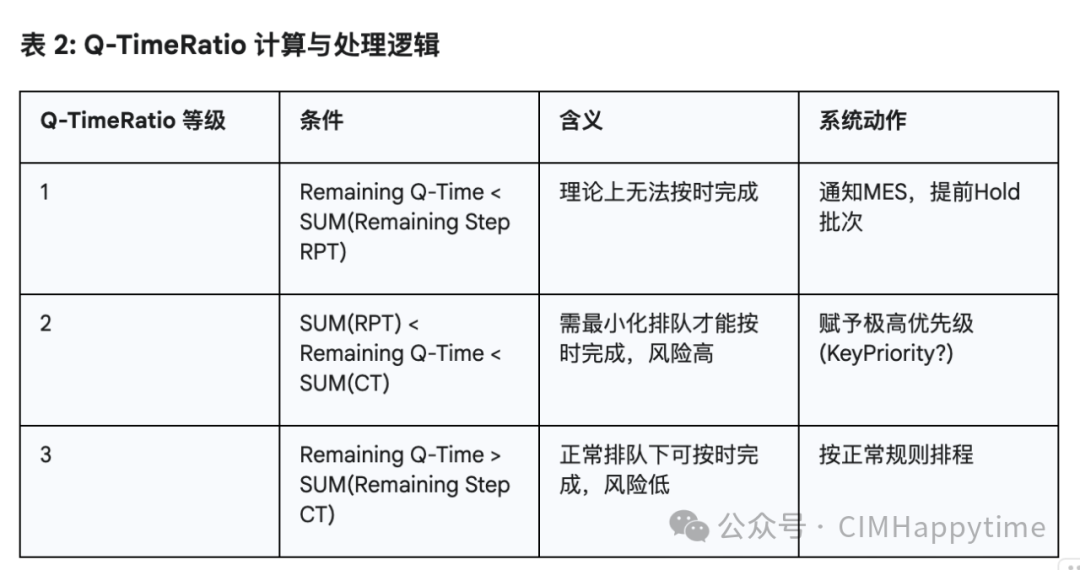

The RTS system manages these time-sensitive batches by calculating the Q-Time Ratio:

- Q-Time Ratio Calculation: This ratio compares the remaining Q-Time window for the batch with the time required to complete the necessary subsequent steps.

- Remaining Q-Time: = Maximum allowable Q-Time – Time consumed within the Q-Time window.

- Remaining Step Total RPT: The shortest theoretical processing time required to complete all subsequent related steps (not considering any queue waiting).

- Remaining Step Total CT: The expected time to complete all subsequent related steps (including average queue waiting time).

- Processing Logic: The system categorizes batches into three levels based on the Q-Time Ratio and takes corresponding actions:

-

Level 1 (Urgent/Hold): When Remaining Q-Time < SUM(Remaining Step RPT). This means that even if all subsequent steps have no queue waiting, processing cannot be completed within the remaining Q-Time window. At this point, the system proactively notifies the MES (Manufacturing Execution System) to hold the batch in advance to avoid wasting processing resources on batches that are destined to violate Q-Time constraints.

-

Level 2 (High Priority): When SUM(Remaining Step RPT) < Remaining Q-Time < SUM(Remaining Step CT). This means that under zero queue or very short queue conditions, the batch may complete within the Q-Time window. However, if following the expected normal queue time, it may exceed the limit. Therefore, these batches are assigned very high priority (possibly elevated to Key Priority) to ensure they can quickly pass through subsequent steps, minimizing queue time.

-

Level 3 (Normal): When Remaining Q-Time > SUM(Remaining Step CT). This means that even under normal expected queue times, the batch has sufficient time to complete within the Q-Time window. Therefore, these batches can be scheduled according to normal scheduling rules.

Due to its direct impact on yield, Q-Time constraints typically hold very high priority in scheduling decisions, even surpassing pure efficiency or delivery time goals. Effective Q-Time management requires precise time tracking capabilities and a certain level of predictive scheduling ability. This clear, risk assessment-based Q-Time Ratio processing logic fully reflects how process quality constraints profoundly influence or even dominate scheduling decisions in semiconductor scheduling. To avoid potential yield losses (whose costs may far exceed processing costs), the system may take drastic measures such as holding batches (Level 1) or breaking conventional priorities (Level 2), indicating that ensuring process windows takes precedence over maintaining smooth logistics.

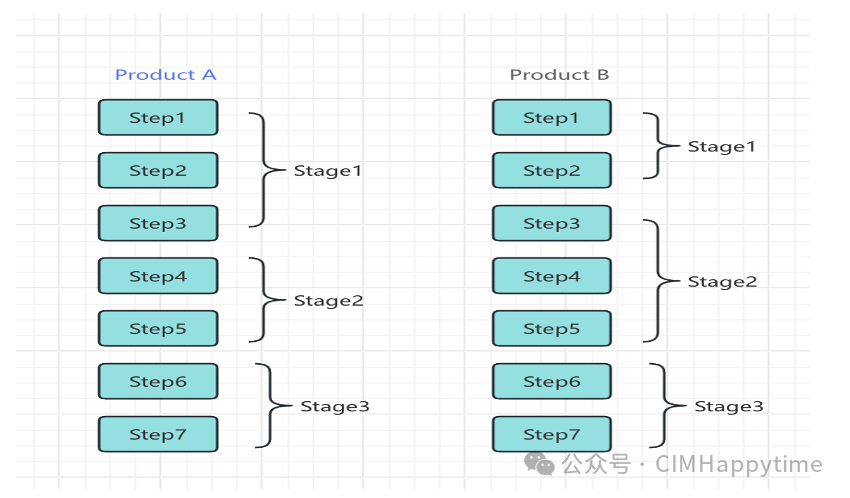

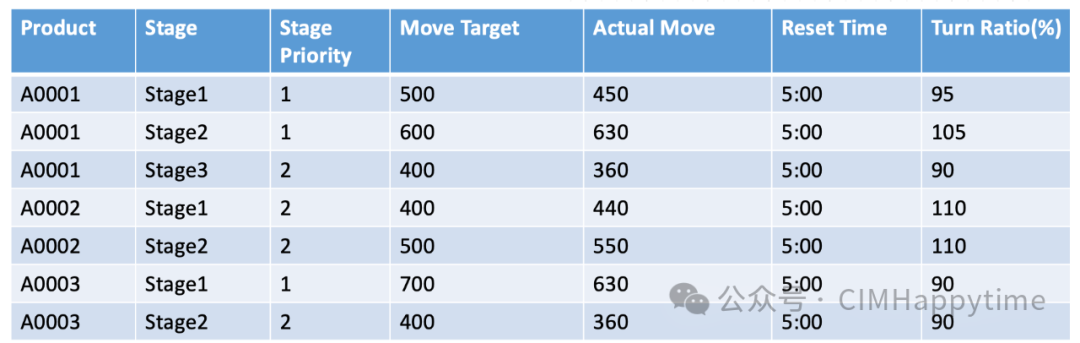

Product Process Stage Movement Drive

In addition to managing the progress of individual batches, the RTS solution also focuses on the overall flow speed of the production line at major process stages (Stage).

-

Concept: The system sets daily (or per shift/cycle) “Movement” targets for different product process stages (e.g., Pre-Poly, Poly, Post-Poly, Backend, Final, etc.). Movement may refer to the number of batches or wafers produced from that stage.

-

Goal: By setting clear stage output targets and adjusting them based on actual production line conditions, the aim is to improve the “Stage Turn Ratio,” which is the speed at which batches pass through specific process stages (also known as WIP Velocity). This helps ensure that the production rhythm between different major areas of the factory remains coordinated and balanced, preventing excessive WIP accumulation in some stages while others are starved.

-

Implementation: The RTS system may use these Movement targets to adjust the priority of batches within different stages or influence resource allocation strategies (such as equipment, operators) to ensure that outputs from each stage can meet the set targets.

This management approach based on stage Movement targets provides the RTS system with a macro-level traffic control mechanism. It complements the micro-control based on batch priorities and bottleneck management. Focusing solely on local optimization (such as individual batches or bottlenecks) may lead to imbalances in the flow between different links in the factory. By setting and monitoring output speed targets for major process stages, RTS can better grasp overall production progress, ensuring that the entire value stream from wafer input to output is smoother and more balanced, thereby supporting the shortening of overall cycle times and the stability of output.

Proactive Pull and Acceleration Mechanisms

To further enhance efficiency and synchronization, the RTS solution also includes some proactive pull and acceleration mechanisms.

-

Key Step / Following WIP Pre-scheduling: The system identifies key steps (Key Steps) in the process and proactively schedules (pre-schedules) the upstream work-in-process (Following WIP) required for these key steps. This means the system predicts when materials will be needed for Key Steps and triggers upstream processes to start processing the corresponding batches in advance, ensuring that materials arrive on time and preventing Key Steps from waiting due to material shortages. This is a typical pull logic aimed at ensuring the continuous operation of critical resources. It aligns with input control strategies like CONWIP and the concept of managing WIP flow to support downstream demand, requiring accurate understanding of inter-process dependencies and timing.

-

Interval Acceleration Rules: Under specific conditions, the system applies rules to accelerate the flow of certain batches. For example:

- Future Merge: Accelerating those batches that are about to merge with other batches. Merging typically occurs in steps requiring batch processing or joint processing. The system needs to have foresight to anticipate future merging events and pull related batches in advance. (Note: This discussion pertains to traffic control and is unrelated to this).

- Diffusion Push Wet Lot: Actively “pushing” batches that have completed wet cleaning to the diffusion process. This is often because diffusion furnaces are batch processing equipment and may be bottlenecks, and they typically require specific wet cleaning steps before processing. Pulling in advance can ensure that the diffusion furnace has sufficient, compliant batches for batching, reducing waiting times.

- Cross-Area Linkage: The system coordinates the production rhythm between different process areas (especially those with strong dependencies, such as lithography-etching, wet-diffusion). For example, batches completed in lithography need to be sent to etching as soon as possible, and batches processed in wet treatment should be promptly sent to diffusion. Through linked scheduling, it can ensure that downstream areas receive batches completed upstream in a timely manner while avoiding upstream areas from halting due to downstream blockages. There are often time constraints (Timelinks) between process steps that need precise coordination.

These mechanisms (Key Step pull, interval acceleration, cross-area linkage) together form the strategy combination of the RTS system to proactively synchronize production processes. They go beyond simple passive dispatching by utilizing foresight information and understanding of process dependencies to proactively predict demand, coordinate activities, reduce waiting, eliminate bottlenecks, and accelerate flow, ultimately achieving smoother and faster overall output. In the complex semiconductor manufacturing environment characterized by re-entrant flows and tightly coupled processes, this proactive, cross-area coordination is crucial for enhancing overall efficiency.

The Role of Advanced Manufacturing Automation (AMA) and the MOM Extension Platform (MEP)

The effective operation of the advanced RTS solution relies on a robust automation foundation and integrated platform support.

AMA in Semiconductor Manufacturing

Modern wafer fabs, especially those of 300mm and above, have achieved a high level of automation (Advanced Manufacturing Automation, AMA). Automation covers various aspects, including material handling (such as using AMHS/OHT overhead crane systems), equipment control (through Equipment Automation Programs, EAP), process control (APC), and data collection. Automation is a key factor in ensuring efficiency, stability, and quality in semiconductor manufacturing.

MEP as an Integration Hub

In the RTS solution, the MOM Extension Platform (MEP) plays a central role as an integration hub. MOM (Manufacturing Operations Management) systems typically encompass functions such as MES, scheduling, and quality management. MEP, as an extension of MOM, is primarily responsible for connecting the RTS scheduling engine with other factory automation and information systems, such as MES, EAP, databases, and material control systems (MCS). It handles and forwards the real-time data streams required for RTS decision-making (such as WIP status, equipment status, process parameters, Q-Time data, priority instructions, etc.) and ensures that RTS scheduling instructions can be accurately and timely communicated to execution systems.

Utilizing Apache Camel and EIP

The MEP platform is built on the open-source integration framework Apache Camel. Apache Camel is a powerful, rule-based routing and mediation engine that provides a rich set of components for connecting various transport protocols and data formats, implementing numerous well-known Enterprise Integration Patterns (EIPs).

EIPs are standardized patterns and best practices defined by Gregor Hohpe and Bobby Woolf in their classic work, used to solve common integration problems. Camel greatly simplifies the development of complex integration scenarios by providing direct implementations of these patterns. Some examples of EIPs that may be used in MEP include:

- Content-Based Router: Routes messages to different destinations (such as different MES functions or device interfaces) based on message content (such as batch priority, target device).

- Message Translator: Transforms data formats between different systems (such as converting RTS scheduling instructions into a format recognizable by MES).

- Splitter / Aggregator: Processes batch messages or merges multiple messages.

MEP utilizes Camel’s components and EIP capabilities to achieve its core functions:

- Connectivity: Connects heterogeneous systems such as RTS, MES, equipment, and databases.

- Routing: Intelligently routes data and commands based on RTS instructions and factory events.

- Transformation: Handles data format differences between different systems.

- Execution Interface Logic: MEP is not just a data mover; it can also execute interface logic. This means that the Camel routes within MEP can include business logic, such as generating specific instructions to send to MES based on RTS-calculated priorities and Q-Time status; or triggering RTS to recalculate upon receiving equipment status change events. This capability makes MEP an active coordinator rather than just a simple message-passing middleware. Extended MOM platforms or ESBs (Enterprise Service Buses) typically possess this capability for execution logic.

It can be said that without a powerful and flexible integration platform like MEP, the complex scheduling logic designed for the RTS system would be difficult to implement and execute effectively. Apache Camel and its implemented EIPs provide standardized, reusable solutions to address the complex real-time communication and coordination needs among heterogeneous systems in semiconductor fabs, significantly reducing integration difficulty and improving system reliability and maintainability. By executing interface logic, MEP transforms the “intelligence” of RTS into executable “actions” for automation systems, serving as a critical bridge connecting scheduling decisions with physical execution.

Application Scenarios Supported by MEP in Combination with RTS Strategies

The mentioned MEP supports several specific application scenarios, which likely represent pre-configured integration processes or patterns in MEP (based on Apache Camel) for executing specific RTS strategies.

<span>Fixed Buffer / Internal Buffer:</span>: These scenarios are likely directly related to WIP management and buffer strategies in RTS. They may implement the following logic:

- Monitoring the WIP count in specific areas or equipment groups (e.g., before bottleneck equipment) and comparing it with the “standard WIP level” or target buffer size set by RTS.

- Triggering corresponding actions, such as pausing upstream production (Hold Release) or requesting accelerated material delivery when WIP counts reach upper or lower limits.

- Executing RTS’s management logic regarding differentiated buffer capacities for bottlenecks and non-bottlenecks.

(Note: This discussion pertains to general software buffers, not specifically to these MEP scenarios. It mentions limited internal buffers for cluster tools).

<span>Trigger Scenario:</span>This is a general, event-driven execution mechanism. It can be used by RTS to implement various scheduling strategies that need to be triggered based on specific events, such as:

- Key Step/Following WIP Pull: When RTS determines that a Key Step is about to require materials, it sends pull instructions to upstream stations through the MEP trigger scenario.

- Cross-Area Linkage: When a batch completes in a certain area (such as lithography), it triggers preparation work or priority adjustments in downstream areas (such as etching).

- Q-Time Warning/Processing: When a batch’s Q-Time Ratio reaches Level 2 or Level 1, it triggers high-priority instructions or hold instructions to be sent to MES.

- Equipment Status Response: When critical equipment fails or recovers, it triggers RTS to reassess the plan and sends updated instructions through MEP.

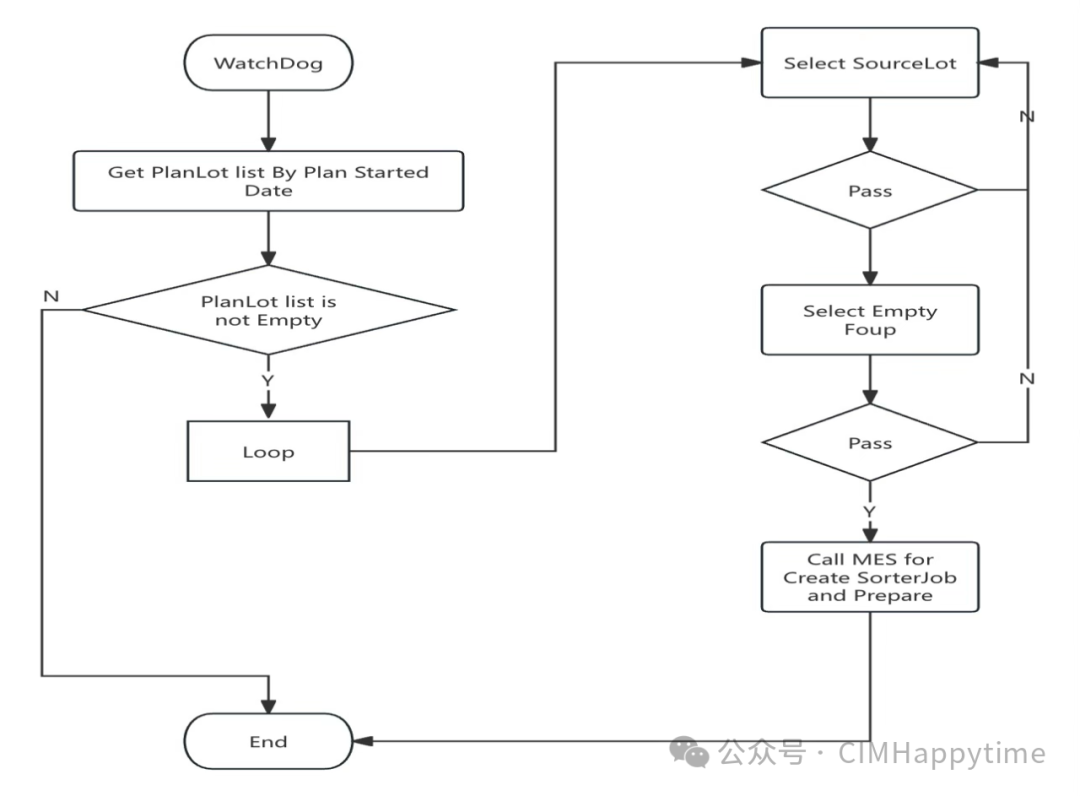

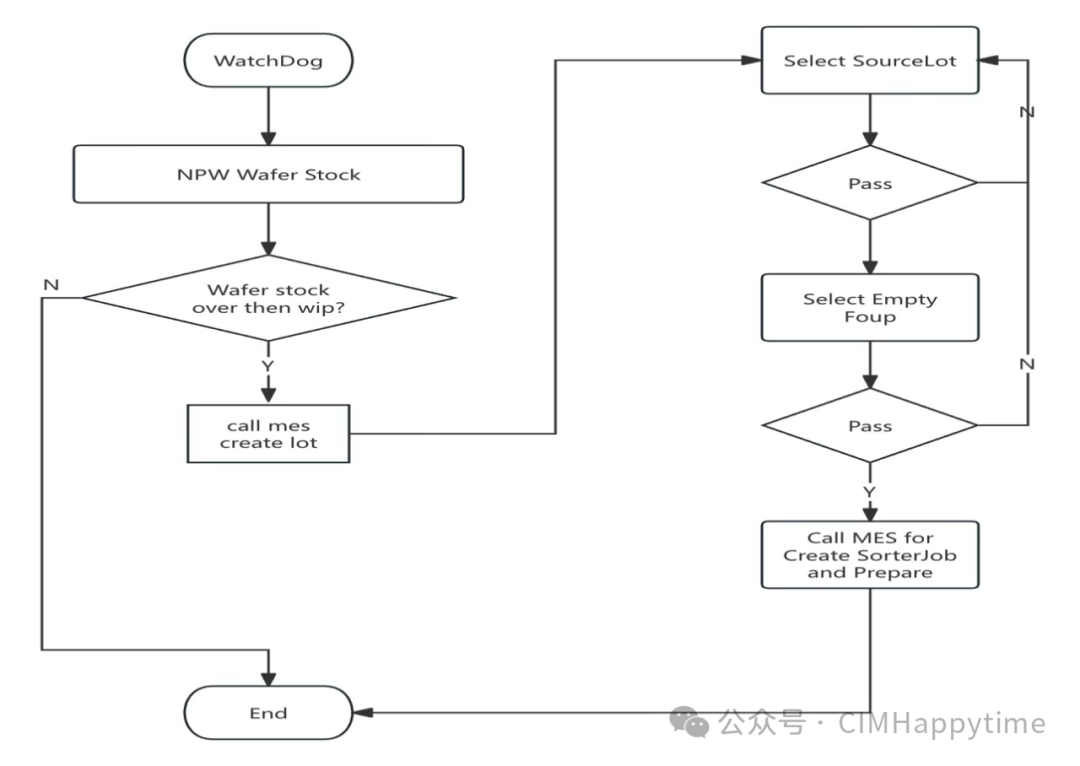

<span>Wafer Start Scenario:</span>: This scenario is specifically used to manage the actions of introducing new wafer batches into the production line. It may implement RTS’s input release control logic, such as:

- Deciding whether to allow new batches to start production based on the current overall WIP level, especially the WIP status in bottleneck areas (related to Standard WIP Level or CONWIP strategies).

- Adjusting the input release rate based on RTS’s predictions of future capacity and demand.

- Ensuring that newly introduced batches align with the overall production plan and delivery targets.

These MEP application scenarios translate RTS strategies and decisions into specific actions that automation systems can understand and execute. For example, when RTS calculates a new bottleneck area WIP target, the Fixed/Internal Buffer scenario in MEP is responsible for monitoring and executing the corresponding input control; when RTS identifies a batch that needs to be pulled for a Key Step, the Trigger Scenario in MEP is responsible for sending specific pull requests to relevant systems. Therefore, these scenarios are not abstract concepts but executable components of RTS strategies within the automation framework, forming a bridge connecting high-level scheduling logic with the underlying physical operations of the factory.

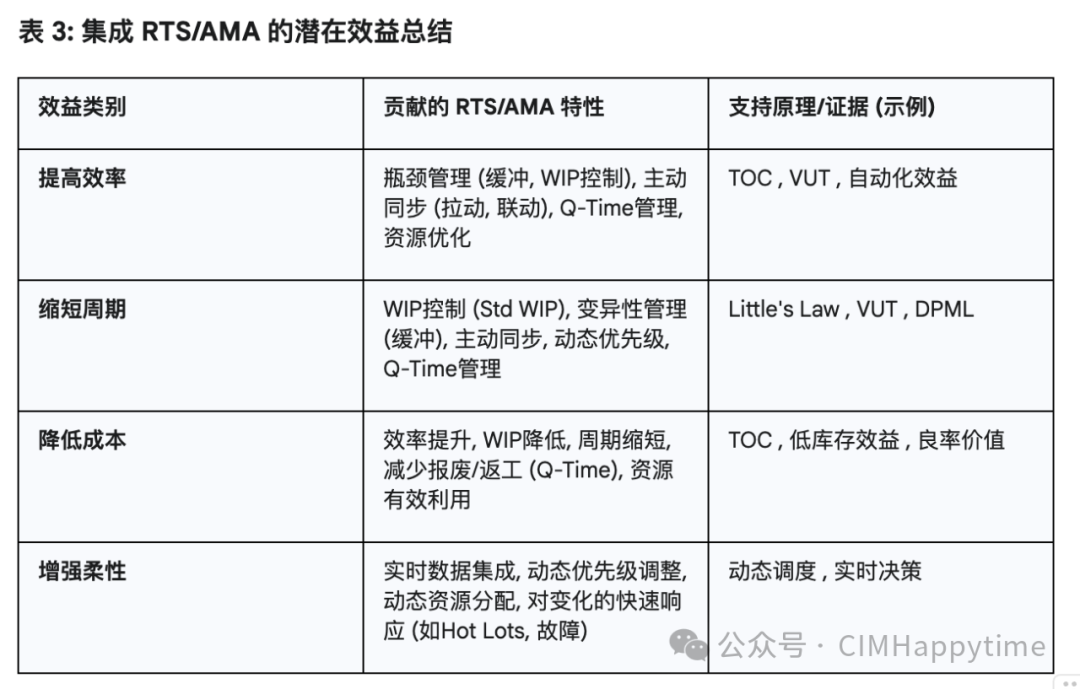

Potential Benefits of Integrated RTS/AMA Solutions

Combining advanced RTS solutions with a robust AMA/MEP integration platform is expected to bring significant operational benefits to semiconductor manufacturing fabs.

Improving Production Efficiency:

- Mechanism: Through TOC-based bottleneck optimization (such as reserved buffer capacity, standard WIP level control), ensure that the overall output capacity of the factory is maximized. By employing proactive synchronization mechanisms like Key Step pull and cross-area linkage, reduce idle waiting times for equipment. Effective Q-Time management minimizes rework and scrap due to quality issues, thereby increasing effective output. While not pursuing maximum non-bottleneck utilization, overall resource utilization efficiency is optimized.

- Support: TOC applications aim to enhance throughput. Automation and intelligent scheduling can improve productivity. Effective scheduling is key to enhancing efficiency.

Shortening Production Cycles:

- Mechanism: Little’s Law indicates that lowering WIP levels (through Standard WIP Level control) can directly shorten average cycle times. Variability management guided by VUT principles (such as reserved buffers) helps reduce queue times, a major component of cycle time. Proactive synchronization mechanisms (like Key Step pull) eliminate unnecessary waiting in the process. Dynamic priority adjustments based on flow timetables can accelerate lagging batches, enabling them to complete faster.

- Support: Controlling WIP is key to shortening lead times. Reducing variability can shorten cycle times. Effective scheduling helps lower cycle times. DPML is an important metric for measuring cycle time progress, and its improvement is one of the goals of scheduling optimization.

Reducing Production Costs:

- Mechanism: Improved production efficiency means lower fixed costs per unit (such as equipment depreciation). Lower WIP levels reduce inventory holding costs and capital occupation. Shorter cycle times may lower operating costs (such as energy consumption). By maximizing Q-Time management to minimize scrap and rework, direct savings on materials and reprocessing costs are achieved. More effective resource utilization also means cost savings.

- Support: TOC helps improve financial performance. Low inventory reduces costs. Efficiency improvements lead to cost reductions. Avoiding yield losses (such as those caused by Q-Time violations) can significantly save costs.

Enhancing Production Flexibility:

- Mechanism: The integration of real-time data and dynamic adjustment capabilities enables the production system to respond more quickly and effectively to various changes and uncertainties, such as urgent orders (Hot Lots), sudden equipment failures, and demand fluctuations. The system can dynamically reallocate priorities and resources based on flow timetables and Q-Time status.

- Support: Automation and real-time decision-making enhance the system’s responsiveness. Dynamic scheduling is designed to address uncertainty.

These benefits do not exist in isolation but are the result of mutual promotion and synergy. For example, improving efficiency through bottleneck management (TOC) increases throughput while controlling WIP (Standard WIP Level) shortens cycle times (Little’s Law). Shorter cycle times and less scrap (Q-Time management) directly reduce production costs. The real-time control capabilities of the entire system supported by RTS/AMA provide the flexibility to respond to disturbances, thus maintaining high efficiency and meeting delivery requirements in a dynamically changing environment. The overall benefits brought by this integration exceed the simple sum of individual functions.

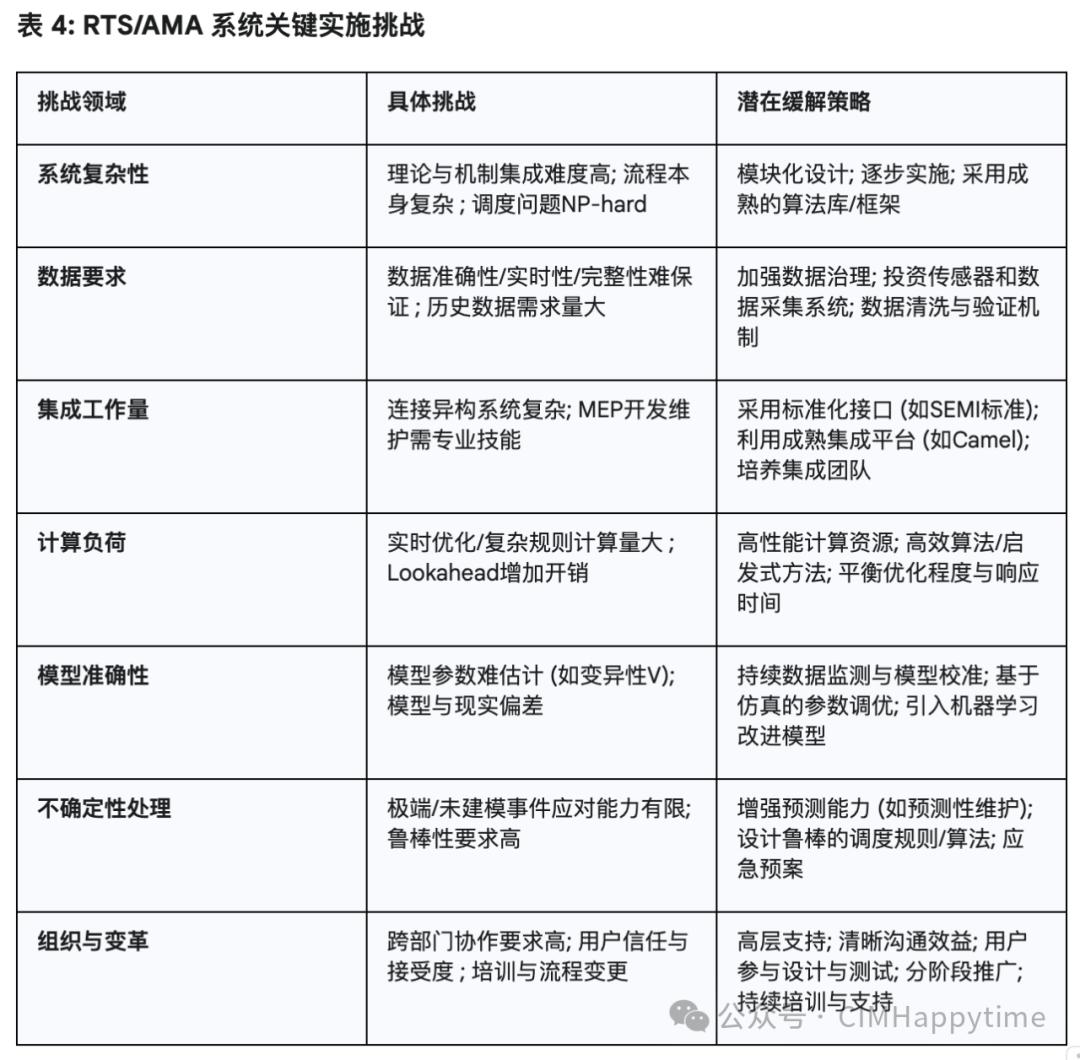

Implementation Challenges, Complexities, and Constraints

Despite the promising prospects of integrated RTS/AMA solutions, implementing such advanced systems in actual semiconductor fabs faces numerous challenges and complexities.

System Complexity:

- Integrating various management theories (TOC, Little’s Law, VUT) and complex scheduling mechanisms (priority logic, Q-Time processing, buffer strategies, pull rules, etc.) into a coordinated and stable operating system presents a high level of technical complexity.

- The inherent complexity of semiconductor manufacturing processes (re-entrant flows, hundreds or thousands of steps, mixed batch and single wafer processing, sequence-related setup times, etc.) makes scheduling problems NP-hard, placing high demands on the design and implementation of scheduling algorithms.

Data Requirements:

- The effective operation of RTS heavily relies on high-quality, timely data inputs, including accurate equipment status, WIP location and status information, reliable process time (RPT) and waiting time (WT) estimates, accurate definitions of Q-Time constraints, and tracking of remaining time. Ensuring the accuracy, completeness, and timeliness of data in actual production environments is a significant challenge.

- The initialization of the system, parameter calibration (such as standard WIP levels, buffer sizes, priority weights), and potential training of machine learning models require a large amount of accurate historical production data. The workload for data collection, cleaning, and management is substantial.

Integration Workload (AMA/MEP):

- Seamlessly integrating RTS with numerous existing systems in the factory (MES, EAP, AMHS, databases, etc.) through MEP is a large and complex project. It requires addressing differences in interfaces, protocols, and data formats among different systems.

- Developing, testing, and maintaining Camel routes and EIP configurations in MEP requires specialized technical knowledge and ongoing investment. Ensuring the stable and reliable operation of the integration platform is crucial; any failure in the integration process may lead to the failure of the scheduling system.

Computational Load:

- For large wafer fabs, executing real-time optimization calculations or evaluating complex scheduling rules may generate a significant computational load. Especially when RTS needs to perform pre-scheduling or simulation over extended time windows, a trade-off must be made between the quality of the scheduling solution (close to optimal) and the computational response time (fast enough to respond to real-time changes). This often requires powerful computing hardware and efficient algorithm support.

Model Accuracy and Tuning:

- The effectiveness of RTS decisions depends on the accuracy of its internal models, such as estimates of process times, waiting times, equipment efficiency, and the variability factor V in the VUT equation. Deviations between the model and actual conditions can lead to poor scheduling outcomes.

- There are numerous parameters in the system that require careful setting and continuous tuning, such as specific buffer sizes, thresholds for standard WIP levels, weights for various priority calculations, and benchmarks for flow timetables. This often requires repeated experimentation and validation using simulation tools, which is a time-consuming process requiring expertise.

Handling Uncertainty and Variability:

- Although RTS aims to better manage variability, the system’s ability to respond to extreme events beyond expectations (such as prolonged unexpected downtimes, raw material supply interruptions, sudden market demand changes, etc.) or sources of variability not adequately captured by the model remains limited. The robustness of the system is a key indicator of its performance in uncertain environments. Introducing predictive maintenance and other technologies can help reduce unexpected downtimes but cannot completely eliminate all uncertainties.

Organizational and Change Management:

- Successfully implementing advanced RTS/AMA systems is not just a technical issue; it requires close collaboration across departments (production, engineering, IT) and support from senior management.

- On-site operators and engineers need to adapt to new workflows and trust the scheduling instructions provided by the automation system. This involves extensive training, communication, and cultural shifts. Resistance to change or lack of confidence in the system can hinder project success.

Successfully implementing RTS/AMA systems heavily relies on a tightly coupled “data-model-computation” triad. Accurate, real-time data is the foundation for driving complex models that represent factory physical laws and constraints (based on OR theory and specific rules), which need to run timely on a robust computing platform to produce effective scheduling decisions. Any shortcoming in this chain—whether in data accuracy, model distortion, or computational lag—can severely impact the performance and reliability of the entire system.

Achieving Global Optimization and Intelligent Scheduling

The described RTS combined with AMA solution aims to elevate semiconductor manufacturing production scheduling from traditional, localized, reactive management methods to a new level of global, predictive, and intelligent management by integrating various theories, strategies, and technical tools.

The core of this system lies in its integrative nature:

- Theoretical Integration: It does not rely on a single theory but organically combines classical operational management theories such as TOC, queueing theory (VUT equation), and process analysis (Little’s Law) to provide a solid scientific foundation for scheduling decisions.

- Strategic Integration: The system integrates various specific scheduling strategies, including TOC-based bottleneck management, dynamic priority adjustments based on flow timetables and Q-Time, macro flow rate control based on stage targets, and proactive pull and cross-area coordination mechanisms. These strategies complement each other and work together on complex production processes.

- Technical Integration: Advanced RTS algorithm logic is closely integrated with robust AMA infrastructure (including MEP integration platform, Apache Camel/EIP technology). The algorithms are responsible for “thinking” (making decisions), while the automation platform is responsible for “executing” (transmitting information, driving equipment and materials).

This high level of integration enables the system to transcend local optimization and achieve global optimization. Traditional RTD often focuses only on single points or small areas of efficiency, while RTS seeks to find optimal or near-optimal solutions at the system level within a given time window by pre-scheduling, considering global constraints (such as bottlenecks, Q-Time, cross-area dependencies), and optimizing objectives (such as meeting delivery dates, maximizing overall efficiency).

Furthermore, this system embodies the concept of smart manufacturing. It utilizes real-time data to perceive factory status, analyzes and judges based on built-in models and rules, automatically makes complex scheduling decisions, and executes these decisions through automation systems, forming a closed loop of perception-decision-execution. MEP, as the platform for execution logic, enables the system not only to transmit information but also to proactively coordinate and manage complex interactive processes. This adaptive adjustment capability based on data and models is an important step toward higher levels of manufacturing intelligence.

On a deeper level, this RTS/AMA system can be viewed as a paradigm for implementing the principles of operations research (OR) in cyber-physical systems (CPS). OR provides the theoretical tools for optimizing production systems (TOC, queueing theory, Little’s Law, etc.). The RTS algorithms translate these theories into dynamic decision logic (priority rules, buffer logic, Q-Time processing, etc.). The AMA/MEP layer builds the bridge connecting the digital world (algorithms, models, data) with the physical world (equipment, materials, sensors, actuators). Through this cyber-physical closed loop, the optimization ideas of OR can be applied and continuously adjusted in the complex and variable real manufacturing environment, transforming theoretical optimization potential into actual production benefits.

Industry Background and Future Trends

In the fiercely competitive semiconductor industry, advanced production scheduling systems are key elements in maintaining competitiveness.

- Existence of Similar Solutions: There are indeed various advanced scheduling solutions in the industry, including products offered by commercial software vendors (such as the mentioned commercial solutions and Applied Materials’ RTD/AutoSched products) and proprietary systems developed internally by large semiconductor manufacturers.

- Actual Application Effects and Challenges: Theoretically, advanced RTS systems can bring significant benefits. However, the actual successful deployment often requires overcoming numerous challenges. The degree of benefit realization largely depends on the quality of implementation, the degree of integration with existing systems, the accuracy of data, and ongoing maintenance and optimization investments. Successful cases often demonstrate efficiency improvements, cycle time reductions, etc., but this is not achieved overnight.

- Industry Development Trends: The semiconductor manufacturing scheduling field is undergoing continuous technological evolution:

- From Rules to Optimization: More and more systems are shifting from relying on simple dispatching rules to adopting more complex mathematical programming or heuristic optimization algorithms to seek better scheduling solutions.

- Application of AI/ML: Artificial intelligence and machine learning technologies are increasingly being explored and applied in the scheduling field, such as discovering more effective dynamic dispatching rules by learning from historical data; predicting equipment failures or maintenance needs and incorporating this information into scheduling considerations; more accurately predicting batch cycle times; and assisting in optimizing scheduling parameters.

- Digital Twin: Building virtual replicas of factories (digital twins) has become an important trend. Digital twins can be used for offline simulation, testing, and validating new scheduling strategies or parameter settings without risking actual production lines. They can accelerate the development and optimization process of scheduling solutions.

- Integration and Data Platforms: As system complexity increases, the demand for powerful, flexible integration platforms (like MEP) and high-quality real-time data is also growing to support more complex real-time decision-making and control.

For RTS/AMA systems, while already quite advanced, they are more like a position in a continuously evolving technological spectrum. The semiconductor industry is moving toward more data-driven, predictive, and adaptive intelligent scheduling and control systems. In the future, we can expect to see deeper integration of emerging technologies like AI/ML and digital twins with RTS/AMA systems to address the challenges posed by increasing factory complexity, product diversity, and market dynamics.