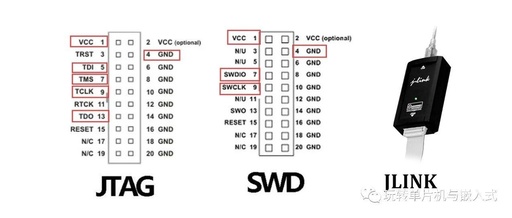

Comparison of Embedded Debug Interfaces JTAG and SWD

Developing and debugging embedded systems is a complex task that requires powerful tools and interfaces to ensure the correctness of hardware and software. In this field, JTAG (Joint Test Action Group) and SWD (Serial Wire Debug) are two commonly used debugging interface standards that play a crucial role in embedded system development. This article will … Read more