Introduction: Makefile scripting language greatly enhances productivity, allowing us to focus more on the design itself. This article introduces the Makefile scripts for commonly used VCS and Verdi software in IC design/verification, along with the source code, hoping to be of help to everyone. If you don’t have the relevant operating environment, try replying hidden benefits in the background!

This article is from Zhihu user Trustintruth, and the article links are https://zhuanlan.zhihu.com/p/105165439 and https://zhuanlan.zhihu.com/p/105863018

VCS

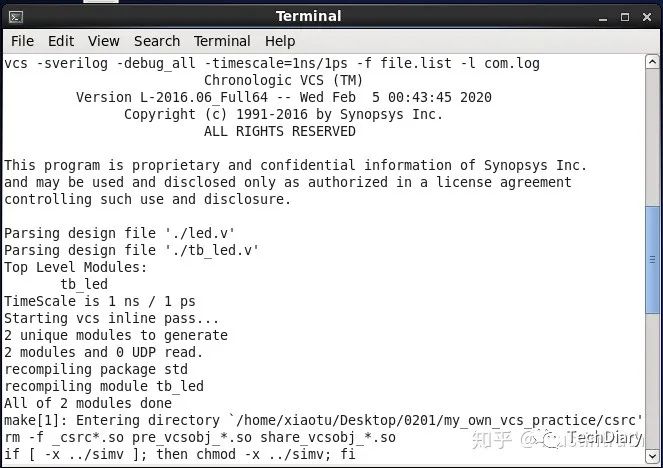

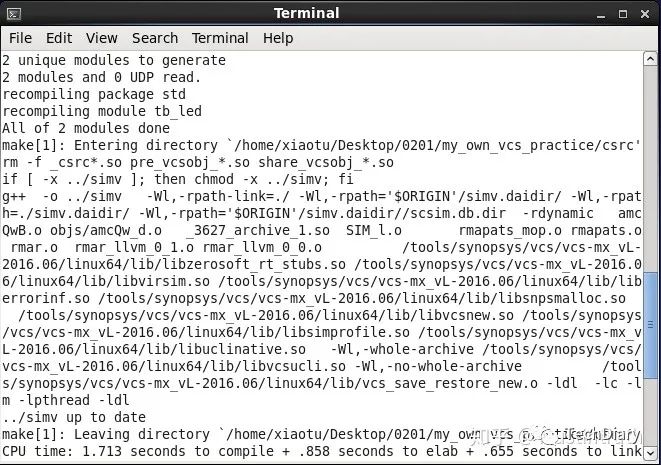

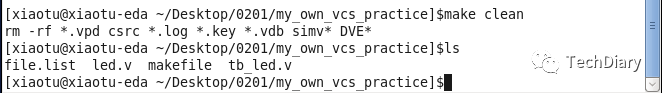

First, navigate to the path of your personal directory where the .v files are located. Compile the .v design files and tb files by entering the following command in the terminal:

vcs -sverilog -debug_all -timescale1ns/1ps led.v tb_led.v -l com.logThis compiles the source code RTL and testbench. Here, led.v is the design file, and tb_led is the test file.

After running, you can use the ls command to see the executable file simv in the directory.

Next, enter the command to run the simulation:

./simv -l sim.log

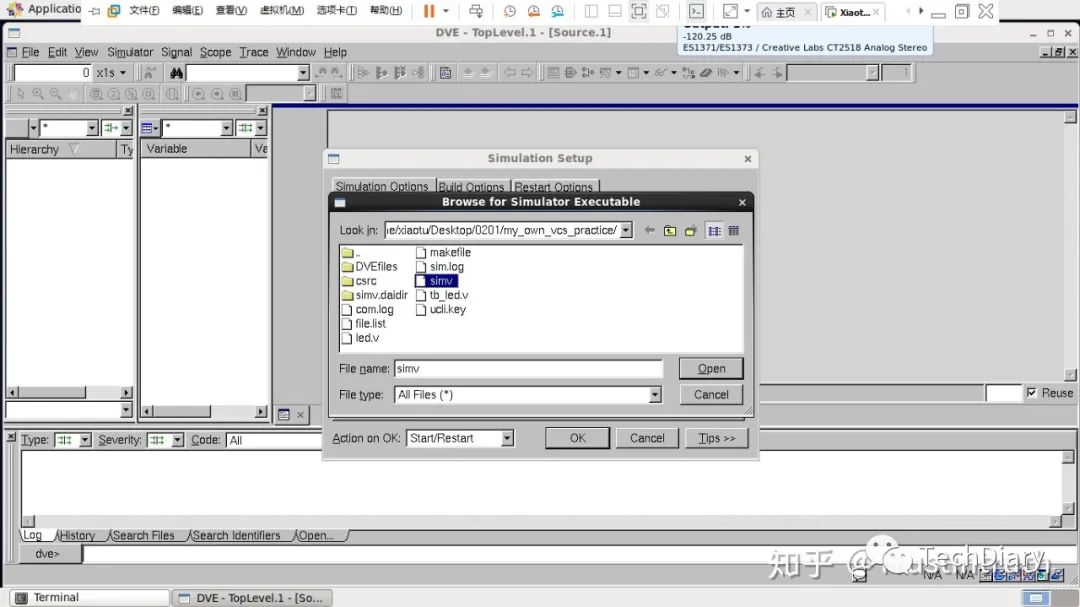

Finally, view the waveform in dve:

dve -vpd vcdplus.vpd &The & symbol indicates to run in the background. This opens the dve interface, where you can select simv for setup and run in the graphical interface.

However, this process is too complex, so we choose to use Makefile. The make commands we need to execute include:

-

make all to perform all the above operations -

make com to compile -

make sim to run sim -

make run_dve to open DVE -

make clean to delete intermediate simulation files

In the terminal, under the directory with the Makefile, simply enter the above make commands to complete the operations.

Before that, we first generate a file.list with the paths of the .v and tb files by entering the following command in the terminal:

find -name "*.v" > file.listOpen file.list to see the following structure:

Then, use gvim to create the makefile:

all: com sim run_dve

com: vcs -sverilog -debug_all -timescale1ns/1ps led.v tb_led.v -l com.log

sim: ./simv -l sim.log

run_dve: dve -vpd vcdplus.vpd &

clean: rm -rf *.log csrc simv* *.key *.vpd DVEfile coverage *.vdbAfter saving, enter make all in the terminal to perform the above operations, which will yield the same results as before. Finally, after completion, you can use make clean to remove the files generated during the simulation, and you can use ls to check if they are cleared.

Verdi

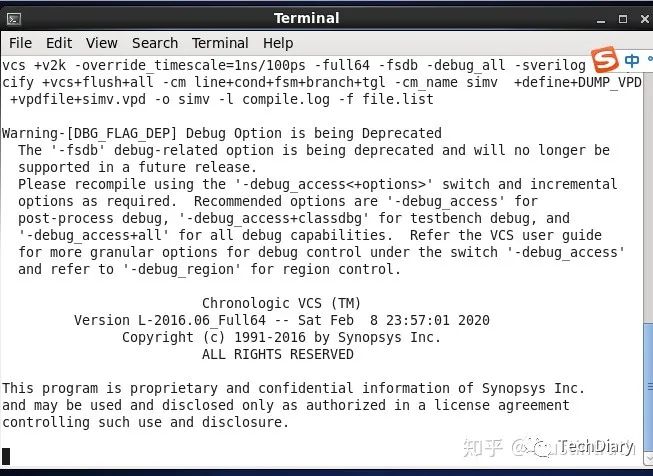

If we want to use Verdi instead of VCS, how do we call it? Similar to before, we also need to put the paths of our .v files and tb files into file_list.f (last time it was file.list), then write the makefile, and once it’s set up, we can use the make command to complete it.

The makefile is as follows:

.PHONY: com sim cov clean debug

OUTPUT = simv

ALL_DEFINE = +define+DUMP_VPD

# Code coverage command

CM = -cm line+cond+fsm+branch+tgl

CM_NAME = -cm_name $(OUTPUT)

CN_DIR = -cm_dir ./$(OUTPUT).vdb

# vpd file name

VPD_NAME = +vpdfile+$(OUTPUT).vpd

# Compile command

VCS = vcs +v2k -timescale=1ns/1ns

# simulation command

SIM = ./$(OUTPUT) +ntb_ramdom_seend_automatic $(CM) $(CM_NAME) $(CM_DIR) $(VPD_NAME) $(ALL_DEFINE) -l $(OUTPUT).log

# start compile

com: $(VCS) -f file_list.f

# Start simulation

sim: $(SIM)

# show the coverage

cov: dve -covdir *vdb &

debug: dve -vpd $(OUTPUT).vpd &

# start clean

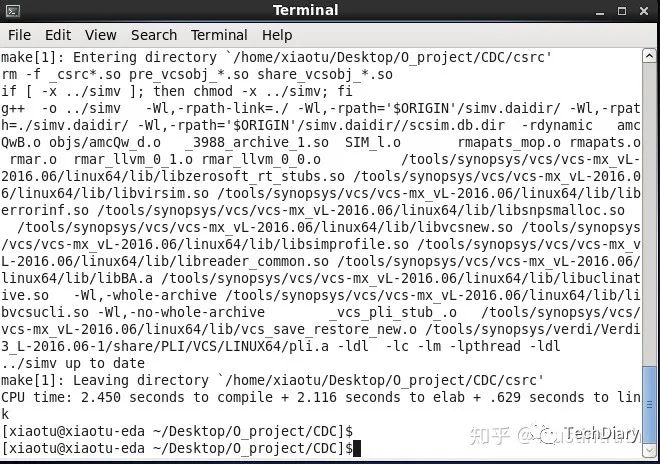

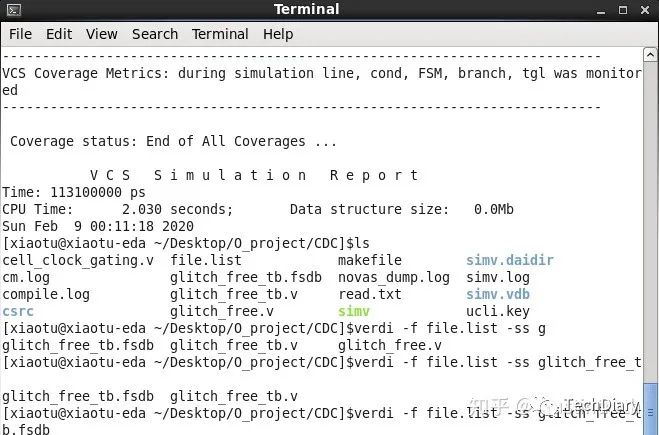

clean: rm -rf ./csrc *.daidir ./csrc *.log *.vpd *.vdb simv* *.key +race.out* novas* verdi* *fsdb apb2apb_asyncAfter saving, first run make com

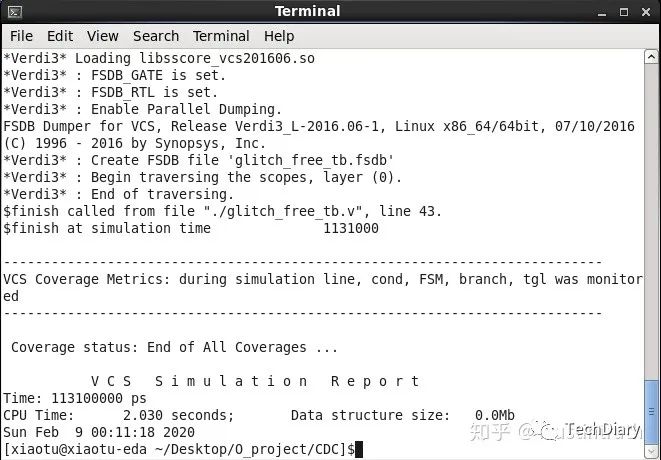

Then run make sim

Then run make sim

Next, use ls to check, and you will find a .fsdb file in the path (I named it glitch_free_tb.fsdb in the makefile, which can be changed if needed). Enter the command:

verdi -f file_list.f -ss glitch_free_tb.fsdb

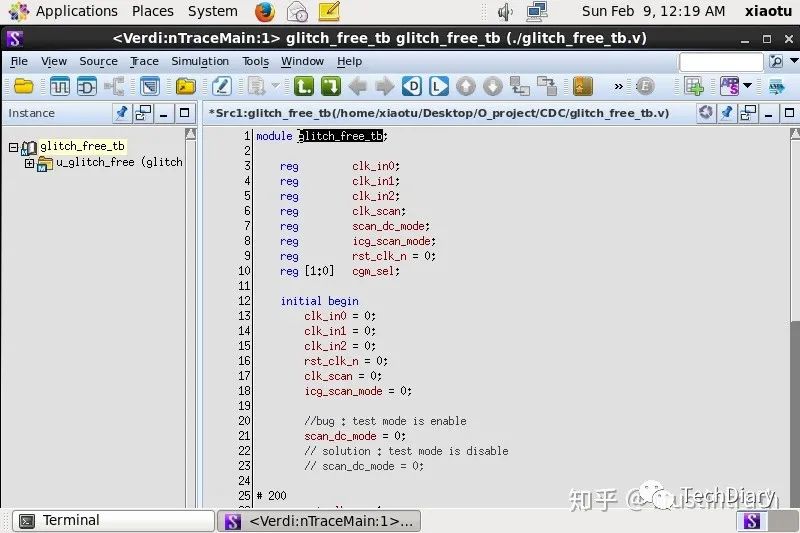

During the operation, I changed the file.list, and according to the makefile created in the article, follow the commands above, do not follow the instructions in the image. Then enter the interface:

Minimize the interface to operate:

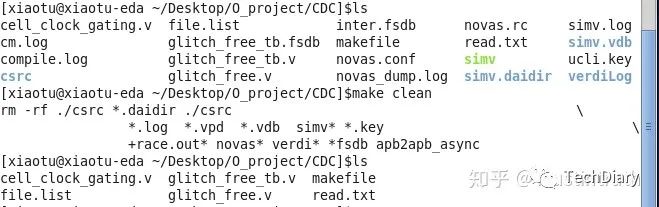

If you need to delete intermediate files, enter make clean

end

Light up  , let everyone know you are watching

, let everyone know you are watching