Click aboveLinux Community to follow us

Abstract: This article mainly introduces makefile, a commonly used tool language for GNU GCC compilation. LiteOS also uses this file to build project files and generate executable files.

In the LiteOS source code, makefile is used for batch processing compilation and linking to generate files. When designing a project using LiteOS with the GNU compiler, makefile is generally used for compiling and linking the program. If using Keil or IAR compilers, you can set the compiler information and file path in Keil IDE or IAR IDE to compile, link, and output files.

1. Introduction to Makefile

Simply put, makefile is the file executed by make, and the process of turning code into executable files is called compilation. The compilation of a series of files is called building. Make is a build tool provided by GNU, mainly used for the build compilation process of C and C++ projects. To learn to use Make, we need to learn to write makefile. This file describes how to compile and link several C source files and header files. When explicitly required, makefile can also tell make how to run other commands (e.g., deleting certain files as a cleanup operation).

1.1 Makefile Rules

A simple makefile consists of rules in the following format:

target … : prerequisites …

recipe

…

…target is usually the name of the file generated by the program. Examples of targets include executable files or object files. Targets can also be the name of operations to be executed, such as “clean”;

prerequisites are files used as input to create the target. A target usually depends on several files;

recipe is an action to be executed. Recipes may have multiple commands on the same line or on their own lines. Note: You need to add a tab at the beginning of each recipe line! This is a common point of confusion. If you want to use characters other than tabs as prefixes in the recipe, you can set the .RECIPEPREFIX variable to other characters.

The “target” is required and cannot be omitted; both “prerequisites” and “recipe” are optional, but at least one of the two must exist.

A rule explains how and when to remake certain files as specific rule targets. Make executes methods based on the prerequisites to create or update the target. Rules can also explain how and when to perform an operation. A makefile may contain other text besides rules, but a simple makefile only needs to contain rules. Rules may seem more complex than shown in this example, but all rules fit this pattern more or less.

1.2 Makefile Syntax

① # indicates comments

② Wildcards are used to specify a group of matching filenames. The wildcards in Makefile are consistent with Bash, mainly including asterisk (*), question mark (?), and […]. For example, *.o indicates all files with the .o suffix.

③ % pattern matching

For compiling the files a.c and b.c in the current directory, the original writing is:

a.o: a.c

b.c: b.cUsing % can be simplified to:

%.o : %.cThis allows for simplification when processing a large number of similar files.

④ “=” to define custom variables

txt = Hello World

test:

@echo $(txt)Here, txt replaces “Hello World”.

Additionally, based on “=”, Makefile provides four assignment operators: (=, :=, ?=, +=).

⑤ Built-in variables

Make has its own operational variables, which refer to some of its own functional commands, such as: $(CC) points to the currently used compiler, $(MAKE) points to the currently used Make tool.

For specific variable rules, refer to: https://www.gnu.org/software/make/manual/html_node/Implicit-Variables.html

⑥ Automatic Variables

Makefile provides some variables related to rules, commonly used include:

(1) $@ —– refers to the current target

(2) $< —– refers to the first prerequisite

a.txt: b.txt c.txt

cp $< $@The above code is equivalent to the following code:

a.txt: b.txt c.txt

cp b.txt a.txt$< refers to the first prerequisite, which is “b.txt”; $@ refers to the target value, which is “a.txt”.

(3) $? —— refers to all prerequisites that are newer than the target, separated by spaces. For example, if the rule is t: p1 p2, where the timestamp of p2 is newer than t, $? refers to p2.

(4) $^ —— refers to all prerequisites, separated by spaces. For example, if the rule is t: p1 p2, then $^ refers to p1 p2.

(5) $* —— refers to the part matched by the % wildcard, for example, % matches f1.txt, $* represents f1.

(6) $(@D) and $(@F) —— refer to the directory name and file name of $@ respectively. For example, if $@ is src/input.c, then $(@D) would be src, and $(@F) would be input.c.

(7) $(<D) and $(<F) —— refer to the directory name and file name of $< respectively.

1.3 Makefile Loops

Makefile uses Bash syntax to complete conditions and loops.

For example, ifeq — else — endif usage:

ifeq ($(CC),gcc)

libs=$(libs_for_gcc)

else

libs=$(normal_libs)

endifThe above code determines different compilation paths based on whether the compiler is gcc.

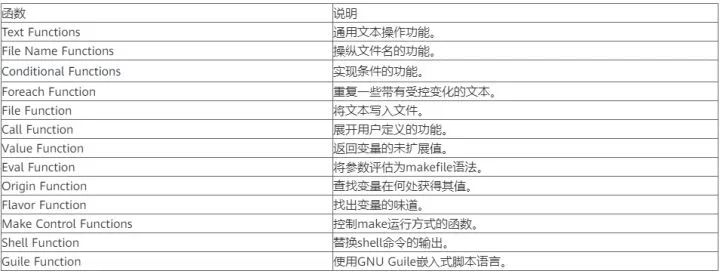

1.4 Makefile Functions

Makefile provides some built-in functions, used in the following format:

$(function arguments)

# or

${function arguments}The built-in functions are as follows: for specific functions refer to (https://www.gnu.org/software/make/manual/html_node/Functions.html)

2. Writing Makefile Files

The following file compiles a C language project, including three source files main.c, kbd.c, display.c, and two header files defs.h, command.h.

The compilation code is as follows:

edit : main.o kbd.o command.o display.o

cc -o edit main.o kbd.o command.o display.o

main.o : main.c defs.h

cc -c main.c

kbd.o : kbd.c defs.h command.h

cc -c kbd.c

command.o : command.c defs.h command.h

cc -c command.c

display.o : display.c defs.h

cc -c display.c

clean :

rm edit main.o kbd.o command.o display.o

.PHONY: edit cleanIn this code, the output files are cleared, and then the gcc compiler compiles the three header files and two files.

This article is shared from Huawei Cloud Community “Understanding Makefile in LiteOS (1) —- Introduction to Makefile”, original author: o0LongLong0o.

Follow Us

Long press or scan the QR code below to followLinux Community

Follow Linux Community, add “Star“

Get daily technical content, let us grow togetherContact WeChat: linuxgs