Debug Authentication

The debug authentication signals are used to control access to the debug components. For more information about these signals, refer to the Arm CoreSight Architecture Specification v3.0.

As shown in Figure 3 – 13 “Architectural View of RD – V2 DAP Structure on Page 39”, there are different debug domains within the compute subsystem:

·System Debug Domain: This domain includes system-level components such as the CMN – 700 interconnect and AXI – AP for accessing memory-mapped resources.

·Application Processor Core Debug Domain.

·SCP Core Debug Domain.

·MCP Core Debug Domain.

A different set of authentication signals provides debug authentication for each domain:

·System Debug Domain Components: SYSDBGEN, SYSNIDEN, SYSSPIDEN, SYSSPNIDEN

·Application Processor Core Debug Components, which are part of all debug domain chains: APPDBGEN, APPSPIDEN

·SCP Core Debug Domain Components: SCPDBGEN, SCPNIDEN, SCPSPIDEN, SCPSPNIDEN

·MCP Core Debug Domain Components: MCPDBGEN, MCPNIDEN, MCPSPIDEN, MCPSPNIDEN

Each domain enables both intrusive and non-intrusive debugging separately. Security and non-security debugging for each domain are also controlled separately.

The application processor core adopts the Armv8.5 debug architecture, where the NIDEN and SPNIDEN signals have been deprecated.

These signals are instantiated as inputs into the compute subsystem. The instantiation method of these signals is determined by the implementation. The System on Chip (SoC) implementation must ensure that these signals are controlled by a secure entity/trust root to prevent tampering. Alternatively, fuses implemented as part of the SoC can also be used to set these signals.

System Debug Support

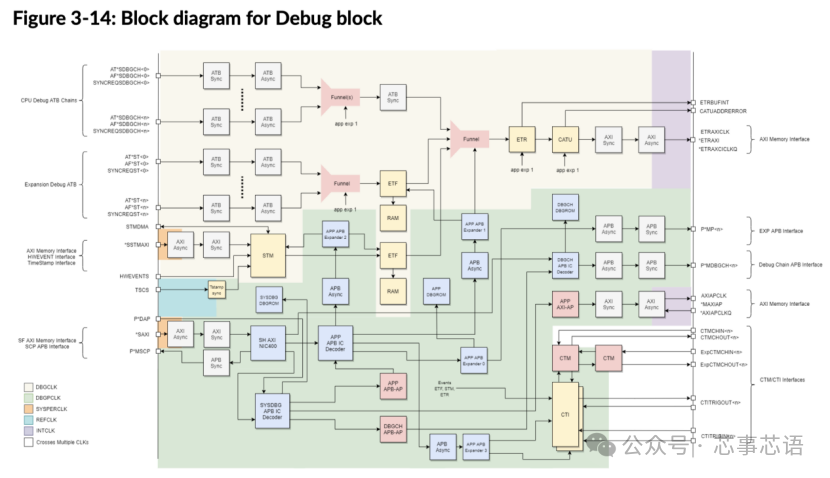

The system debug logic provides the following debug support:

·Logic to support daisy chaining of core debug logic interfaces (Debug APB, tracing, triggering, and timestamping) to support tile-based layout planning.

·A system trace macro unit (STM) that can generate trace data directly from AMBA AXI write transactions (in-band trace data) and hardware events (HWEVENT interface). The STM has its own dedicated 16KB memory for the STM first-in-first-out trace cache (ETF).

·A system trace aggregator that collects trace data from application processor cores, system control processors (SCP), main control processors (MCP), CMN, and STM in different daisy chains, aggregating this data into a 32KB system ETF memory.

·Routing of trace data to the main system memory via the Embedded Trace Router (ETR).

·A CoreSight Address Translation Unit (CATU) that provides address translation functionality on the AMBA AXI interface from the ETR.

·A debug APB network for programming debug peripherals.

·A dedicated debug access port (DAP) APB bus interface from external debuggers.

·A debug APB interface for accessing all cores in various debug chains as well as debug components in SCP and MCP modules.

·System-wide tracing and triggering components.

·All application processors, SCP, and MCP cores can be accessed for self-hosted software debugging.

·An AMBA AXI – AP that allows external debuggers to access the system memory backplane directly without going through the processor.

·Debug authentication for system debug components through input signals SYSDBGEN, SYSNIDEN, SYSSPIDEN, and SYSSPNIDEN.

·Cross-triggering between all components in the system via the Cross Trigger Interface (CTI) and Cross Trigger Matrix (CTM).

·Extended debug interfaces (Debug APB, extended tracing and triggering) for components added outside the compute subsystem, providing support for SoC.

·Support for fine-grained power requestor (GPR) functionality through GPR registers for SYSTOP power domain reset requests.

·Support for multi-chip debugging.