Click the blue text to follow us

1. Overview of Microcontroller Serial Expansion

The methods for implementing microcontroller serial expansion include commonly used serial bus standards such as: I2C bus, Serial Peripheral Interface (SPI), and Universal Serial Bus (USB). This chapter will focus on the I2C bus.

1. Implementation through dedicated serial standard bus

(1) Serial Peripheral Interface (SPI)

SPI (Serial Peripheral Interface) is a synchronous serial interface standard with a 3-wire structure, requiring only 4 lines to interface with various standard peripheral devices. It uses full-duplex 3-wire synchronous data transmission and supports a multi-master/slave structure.(2) Universal Serial Bus (USB)

① Simple wiring and ease of use.

② Transmission rates range from a few kbps to several Mbps, suitable for medium to low-speed device interfaces.

③ Strong error correction capabilities, resulting in high reliability.

(3) Access Bus

2. Implementation through serial communication port UART

3. Implementation through software simulation

2. I2C Bus

1. Structure and Signal of I2C Bus

(1) Structure of I2C Bus

(3) Status and Signals of I2C Bus

1) Bus Idle

Both SCL and SDA are in a high state, indicating that the bus is idle.

2) Bus Occupation and Release

If a device wants to use the bus, it must first occupy it. The master device occupying the bus sends clock signals on the SCL line. After data transmission is completed, the bus should be released promptly, restoring it to an idle state.

3) Clock Signal and Data Signal

Clock signals appear on the SCL line, while data signals are transmitted on the SDA line. Data is transmitted bit by bit, with one clock cycle transmitting one bit of data. A high level on the SDA line represents data bit 1, while a low level represents data bit 0. The relationship between the clock signal and data signal is: during the high level of the clock signal, the state of the data line must remain stable; only when the clock signal is low can the state of the data bit change. As shown in the figure below.

4) Start and Stop Signals

Start and stop signals can only be issued by the master device, corresponding to the high level of SCL and the transition on SDA. When the SCL line is high, the master device generates a negative level transition on the SDA line, indicating a start signal. When the SCL line is high, the master device generates a positive level transition on the SDA line, indicating a stop signal. After the stop signal appears, a certain time interval must be allowed before the bus can be considered released and return to an idle state.

Typically, the start signal is denoted by S, and the stop signal is denoted by P.

Additionally, during data transmission, a start signal may also occur, but this start signal is referred to as a repeated start signal, denoted by Sr, issued to initiate a new data transmission that differs from the previous one.

5) Acknowledge and Non-Acknowledge Signals

The acknowledge signal confirms the transmission of a byte of data, and after each byte of data transmission is completed, the receiving device should return an acknowledge signal.

The acknowledge signal and non-acknowledge signal correspond to the 9th clock pulse, where the SDA line remains high for a non-acknowledge signal. In practice, the acknowledge signal is represented by ACK (or A), while the non-acknowledge signal is represented by NACK (or NA).

6) Wait State

- In the I2C bus, the receiving device is granted the authority to put the system into a wait state, but this wait state can only occur after a complete data byte has been received.

- In the wait state, the sender cannot send data until the receiving device determines that it can continue receiving data, at which point it releases the SCL line, allowing the system to exit the wait state, and the sender can then continue sending data.

- The wait state is also known as the delay state, essentially changing the data transmission rate by extending the clock pulse cycle. The purpose of setting a wait state is twofold: to provide the receiving device with an opportunity to perform other operations, and to allow the system to connect devices with different speeds. Therefore, the I2C bus system does not impose speed requirements on connected devices.

2. Data Transmission Methods of I2C Bus

(1) Basic Data Transmission Format

Data transmission on the I2C bus occurs bit by bit, with the high bit first and the low bit second. Each time a data byte is transmitted, an acknowledge signal is used to confirm, and there is no limit to the number of bytes transmitted. The transmission format is shown in the figure below.

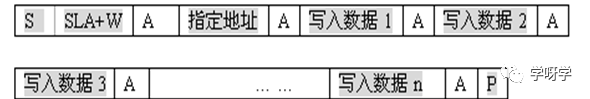

(2) Master Transmit Mode

Master transmit mode refers to the master device sending data to the controlled slave device. The data transmission format in master transmit mode is shown in the figure below.

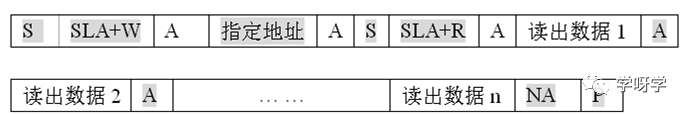

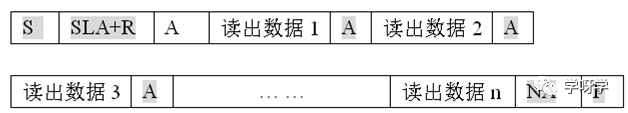

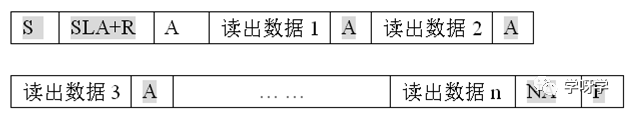

(3) Master Receive Mode

The master device receives data sent from the controlled slave device, which is referred to as master receive mode. Its data transmission format is shown in the figure below.

3. Device Addressing

(1) Device Classification

According to control relationships, there is a control and controlled relationship (or master-slave relationship) between devices. The controlling device is called the master device, while the controlled device is referred to as the slave device.

According to the data transmission relationship, there is a sending and receiving relationship between devices, where the device sending data is called the sender, and the device receiving data is called the receiver.

(2) Device Working Modes

Devices in the bus system have four working modes: master transmit mode (the device sends data as the master), master receive mode (the device receives data as the master), slave transmit mode (the device sends data as the slave), and slave receive mode (the device receives data as the slave).

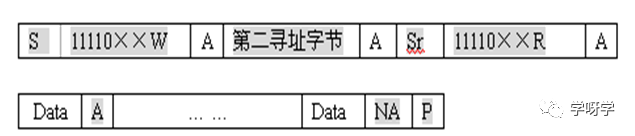

(3) In the I2C bus system, since there are no address lines available, addresses can only be transmitted via the serial line SDA. Users are concerned with device addressing, specifically how to locate the slave device.

1) Device Addressing

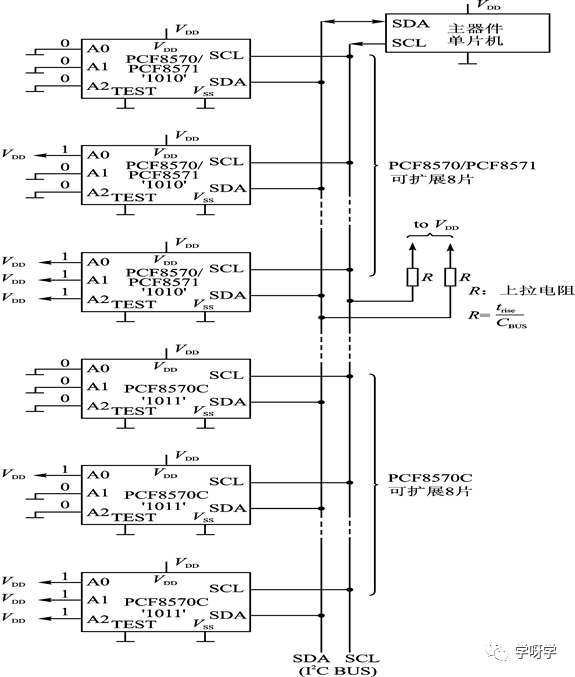

In the I2C bus, device addressing is also known as the slave address. After the I2C bus starts, the first byte sent by the master device is the addressing byte, denoted as SLA+R/W, where the first 7 bits of SLA represent the slave address. The I2C device addressing is uniformly allocated by the I2C bus committee and follows certain rules.

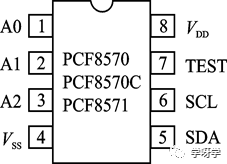

For example: PCF8574 (I2C bus to 8-bit parallel bus converter)

2) Pin Address

The bits A2A1A0, A1A0, and A0 in the addressing bits indicate that their corresponding bits’ encoding is obtained through external levels. These bits of device encoding are set through pins, hence referred to as pin addresses. The pin addresses of the chip are always arranged starting from the lowest bit.

3. I2C Bus of Microcontroller 8×C552

4. Serial Expansion of Microcontroller 8×C552

-

Specified Address Write

-

Specified Address Read

-

Current Address Read

Multi-chip data storage expansion in I2C bus system

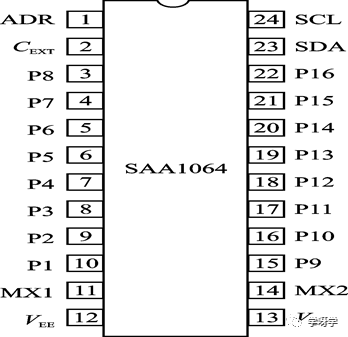

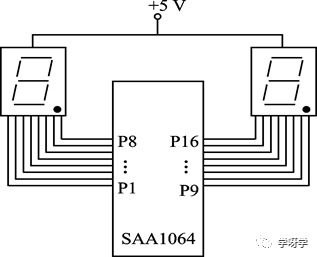

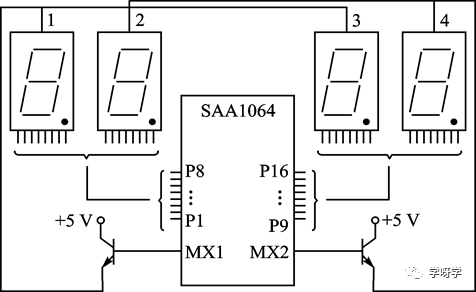

SAA1064 dynamic display mode interface connection

5. Serial Expansion of Microcontroller 80C51

1. Serial Program Memory Expansion via UART

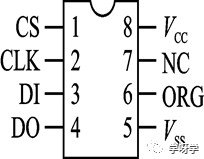

Serial program memory expansion typically uses serial EEPROM chips for electrically erasable programmable read-only memory. In such chips, some can be expanded via UART, such as the 93C46. The pin arrangement of this chip is shown in the figure below.

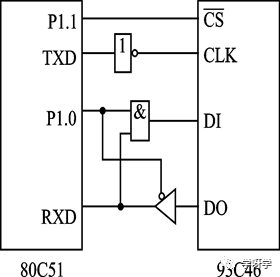

Connecting the serial memory expansion via the UART of the 80C51 is not complicated; for example, the connection of the 93C46 is shown in the figure below.

93C46 Chip Pin Arrangement

Connection of Serial Memory Expansion via UART

2. Software Simulation of Serial Interfaces

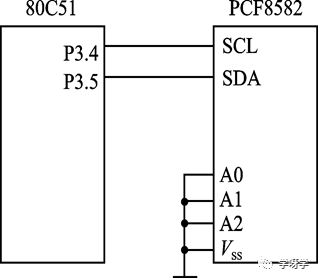

Serial interface functions can also be achieved through software simulation, i.e., using software-driven serial data transmission on parallel port lines, which is commonly used in simple systems without serial interfaces. Taking the serial interface of the 80C51 and PCF8582 as an example, we will illustrate the software simulation method for the I2C bus interface.

Using P3.4 and P3.5 of the 80C51 as the serial clock line SCL and serial data line SDA, the circuit connection is shown in the figure below.

In the 80C51 chip, since there are pull-up resistors within port P3, external pull-up resistors are not required. On the PCF8582 chip, A2, A1, A0 are grounded, which means the pin address is 000.

To start the I2C bus, both the SCL and SDA lines should be set high, and after a delay, the SDA line should be pulled low. The following sequences of instructions call or jump to the delay subroutine DELAY, which is merely to indicate that a time delay is required at that point.

SCL EQU 0B4H

SDA EQU 0B5H

SETB SCL

NOP

NOP

SETB SDA

ACALLDELAY

CLR SDA

PCF8582 has an I2C bus interface circuit that can detect the start signal on the bus and subsequently enter working state to receive the addressing byte sent by the 80C51.

In the I2C bus, data transmission occurs with the high bit first and the low bit second, hence the loop left shift instruction RLC is used to shift the data into the carry flag C first, followed by the bit transfer instruction to send it out. The two instructions are as follows:

RLC A

MOV SDA,C

After PCF8582 receives a byte of data, it should return an acknowledge signal. To receive the acknowledge signal from PCF8582, the simulation program of the 80C51 should release the SDA line to make it high. Additionally, the SCL line should be set high and then low to generate the 9th clock pulse. The sequence of instructions is as follows:

SETB SDA

ACALL DELAY

SETB SCL

ACALL DELAY

CLR SCL

If the operation is to read from PCF8582, after the 80C51 receives a byte of data, it sends an acknowledge signal to PCF8582 by pulling SDA low and generating the 9th clock pulse. The instruction sequence for this is as follows:

CLR SDA

ACALL DELAY

SETB SCL

ACALL DELAY

CLR SCL

The stop signal should be issued by the 80C51, as shown in the instruction sequence below:

CLR SDA

NOP

NOP

SETB SCL

ACALL DELAY

SETB SDA

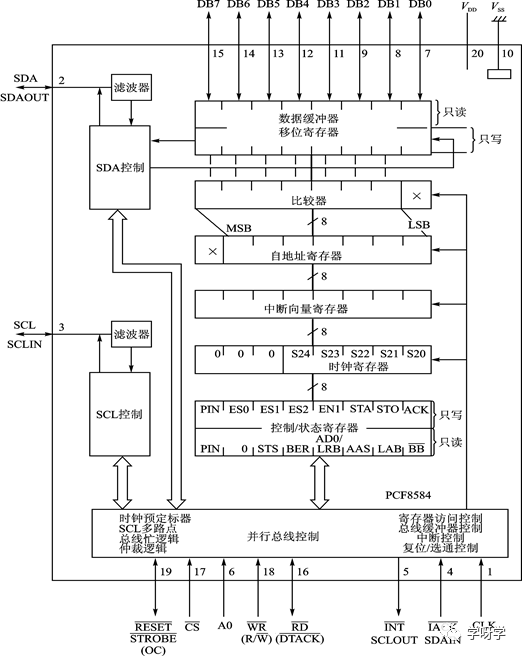

3. I2C Bus Interface Chip PCF8584

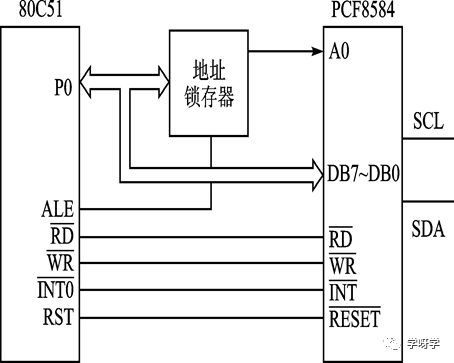

For microcontrollers like the 80C51 that lack an I2C bus interface, the I2C bus interface chip can be utilized to perform I2C bus operations. A typical I2C bus interface chip is the PCF8584, which primarily functions to convert from parallel bus to I2C bus.

(1) Logical Structure of PCF8584

Microcontrollers interfacing with PCF8584 can act as master devices in the I2C bus system, so the hardware structure of the PCF8584 chip is relatively complex. Its logical structure is shown in the figure below.

The conversion between parallel bus and I2C bus is achieved through a data register. The data register is a combination of a data buffer and a shift register, connecting to the parallel bus through the data buffer and to the I2C bus through the shift register. Both share a common address, thus referred to as the data register.

When the PCF8584 interface chip needs to send data to the I2C bus, the parallel data is directly written into the serial shift register, then shifted onto the SDA line. When receiving data, serial data is shifted from the SDA line into the shift register, and when the acknowledge signal appears, the data is copied from the shift register to the data buffer, then read into the CPU via the parallel bus.

The control register, status register, and self-address register are introduced below. The control and status registers share a common address and can be referred to as control/status registers.

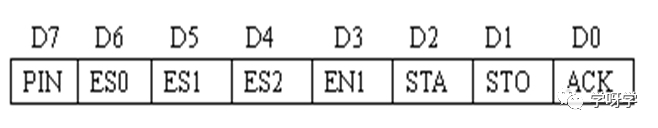

The control register is an 8-bit write-only register, with bit format and main control bit definitions as follows:

PIN——Interrupt control bit; ES2~ES0——Register selection bits;

ENI——Interrupt enable bit; STA——Start signal control bit;

STO——Stop signal control bit; ACK——Acknowledge signal control bit.

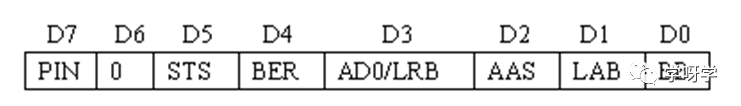

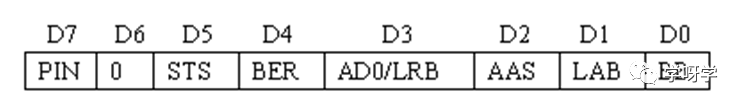

The status register is an 8-bit read-only register, with bit format and main control bit definitions as follows:

PIN——Interrupt control bit; STS——Stop status flag bit;

BER——Bus error flag bit; AD0——Zero address bit;

LRB——Last received flag bit; AAS——Slave device addressing bit;

LAB——Arbitration failure bit; BB——Bus busy flag bit.

The self-address register can also be referred to as the slave address register; it is also an 8-bit register (only using 7 bits) used to store the device code of this chip.

(2) Connecting 80C51 to I2C Bus via PCF8584

The main interface function of PCF8584 is to connect the microcontroller to the I2C bus system. Its connection with the 80C51 is shown in the figure below.

Connection of 80C51 with PCF8584

Long press the image to follow

Discover more exciting content

WeChat ID: Mechanical-knowledge