Introduction

Many engineers without formal education in computer science are actually not familiar with the compilation and linking of projects (including the author). However, if we want to create our own projects or implement a project from 0 to 1, or if we want to optimize programs, modify the memory layout, or implement memory protection under the AUTOSAR architecture, knowledge of compilation and linking is essential. With the goal of thoroughly understanding the subject, we decided to create a compilation environment based on the AUTOSAR architecture on the Windows operating system from 0 to 1. To enhance our coding skills, we will also implement a commonly used data structure library from 0 to 1. If there are excellent open-source AUTOSAR codes, we plan to incorporate them as well. We plan to manually write the entire project’s makefile so that we can directly compile the project using the make tool, while also writing CMakeLists files to support CMake in generating makefile files for compiling the entire project.

For those unfamiliar with the compilation toolchain, you can refer to this article: https://blog.51cto.com/xiacaojun/5648507

The tools we will use:

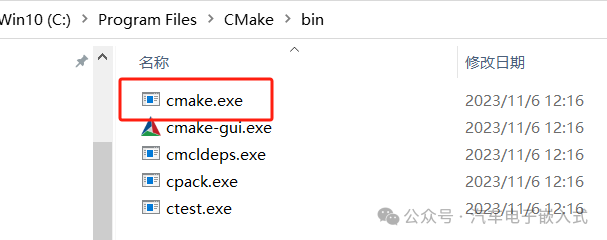

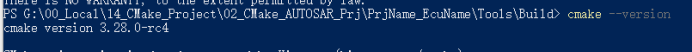

Project Build Generation Tool: CMake

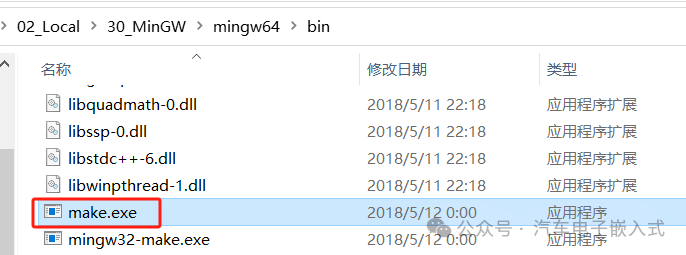

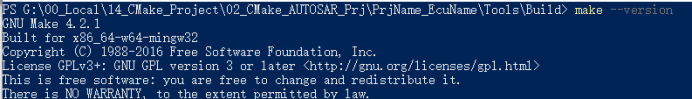

Project Build Tool: make

Compiler:

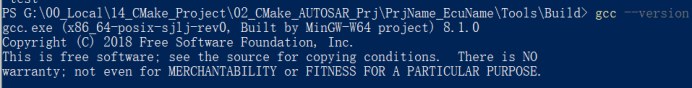

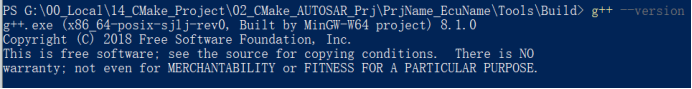

Windows: gcc/g++

TC3xx: Green Hills (GHS)

For an introduction to installing CMake on Windows, please refer to this article: Windows下CMake的小白级入门使用教程(hello world)

Special Articles:

Compilation and Linking Special Article Part 1 – Introduction to make and makefile

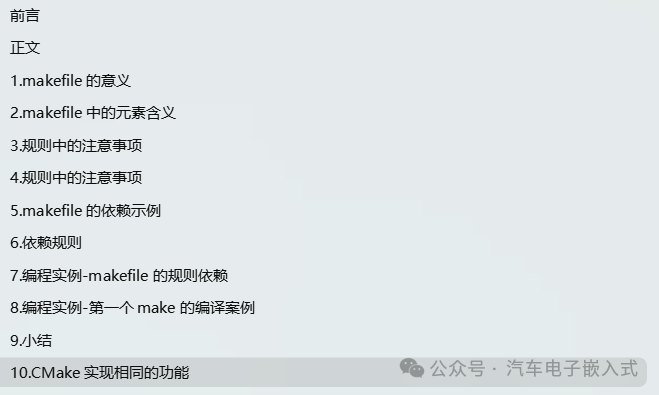

This article’s directory

Note: This article references some third-party tools and documents. If there is any infringement, please contact the author for deletion!

Main Text

1. The Significance of makefile

— makefile is used to define the dependencies between source files

— makefile specifies how to compile each source file and generate the executable file

The essence of a makefile is a script program, which needs to be interpreted and executed. Who interprets the makefile? — It is the make application.

Note:

1. Commands can be placed after dependencies or targets (placing them after the target implies no dependencies).

2. Dependencies can be omitted or absent, meaning that as long as the command is executed, the target can be completed.

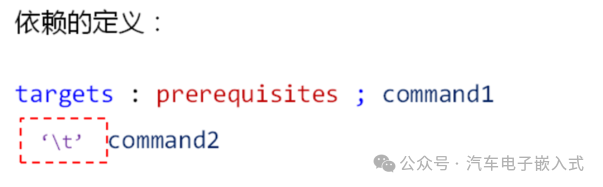

2. Elements of makefile

target

. Usually the name of the target file to be generated

. The name of the command that make needs to execute

prerequisites

. Other targets or files that the current target depends on

command

. The command that needs to be executed to complete the target

3. Notes on Rules

targets can contain multiple targets, separated by spaces.

prerequisites can contain multiple dependencies, separated by spaces.

4. Notes on Rules

[Tab] key:’ ’

. Each command line must start with a [Tab] character.

. [Tab] character tells make that this line is a command line.

Line continuation character: \